Go to the source code of this file.

Functions | |

| ABC_NAMESPACE_IMPL_START void | Amap_LibCollectFanins_rec (Amap_Lib_t *pLib, Amap_Nod_t *pNod, Vec_Int_t *vFanins) |

| DECLARATIONS ///. | |

| Vec_Int_t * | Amap_LibCollectFanins (Amap_Lib_t *pLib, Amap_Nod_t *pNod) |

| Vec_Int_t * | Amap_LibDeriveGatePerm_rec (Amap_Lib_t *pLib, Kit_DsdNtk_t *pNtk, int iLit, Amap_Nod_t *pNod) |

| unsigned * | Amap_LibVerifyPerm_rec (Amap_Lib_t *pLib, Amap_Nod_t *pNod, Vec_Ptr_t *vTtElems, Vec_Int_t *vTruth, int nWords, int *piInput) |

| void | Amap_LibVerifyPerm (Amap_Lib_t *pLib, Amap_Gat_t *pGate, Kit_DsdNtk_t *pNtk, Amap_Nod_t *pNod, int *pArray) |

| int | Amap_LibDeriveGatePerm (Amap_Lib_t *pLib, Amap_Gat_t *pGate, Kit_DsdNtk_t *pNtk, Amap_Nod_t *pNod, char *pArray) |

| DECLARATIONS ///. | |

| Vec_Int_t * Amap_LibCollectFanins | ( | Amap_Lib_t * | pLib, |

| Amap_Nod_t * | pNod ) |

Function*************************************************************

Synopsis [Collects fanins of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 77 of file amapPerm.c.

| ABC_NAMESPACE_IMPL_START void Amap_LibCollectFanins_rec | ( | Amap_Lib_t * | pLib, |

| Amap_Nod_t * | pNod, | ||

| Vec_Int_t * | vFanins ) |

DECLARATIONS ///.

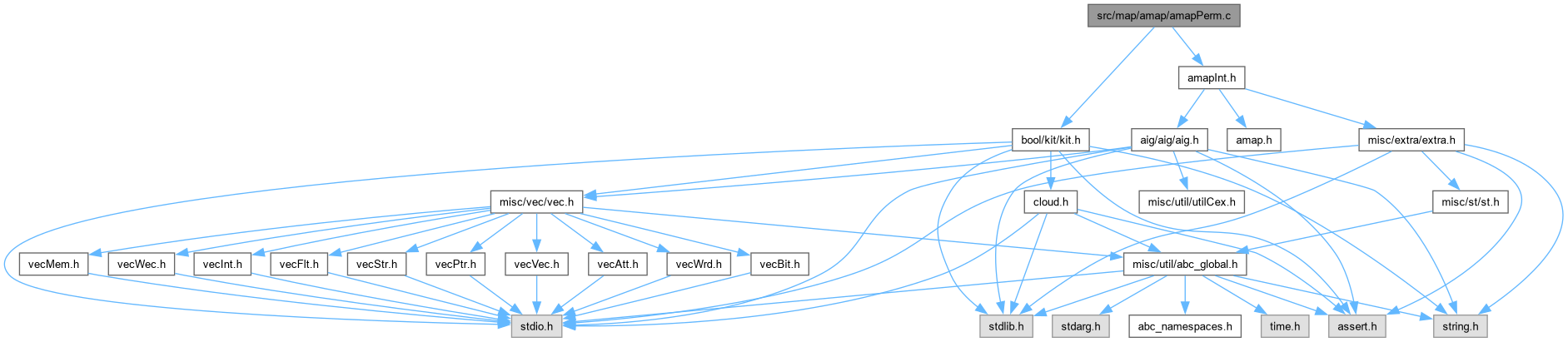

CFile****************************************************************

FileName [amapPerm.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Technology mapper for standard cells.]

Synopsis [Deriving permutation for the gate.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Collects fanins of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 46 of file amapPerm.c.

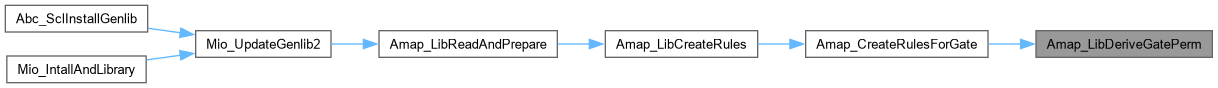

| int Amap_LibDeriveGatePerm | ( | Amap_Lib_t * | pLib, |

| Amap_Gat_t * | pGate, | ||

| Kit_DsdNtk_t * | pNtk, | ||

| Amap_Nod_t * | pNod, | ||

| char * | pArray ) |

DECLARATIONS ///.

Function*************************************************************

Synopsis [Matches the node with the DSD of a gate.]

Description []

SideEffects []

SeeAlso []

Definition at line 331 of file amapPerm.c.

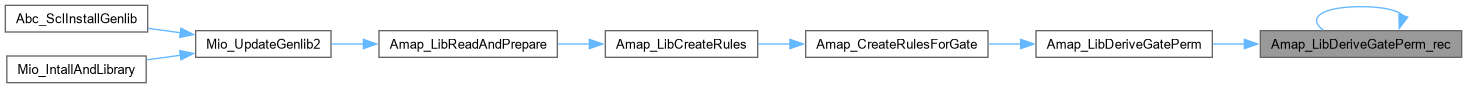

| Vec_Int_t * Amap_LibDeriveGatePerm_rec | ( | Amap_Lib_t * | pLib, |

| Kit_DsdNtk_t * | pNtk, | ||

| int | iLit, | ||

| Amap_Nod_t * | pNod ) |

Function*************************************************************

Synopsis [Matches the node with the DSD node.]

Description [Returns perm if the node can be matched.]

SideEffects []

SeeAlso []

Definition at line 95 of file amapPerm.c.

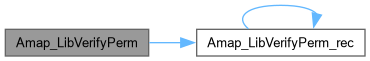

| void Amap_LibVerifyPerm | ( | Amap_Lib_t * | pLib, |

| Amap_Gat_t * | pGate, | ||

| Kit_DsdNtk_t * | pNtk, | ||

| Amap_Nod_t * | pNod, | ||

| int * | pArray ) |

Function*************************************************************

Synopsis [Performs verification of one gate and one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 280 of file amapPerm.c.

| unsigned * Amap_LibVerifyPerm_rec | ( | Amap_Lib_t * | pLib, |

| Amap_Nod_t * | pNod, | ||

| Vec_Ptr_t * | vTtElems, | ||

| Vec_Int_t * | vTruth, | ||

| int | nWords, | ||

| int * | piInput ) |

Function*************************************************************

Synopsis [Performs verification of one gate and one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 237 of file amapPerm.c.