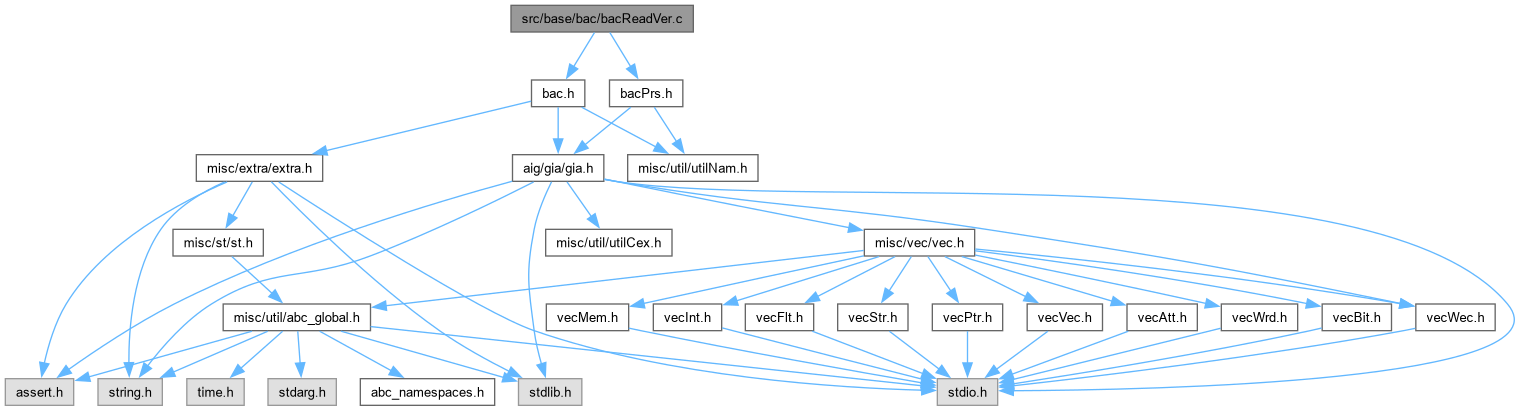

#include "bac.h"

#include "bacPrs.h"

Go to the source code of this file.

|

| enum | Bac_VerType_t {

PRS_VER_NONE = 0

, PRS_VER_INPUT

, PRS_VER_OUTPUT

, PRS_VER_INOUT

,

PRS_VER_WIRE

, PRS_VER_MODULE

, PRS_VER_ASSIGN

, PRS_VER_REG

,

PRS_VER_ALWAYS

, PRS_VER_DEFPARAM

, PRS_VER_BEGIN

, PRS_VER_END

,

PRS_VER_ENDMODULE

, PRS_VER_UNKNOWN

} |

| | DECLARATIONS ///. More...

|

| |

◆ Bac_VerType_t

DECLARATIONS ///.

CFile****************************************************************

FileName [bacReadVer.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Hierarchical word-level netlist.]

Synopsis [BLIF writer.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - November 29, 2014.]

Revision [

- Id

- bacReadVer.c,v 1.00 2014/11/29 00:00:00 alanmi Exp

]

| Enumerator |

|---|

| PRS_VER_NONE | |

| PRS_VER_INPUT | |

| PRS_VER_OUTPUT | |

| PRS_VER_INOUT | |

| PRS_VER_WIRE | |

| PRS_VER_MODULE | |

| PRS_VER_ASSIGN | |

| PRS_VER_REG | |

| PRS_VER_ALWAYS | |

| PRS_VER_DEFPARAM | |

| PRS_VER_BEGIN | |

| PRS_VER_END | |

| PRS_VER_ENDMODULE | |

| PRS_VER_UNKNOWN | |

Definition at line 31 of file bacReadVer.c.

31 {

Bac_VerType_t

DECLARATIONS ///.

◆ Psr_ManPrintModules()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 806 of file bacReadVer.c.

807{

808 char * pName; int i;

809 printf(

"Succeeded parsing %d models:\n", Vec_IntSize(&

p->vSucceeded) );

811 printf( " %s", pName );

812 printf( "\n" );

813 printf(

"Skipped %d known models:\n", Vec_IntSize(&

p->vKnown) );

815 printf( " %s", pName );

816 printf( "\n" );

817 printf(

"Skipped %d failed models:\n", Vec_IntSize(&

p->vFailed) );

819 printf( " %s", pName );

820 printf( "\n" );

821}

#define Psr_ManForEachNameVec(vVec, p, pName, i)

◆ Psr_ManReadSignalList()

| int Psr_ManReadSignalList |

( |

Psr_Man_t * | p, |

|

|

Vec_Int_t * | vTemp, |

|

|

char | LastSymb, |

|

|

int | fAddForm ) |

Definition at line 450 of file bacReadVer.c.

451{

452 Vec_IntClear( vTemp );

453 while ( 1 )

454 {

455 int Item = Psr_ManReadSignal(

p);

456 if ( Item == 0 )

return Psr_ManErrorSet(

p,

"Cannot read signal in the list.", 0);

457 if ( fAddForm )

458 Vec_IntPush( vTemp, 0 );

459 Vec_IntPush( vTemp, Item );

460 if ( Psr_ManIsChar(

p, LastSymb) )

break;

461 if ( !Psr_ManIsChar(

p,

',') )

return Psr_ManErrorSet(

p,

"Expecting comma in the list.", 0);

463 }

464 return 1;

465}

◆ Psr_ManReadVerilog()

| Vec_Ptr_t * Psr_ManReadVerilog |

( |

char * | pFileName | ) |

|

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 834 of file bacReadVer.c.

835{

839 return NULL;

840 Psr_NtkAddVerilogDirectives(

p );

841 Psr_ManReadDesign(

p );

842

843 if ( Psr_ManErrorPrint(

p) )

846 return vPrs;

847}

#define ABC_SWAP(Type, a, b)

struct Psr_Man_t_ Psr_Man_t

typedefABC_NAMESPACE_HEADER_START struct Vec_Ptr_t_ Vec_Ptr_t

INCLUDES ///.

◆ Psr_ManReadVerilogTest()

| void Psr_ManReadVerilogTest |

( |

char * | pFileName | ) |

|

Definition at line 849 of file bacReadVer.c.

850{

854

855

856 if ( !vPrs ) return;

857 printf( "Finished reading %d networks. ", Vec_PtrSize(vPrs) );

859 printf( "Memory = %.2f MB. ", 1.0*Psr_ManMemory(vPrs)/(1<<20) );

860 Abc_PrintTime( 1, "Time", Abc_Clock() - clk );

862

863

864

865 Psr_ManVecFree( vPrs );

866}

Vec_Ptr_t * Psr_ManReadVerilog(char *pFileName)

void Psr_ManWriteVerilog(char *pFileName, Vec_Ptr_t *p)

int Abc_NamObjNumMax(Abc_Nam_t *p)