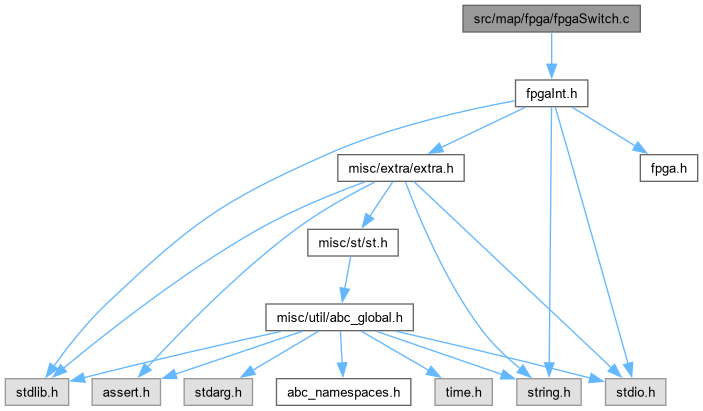

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

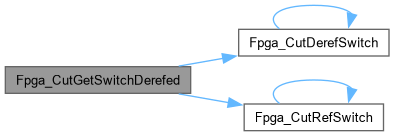

| ABC_NAMESPACE_IMPL_START float | Fpga_CutGetSwitchDerefed (Fpga_Man_t *pMan, Fpga_Node_t *pNode, Fpga_Cut_t *pCut) |

| DECLARATIONS ///. | |

| float | Fpga_CutRefSwitch (Fpga_Man_t *pMan, Fpga_Node_t *pNode, Fpga_Cut_t *pCut, int fFanouts) |

| float | Fpga_CutDerefSwitch (Fpga_Man_t *pMan, Fpga_Node_t *pNode, Fpga_Cut_t *pCut, int fFanouts) |

| float | Fpga_MappingGetSwitching (Fpga_Man_t *pMan, Fpga_NodeVec_t *vMapping) |

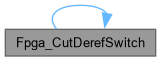

| float Fpga_CutDerefSwitch | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| Fpga_Cut_t * | pCut, | ||

| int | fFanouts ) |

function*************************************************************

synopsis [Dereferences the cut.]

description [This procedure is similar to the procedure NodeRecusiveDeref.]

sideeffects []

seealso []

Definition at line 95 of file fpgaSwitch.c.

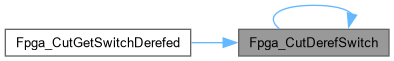

| ABC_NAMESPACE_IMPL_START float Fpga_CutGetSwitchDerefed | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| Fpga_Cut_t * | pCut ) |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaSwitch.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Generic technology mapping engine.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 8, 2003.]

Revision [

] FUNCTION DEFINITIONS /// function*************************************************************

synopsis [Computes the exact area associated with the cut.]

description []

sideeffects []

seealso []

Definition at line 43 of file fpgaSwitch.c.

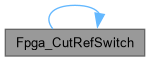

| float Fpga_CutRefSwitch | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| Fpga_Cut_t * | pCut, | ||

| int | fFanouts ) |

function*************************************************************

synopsis [References the cut.]

description [This procedure is similar to the procedure NodeReclaim.]

sideeffects []

seealso []

Definition at line 63 of file fpgaSwitch.c.

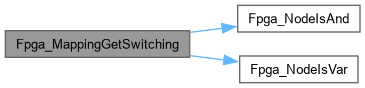

| float Fpga_MappingGetSwitching | ( | Fpga_Man_t * | pMan, |

| Fpga_NodeVec_t * | vMapping ) |

Function*************************************************************

Synopsis [Computes the array of mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 127 of file fpgaSwitch.c.