Go to the source code of this file.

Macros | |

| #define | FPGA_MAX_LUTSIZE 32 |

| INCLUDES ///. | |

| #define | Fpga_IsComplement(p) |

| GLOBAL VARIABLES ///. | |

| #define | Fpga_Regular(p) |

| #define | Fpga_Not(p) |

| #define | Fpga_NotCond(p, c) |

| #define | Fpga_Ref(p) |

| #define | Fpga_Deref(p) |

| #define | Fpga_RecursiveDeref(p, c) |

Typedefs | |

| typedef struct Fpga_ManStruct_t_ | Fpga_Man_t |

| STRUCTURE DEFINITIONS ///. | |

| typedef struct Fpga_NodeStruct_t_ | Fpga_Node_t |

| typedef struct Fpga_NodeVecStruct_t_ | Fpga_NodeVec_t |

| typedef struct Fpga_CutStruct_t_ | Fpga_Cut_t |

| typedef struct Fpga_LutLibStruct_t_ | Fpga_LutLib_t |

| #define Fpga_IsComplement | ( | p | ) |

| #define FPGA_MAX_LUTSIZE 32 |

INCLUDES ///.

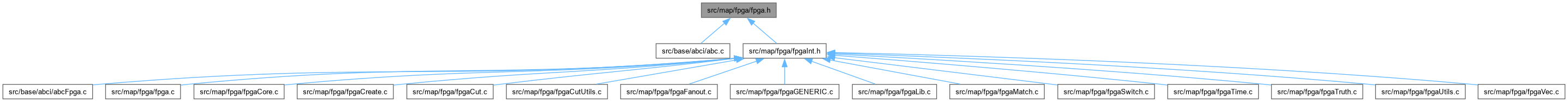

CFile****************************************************************

FileName [fpga.h]

PackageName [MVSIS 2.0: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] PARAMETERS ///

| #define Fpga_Not | ( | p | ) |

| #define Fpga_NotCond | ( | p, | |

| c ) |

| #define Fpga_Regular | ( | p | ) |

| typedef struct Fpga_CutStruct_t_ Fpga_Cut_t |

| typedef struct Fpga_LutLibStruct_t_ Fpga_LutLib_t |

| typedef struct Fpga_ManStruct_t_ Fpga_Man_t |

| typedef struct Fpga_NodeStruct_t_ Fpga_Node_t |

| typedef struct Fpga_NodeVecStruct_t_ Fpga_NodeVec_t |

|

extern |

Function*************************************************************

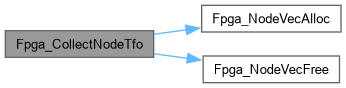

Synopsis [Collects the TFO of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 675 of file fpgaUtils.c.

|

extern |

|

extern |

Definition at line 142 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Reads parameters from the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 141 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Clean the signatures.]

Description []

SideEffects []

SeeAlso []

|

extern |

Function*************************************************************

Synopsis [Clean the signatures.]

Description []

SideEffects []

SeeAlso []

|

extern |

Function*************************************************************

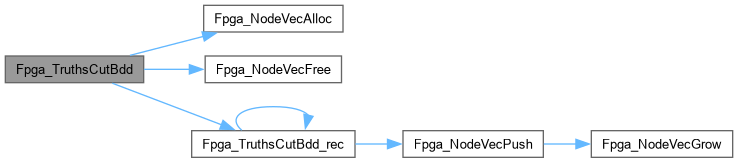

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 140 of file fpgaTruth.c.

|

extern |

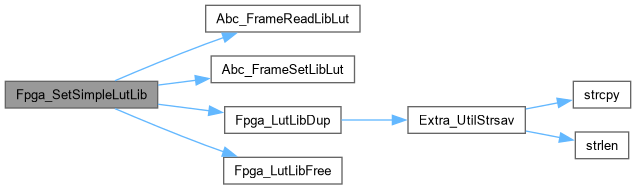

Function*************************************************************

Synopsis [Reads the parameters of the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 86 of file fpgaCreate.c.

|

extern |

Function*************************************************************

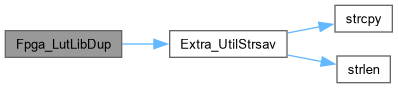

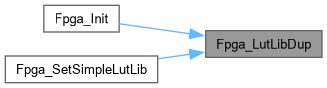

Synopsis [Duplicates the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 165 of file fpgaLib.c.

|

extern |

|

extern |

|

extern |

|

extern |

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaLib.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [APIs to access LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 43 of file fpgaLib.c.

|

extern |

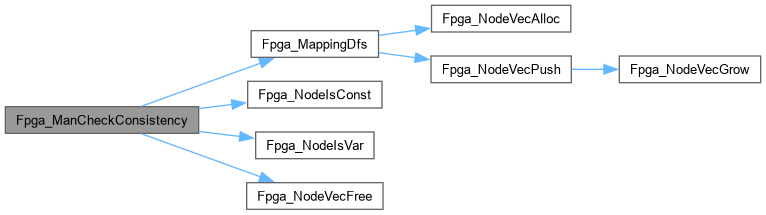

Function*************************************************************

Synopsis [Verify one useful property.]

Description [This procedure verifies one useful property. After the FRAIG construction with choice nodes is over, each primary node should have fanins that are primary nodes. The primary nodes is the one that does not have pNode->pRepr set to point to another node.]

SideEffects []

SeeAlso []

Definition at line 500 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Computes the limited DFS ordering for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 657 of file fpgaUtils.c.

|

extern |

FUNCTION DEFINITIONS ///.

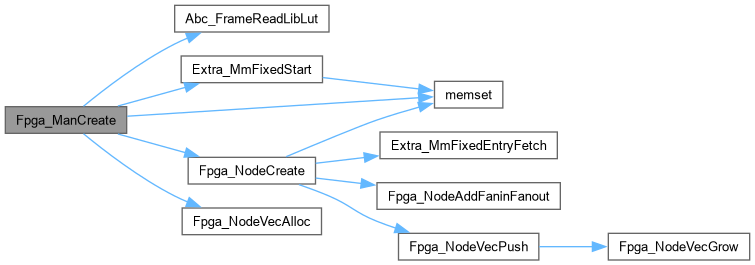

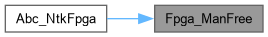

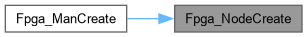

Function*************************************************************

Synopsis [Create the mapping manager.]

Description [The number of inputs and outputs is assumed to be known is advance. It is much simpler to have them fixed upfront. When it comes to representing the object graph in the form of AIG, the resulting manager is similar to the regular AIG manager, except that it does not use reference counting (and therefore does not have garbage collections). It does have table resizing. The data structure is more flexible to represent additional information needed for mapping.]

SideEffects []

SeeAlso []

Definition at line 163 of file fpgaCreate.c.

|

extern |

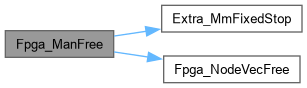

Function*************************************************************

Synopsis [Deallocates the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 217 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Prints runtime statistics of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 252 of file fpgaCreate.c.

|

extern |

Definition at line 55 of file fpgaCreate.c.

|

extern |

|

extern |

Definition at line 56 of file fpgaCreate.c.

|

extern |

FUNCTION DEFINITIONS ///.

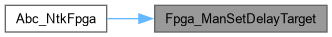

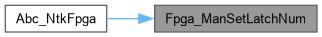

Function*************************************************************

Synopsis [Reads parameters of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 51 of file fpgaCreate.c.

|

extern |

Definition at line 53 of file fpgaCreate.c.

|

extern |

Definition at line 59 of file fpgaCreate.c.

|

extern |

Definition at line 60 of file fpgaCreate.c.

|

extern |

Definition at line 52 of file fpgaCreate.c.

|

extern |

Definition at line 54 of file fpgaCreate.c.

|

extern |

Definition at line 58 of file fpgaCreate.c.

|

extern |

Definition at line 57 of file fpgaCreate.c.

|

extern |

Definition at line 65 of file fpgaCreate.c.

|

extern |

Definition at line 63 of file fpgaCreate.c.

|

extern |

Definition at line 66 of file fpgaCreate.c.

|

extern |

Definition at line 67 of file fpgaCreate.c.

|

extern |

Definition at line 64 of file fpgaCreate.c.

|

extern |

Definition at line 72 of file fpgaCreate.c.

|

extern |

|

extern |

Definition at line 62 of file fpgaCreate.c.

|

extern |

Definition at line 71 of file fpgaCreate.c.

|

extern |

Definition at line 70 of file fpgaCreate.c.

|

extern |

Definition at line 73 of file fpgaCreate.c.

|

extern |

|

extern |

|

extern |

Definition at line 61 of file fpgaCreate.c.

|

extern |

Definition at line 69 of file fpgaCreate.c.

|

extern |

Definition at line 68 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Prints some interesting stats.]

Description []

SideEffects []

SeeAlso []

Definition at line 564 of file fpgaCreate.c.

|

extern |

FUNCTION DEFINITIONS ///.

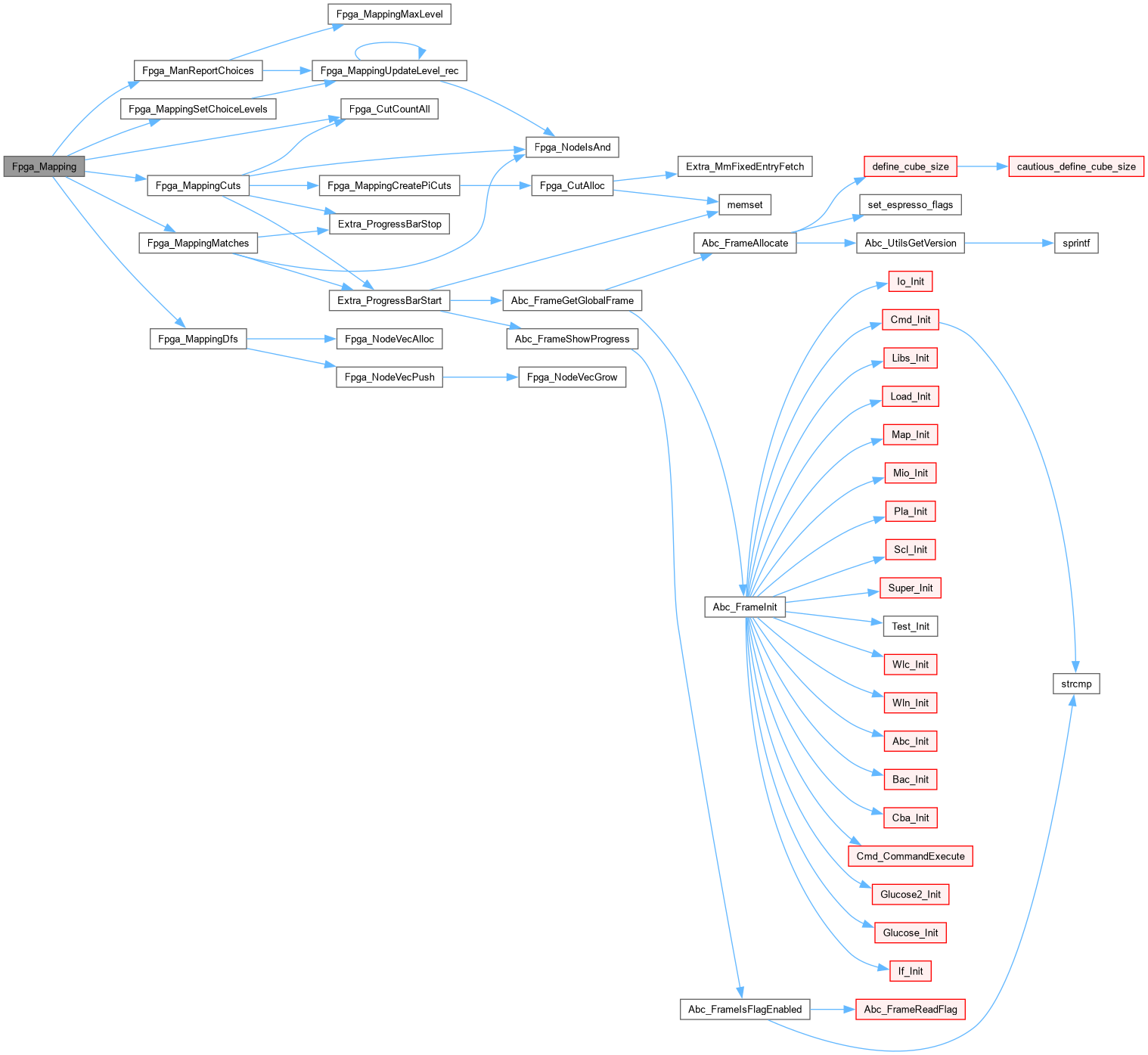

Function*************************************************************

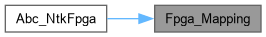

Synopsis [Performs technology mapping for the given object graph.]

Description [The object graph is stored in the mapping manager. First, all the AND-nodes, which fanout into the POs, are collected in the DFS fashion. Next, three steps are performed: the k-feasible cuts are computed for each node, the truth tables are computed for each cut, and the delay-optimal matches are assigned for each node.]

SideEffects []

SeeAlso []

Definition at line 53 of file fpgaCore.c.

|

extern |

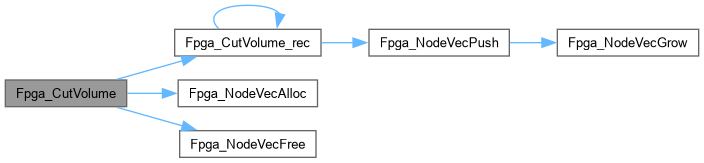

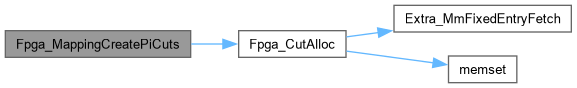

Function*************************************************************

Synopsis [Performs technology mapping for variable-size-LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 181 of file fpgaCut.c.

|

extern |

Function*************************************************************

Synopsis [Sets the used cuts to be the currently selected ones.]

Description []

SideEffects []

SeeAlso []

Definition at line 459 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

Synopsis [Elementary AND operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 470 of file fpgaCreate.c.

|

extern |

Definition at line 128 of file fpgaCreate.c.

|

extern |

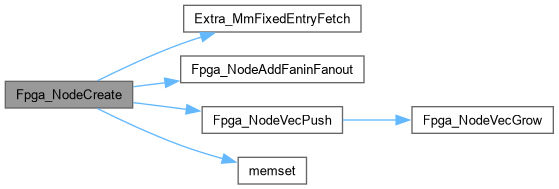

Function*************************************************************

Synopsis [Creates a new node.]

Description [This procedure should be called to create the constant node and the PI nodes first.]

SideEffects []

SeeAlso []

Definition at line 293 of file fpgaCreate.c.

|

extern |

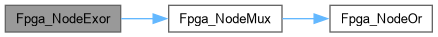

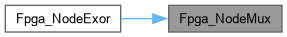

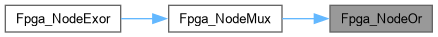

Function*************************************************************

Synopsis [Elementary EXOR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 506 of file fpgaCreate.c.

|

extern |

|

extern |

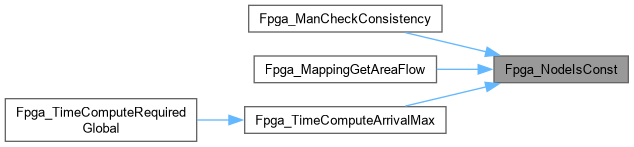

Function*************************************************************

Synopsis [Checks the type of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 125 of file fpgaCreate.c.

|

extern |

|

extern |

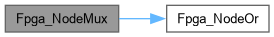

Function*************************************************************

Synopsis [Elementary MUX operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 522 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Elementary OR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 488 of file fpgaCreate.c.

|

extern |

Definition at line 105 of file fpgaCreate.c.

|

extern |

Definition at line 104 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Reads parameters of the mapping node.]

Description []

SideEffects []

SeeAlso []

Definition at line 99 of file fpgaCreate.c.

|

extern |

Definition at line 100 of file fpgaCreate.c.

|

extern |

Definition at line 103 of file fpgaCreate.c.

|

extern |

Definition at line 102 of file fpgaCreate.c.

|

extern |

Definition at line 106 of file fpgaCreate.c.

|

extern |

Definition at line 101 of file fpgaCreate.c.

|

extern |

Definition at line 107 of file fpgaCreate.c.

|

extern |

|

extern |

Function*************************************************************

Synopsis [Sets the node to be equivalent to the given one.]

Description [This procedure is a work-around for the equivalence check. Does not verify the equivalence. Use at the user's risk.]

SideEffects []

SeeAlso []

Definition at line 544 of file fpgaCreate.c.

|

extern |

Definition at line 108 of file fpgaCreate.c.

|

extern |

Definition at line 109 of file fpgaCreate.c.

|

extern |

|

extern |

Definition at line 110 of file fpgaCreate.c.

|

extern |

Definition at line 111 of file fpgaCreate.c.

|

extern |

Definition at line 112 of file fpgaCreate.c.

|

extern |

Function*************************************************************

Synopsis [Sets simple LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 252 of file fpga.c.

|

extern |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 79 of file fpgaTruth.c.