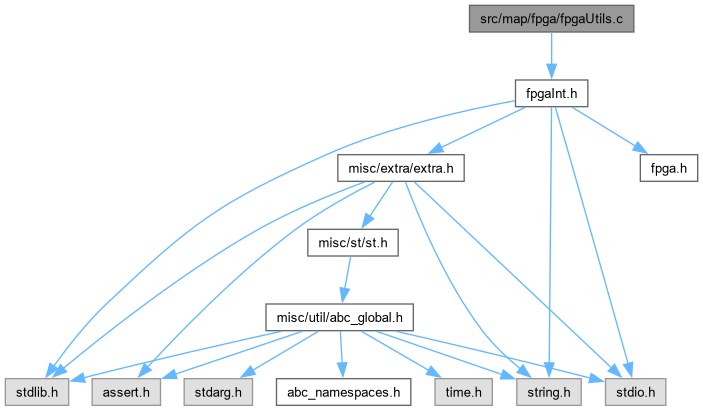

#include "fpgaInt.h"

Go to the source code of this file.

Macros | |

| #define | FPGA_CO_LIST_SIZE 5 |

| DECLARATIONS ///. | |

| #define FPGA_CO_LIST_SIZE 5 |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaUtils.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

]

Definition at line 28 of file fpgaUtils.c.

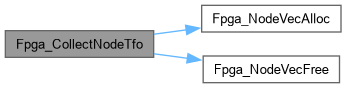

| Fpga_NodeVec_t * Fpga_CollectNodeTfo | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode ) |

Function*************************************************************

Synopsis [Collects the TFO of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 675 of file fpgaUtils.c.

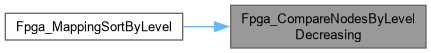

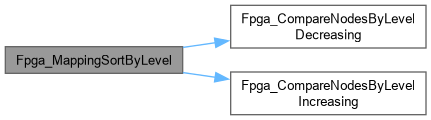

| int Fpga_CompareNodesByLevelDecreasing | ( | Fpga_Node_t ** | ppS1, |

| Fpga_Node_t ** | ppS2 ) |

Function*************************************************************

Synopsis [Compares the supergates by their level.]

Description []

SideEffects []

SeeAlso []

Definition at line 544 of file fpgaUtils.c.

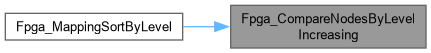

| int Fpga_CompareNodesByLevelIncreasing | ( | Fpga_Node_t ** | ppS1, |

| Fpga_Node_t ** | ppS2 ) |

Function*************************************************************

Synopsis [Compares the supergates by their level.]

Description []

SideEffects []

SeeAlso []

Definition at line 564 of file fpgaUtils.c.

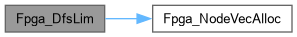

| Fpga_NodeVec_t * Fpga_DfsLim | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| int | nLevels ) |

Function*************************************************************

Synopsis [Computes the limited DFS ordering for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 606 of file fpgaUtils.c.

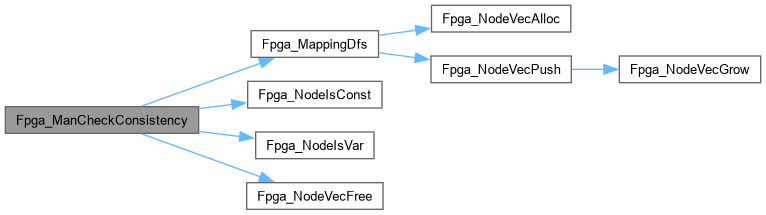

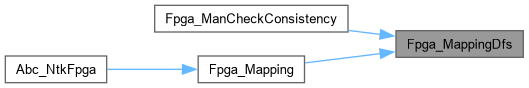

| int Fpga_ManCheckConsistency | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Verify one useful property.]

Description [This procedure verifies one useful property. After the FRAIG construction with choice nodes is over, each primary node should have fanins that are primary nodes. The primary nodes is the one that does not have pNode->pRepr set to point to another node.]

SideEffects []

SeeAlso []

Definition at line 500 of file fpgaUtils.c.

| void Fpga_ManCleanData0 | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Computes the limited DFS ordering for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 657 of file fpgaUtils.c.

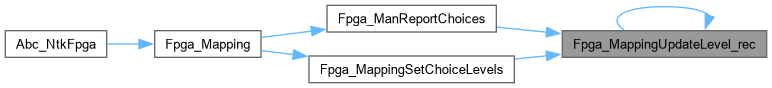

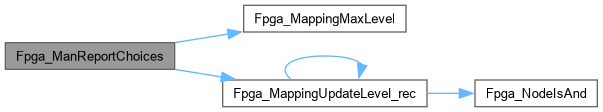

| void Fpga_ManReportChoices | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Reports statistics on choice nodes.]

Description [The number of choice nodes is the number of primary nodes, which has pNextE set to a pointer. The number of choices is the number of entries in the equivalent-node lists of the primary nodes.]

SideEffects []

SeeAlso []

Definition at line 897 of file fpgaUtils.c.

| float Fpga_MappingArea | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Computes the area of the current mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 177 of file fpgaUtils.c.

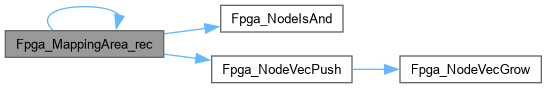

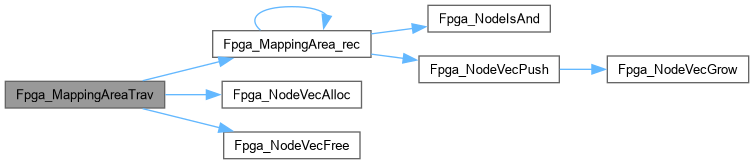

| float Fpga_MappingArea_rec | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| Fpga_NodeVec_t * | vNodes ) |

Function*************************************************************

Synopsis [Recursively computes the DFS ordering of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 203 of file fpgaUtils.c.

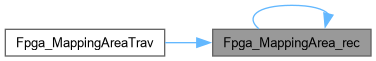

| float Fpga_MappingAreaTrav | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Computes the area of the current mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 239 of file fpgaUtils.c.

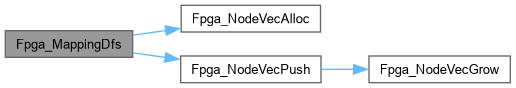

| Fpga_NodeVec_t * Fpga_MappingDfs | ( | Fpga_Man_t * | pMan, |

| int | fCollectEquiv ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Computes the DFS ordering of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 54 of file fpgaUtils.c.

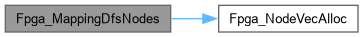

| Fpga_NodeVec_t * Fpga_MappingDfsNodes | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t ** | ppNodes, | ||

| int | nNodes, | ||

| int | fEquiv ) |

Function*************************************************************

Synopsis [Computes the DFS ordering of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 129 of file fpgaUtils.c.

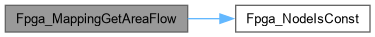

| float Fpga_MappingGetAreaFlow | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 153 of file fpgaUtils.c.

| Fpga_NodeVec_t * Fpga_MappingLevelize | ( | Fpga_Man_t * | pMan, |

| Fpga_NodeVec_t * | vNodes ) |

Function*************************************************************

Synopsis [Levelizes the nodes accessible from the POs.]

Description []

SideEffects []

SeeAlso []

Definition at line 747 of file fpgaUtils.c.

| int Fpga_MappingMaxLevel | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Sets up the mask.]

Description []

SideEffects []

SeeAlso []

Definition at line 804 of file fpgaUtils.c.

| void Fpga_MappingPrintOutputArrivals | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints a bunch of latest arriving outputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 402 of file fpgaUtils.c.

| void Fpga_MappingSetChoiceLevels | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Resets the levels of the nodes in the choice graph.]

Description [Makes the level of the choice nodes to be equal to the maximum of the level of the nodes in the equivalence class. This way sorting by level leads to the reverse topological order, which is needed for the required time computation.]

SideEffects []

SeeAlso []

Definition at line 876 of file fpgaUtils.c.

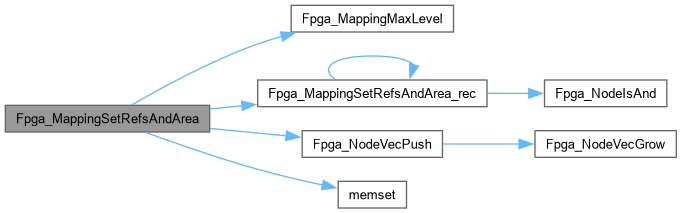

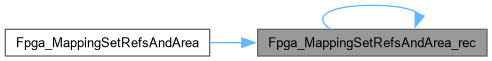

| float Fpga_MappingSetRefsAndArea | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Sets the correct reference counts for the mapping.]

Description [Collects the nodes in reverse topological order and places in them in array pMan->vMapping.]

SideEffects []

SeeAlso []

Definition at line 299 of file fpgaUtils.c.

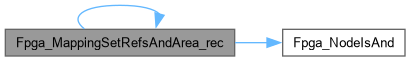

| float Fpga_MappingSetRefsAndArea_rec | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| Fpga_Node_t ** | ppStore ) |

Function*************************************************************

Synopsis [Recursively computes the DFS ordering of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 267 of file fpgaUtils.c.

| void Fpga_MappingSetupMask | ( | unsigned | uMask[], |

| int | nVarsMax ) |

Function*************************************************************

Synopsis [Sets up the mask.]

Description []

SideEffects []

SeeAlso []

Definition at line 475 of file fpgaUtils.c.

| void Fpga_MappingSetupTruthTables | ( | unsigned | uTruths[][2] | ) |

Function*************************************************************

Synopsis [Sets up the truth tables.]

Description []

SideEffects []

SeeAlso []

Definition at line 449 of file fpgaUtils.c.

| void Fpga_MappingSortByLevel | ( | Fpga_Man_t * | pMan, |

| Fpga_NodeVec_t * | vNodes, | ||

| int | fIncreasing ) |

Function*************************************************************

Synopsis [Orders the nodes in the decreasing order of levels.]

Description []

SideEffects []

SeeAlso []

Definition at line 584 of file fpgaUtils.c.

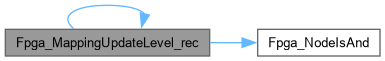

| int Fpga_MappingUpdateLevel_rec | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNode, | ||

| int | fMaximum ) |

Function*************************************************************

Synopsis [Analyses choice nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 826 of file fpgaUtils.c.