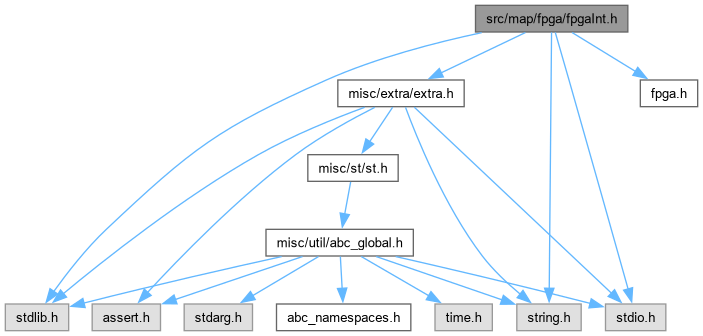

#include <stdio.h>#include <stdlib.h>#include <string.h>#include "misc/extra/extra.h"#include "fpga.h"

Go to the source code of this file.

Classes | |

| struct | Fpga_ManStruct_t_ |

| STRUCTURE DEFINITIONS ///. More... | |

| struct | Fpga_LutLibStruct_t_ |

| struct | Fpga_NodeStruct_t_ |

| struct | Fpga_CutStruct_t_ |

| struct | Fpga_NodeVecStruct_t_ |

Macros | |

| #define | FPGA_MAX_LEAVES 6 |

| INCLUDES ///. | |

| #define | FPGA_MASK(n) |

| #define | FPGA_FULL (~((unsigned)0)) |

| #define | FPGA_NO_VAR (-9999.0) |

| #define | FPGA_NUM_BYTES(n) |

| #define | FPGA_MIN(a, b) |

| #define | FPGA_MAX(a, b) |

| #define | FPGA_FLOAT_LARGE ((float)1.0e+20) |

| #define | FPGA_FLOAT_SMALL ((float)1.0e-20) |

| #define | FPGA_INT_LARGE (10000000) |

| #define | FPGA_SEQ_SIGN(p) |

| #define | Fpga_CutIsComplement(p) |

| #define | Fpga_CutRegular(p) |

| #define | Fpga_CutNot(p) |

| #define | Fpga_CutNotCond(p, c) |

| #define | Fpga_SeqIsComplement(p) |

| #define | Fpga_SeqRegular(p) |

| #define | Fpga_SeqIndex(p) |

| #define | Fpga_SeqIndexCreate(p, Ind) |

| #define | Fpga_NodeReadRef(p) |

| #define | Fpga_NodeRef(p) |

| #define | Fpga_NodeIsSimComplement(p) |

| #define | FPGA_RANDOM_UNSIGNED ((((unsigned)rand()) << 24) ^ (((unsigned)rand()) << 12) ^ ((unsigned)rand())) |

| #define | Fpga_NodeReadNextFanout(pNode, pFanout) |

| #define | Fpga_NodeReadNextFanoutPlace(pNode, pFanout) |

| #define | Fpga_NodeForEachFanout(pNode, pFanout) |

| #define | Fpga_NodeForEachFanoutSafe(pNode, pFanout, pFanout2) |

| #define Fpga_CutNot | ( | p | ) |

| #define Fpga_CutNotCond | ( | p, | |

| c ) |

| #define Fpga_CutRegular | ( | p | ) |

| #define FPGA_MASK | ( | n | ) |

| #define FPGA_MAX_LEAVES 6 |

INCLUDES ///.

CFile****************************************************************

FileName [fpgaInt.h]

PackageName [MVSIS 2.0: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] PARAMETERS /// MACRO DEFINITIONS ///

| #define Fpga_NodeForEachFanout | ( | pNode, | |

| pFanout ) |

Definition at line 269 of file fpgaInt.h.

| #define Fpga_NodeForEachFanoutSafe | ( | pNode, | |

| pFanout, | |||

| pFanout2 ) |

Definition at line 274 of file fpgaInt.h.

| #define Fpga_NodeIsSimComplement | ( | p | ) |

| #define Fpga_NodeReadNextFanout | ( | pNode, | |

| pFanout ) |

Definition at line 258 of file fpgaInt.h.

| #define Fpga_NodeReadNextFanoutPlace | ( | pNode, | |

| pFanout ) |

Definition at line 264 of file fpgaInt.h.

| #define Fpga_NodeReadRef | ( | p | ) |

| #define Fpga_NodeRef | ( | p | ) |

| #define FPGA_NUM_BYTES | ( | n | ) |

| #define FPGA_RANDOM_UNSIGNED ((((unsigned)rand()) << 24) ^ (((unsigned)rand()) << 12) ^ ((unsigned)rand())) |

| #define FPGA_SEQ_SIGN | ( | p | ) |

| #define Fpga_SeqIndex | ( | p | ) |

| #define Fpga_SeqIndexCreate | ( | p, | |

| Ind ) |

| #define Fpga_SeqIsComplement | ( | p | ) |

| #define Fpga_SeqRegular | ( | p | ) |

|

extern |

|

extern |

DECLARATIONS ///.

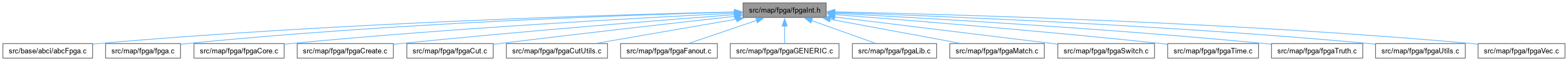

CFile****************************************************************

FileName [fpgaCutUtils.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Generic technology mapping engine.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

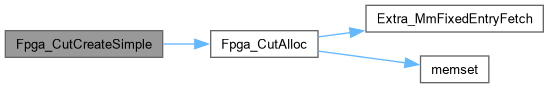

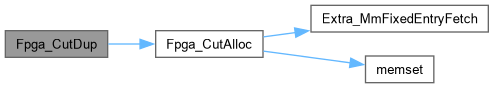

Synopsis [Allocates the cut.]

Description []

SideEffects []

SeeAlso []

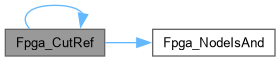

Definition at line 43 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

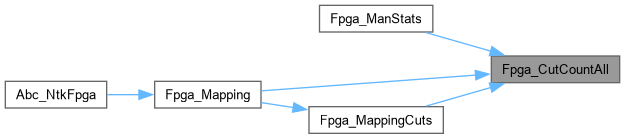

Synopsis [Counts all the cuts.]

Description []

SideEffects []

SeeAlso []

Definition at line 767 of file fpgaCut.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 123 of file fpgaCutUtils.c.

|

extern |

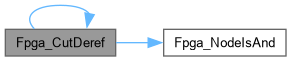

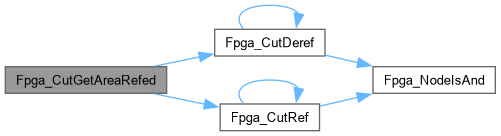

function*************************************************************

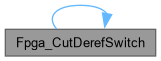

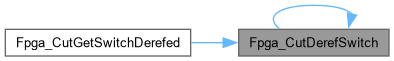

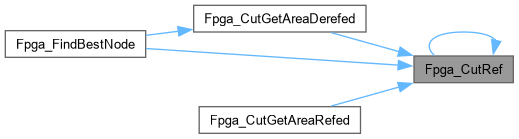

synopsis [Dereferences the cut.]

description [This procedure is similar to the procedure NodeRecusiveDeref.]

sideeffects []

seealso []

Definition at line 421 of file fpgaCutUtils.c.

|

extern |

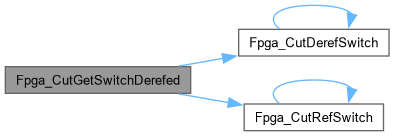

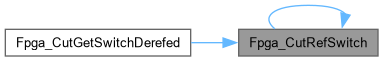

function*************************************************************

synopsis [Dereferences the cut.]

description [This procedure is similar to the procedure NodeRecusiveDeref.]

sideeffects []

seealso []

Definition at line 95 of file fpgaSwitch.c.

|

extern |

Function*************************************************************

Synopsis [Duplicates the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 62 of file fpgaCutUtils.c.

|

extern |

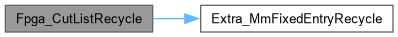

Function*************************************************************

Synopsis [Deallocates the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 85 of file fpgaCutUtils.c.

|

extern |

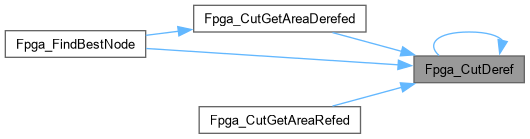

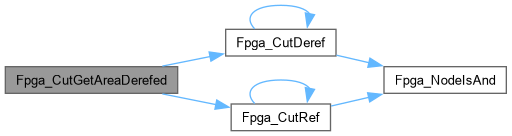

function*************************************************************

synopsis [Computes the exact area associated with the cut.]

description []

sideeffects []

seealso []

Definition at line 362 of file fpgaCutUtils.c.

|

extern |

function*************************************************************

synopsis [Computes the area flow of the cut.]

description []

sideeffects []

seealso []

Definition at line 314 of file fpgaCutUtils.c.

|

extern |

function*************************************************************

synopsis [Computes the exact area associated with the cut.]

description []

sideeffects []

seealso []

Definition at line 340 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

Synopsis [Computes the arrival time and the area flow of the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 279 of file fpgaCutUtils.c.

|

extern |

function*************************************************************

synopsis [Computes the exact area associated with the cut.]

description []

sideeffects []

seealso []

Definition at line 146 of file fpgaCutUtils.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaSwitch.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Generic technology mapping engine.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 8, 2003.]

Revision [

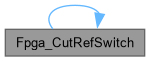

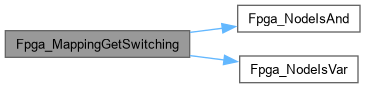

] FUNCTION DEFINITIONS /// function*************************************************************

synopsis [Computes the exact area associated with the cut.]

description []

sideeffects []

seealso []

Definition at line 43 of file fpgaSwitch.c.

|

extern |

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 162 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 211 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 190 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 102 of file fpgaCutUtils.c.

|

extern |

function*************************************************************

synopsis [References the cut.]

description [This procedure is similar to the procedure NodeReclaim.]

sideeffects []

seealso []

Definition at line 384 of file fpgaCutUtils.c.

|

extern |

function*************************************************************

synopsis [References the cut.]

description [This procedure is similar to the procedure NodeReclaim.]

sideeffects []

seealso []

Definition at line 63 of file fpgaSwitch.c.

|

extern |

|

extern |

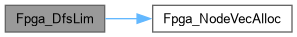

Function*************************************************************

Synopsis [Computes the limited DFS ordering for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 606 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Returns 1 if the delays are discrete.]

Description []

SideEffects []

SeeAlso []

Definition at line 236 of file fpgaLib.c.

|

extern |

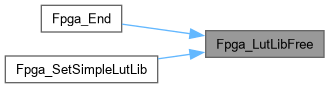

Function*************************************************************

Synopsis [Frees the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 185 of file fpgaLib.c.

|

extern |

Function*************************************************************

Synopsis [Prints the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 205 of file fpgaLib.c.

|

extern |

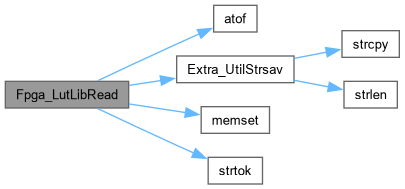

Function*************************************************************

Synopsis [Reads the description of LUTs from the LUT library file.]

Description []

SideEffects []

SeeAlso []

Definition at line 58 of file fpgaLib.c.

|

extern |

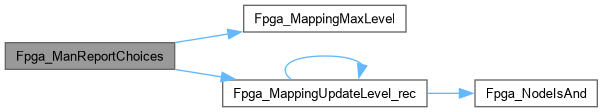

Function*************************************************************

Synopsis [Reports statistics on choice nodes.]

Description [The number of choice nodes is the number of primary nodes, which has pNextE set to a pointer. The number of choices is the number of entries in the equivalent-node lists of the primary nodes.]

SideEffects []

SeeAlso []

Definition at line 897 of file fpgaUtils.c.

|

extern |

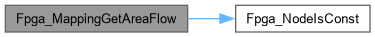

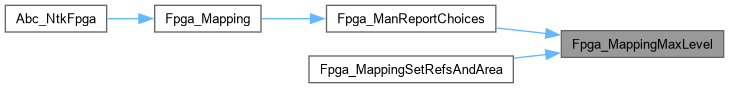

Function*************************************************************

Synopsis [Computes the area of the current mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 177 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Computes the area of the current mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 239 of file fpgaUtils.c.

|

extern |

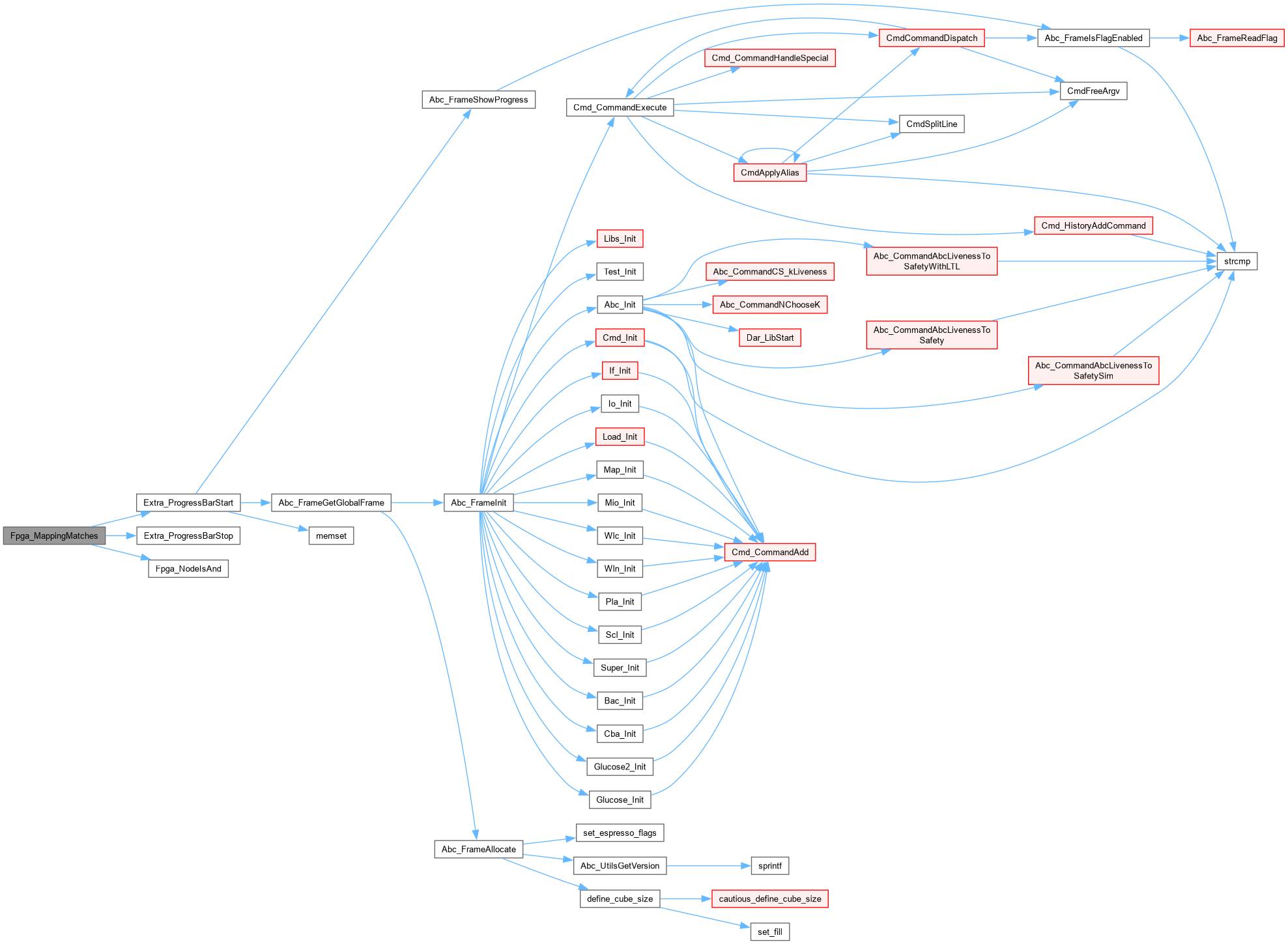

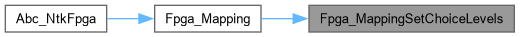

Function*************************************************************

Synopsis [Performs technology mapping for variable-size-LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 181 of file fpgaCut.c.

|

extern |

GLOBAL VARIABLES ///.

FUNCTION DEFINITIONS ///

GLOBAL VARIABLES ///.

Function*************************************************************

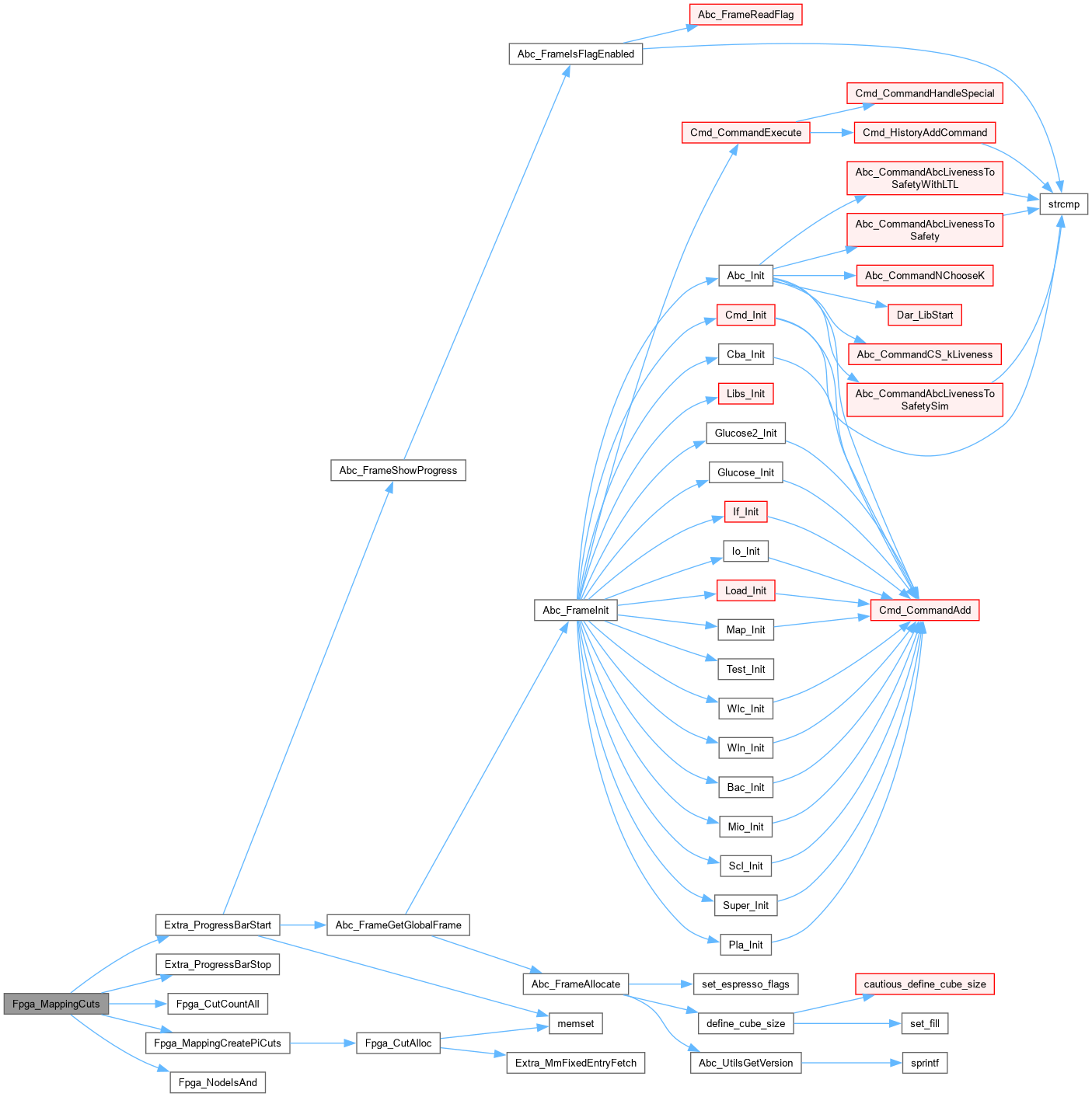

Synopsis [Computes the cuts for each node in the object graph.]

Description [The cuts are computed in one sweep over the mapping graph. First, the elementary cuts, which include the node itself, are assigned to the PI nodes. The internal nodes are considered in the DFS order. Each node is two-input AND-gate. So to compute the cuts at a node, we need to merge the sets of cuts of its two predecessors. The merged set contains only unique cuts with the number of inputs equal to k or less. Finally, the elementary cut, composed of the node itself, is added to the set of cuts for the node.

This procedure is pretty fast for 5-feasible cuts, but it dramatically slows down on some "dense" networks when computing 6-feasible cuts. The problem is that there are too many cuts in this case. We should think how to heuristically trim the number of cuts in such cases, to have reasonable runtime.]

SideEffects []

SeeAlso []

Definition at line 130 of file fpgaCut.c.

|

extern |

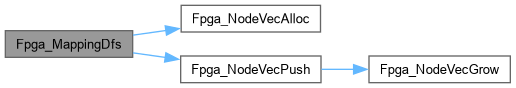

FUNCTION DEFINITIONS ///.

Function*************************************************************

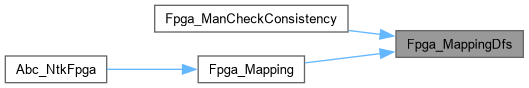

Synopsis [Computes the DFS ordering of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 54 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Computes the DFS ordering of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 129 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 153 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Computes the array of mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 127 of file fpgaSwitch.c.

|

extern |

Function*************************************************************

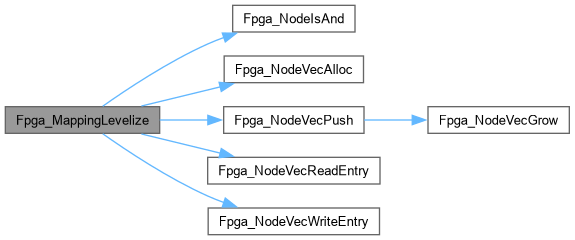

Synopsis [Levelizes the nodes accessible from the POs.]

Description []

SideEffects []

SeeAlso []

Definition at line 747 of file fpgaUtils.c.

|

extern |

FUNCTION DEFINITIONS ///.

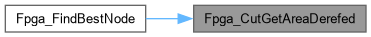

Function*************************************************************

Synopsis [Finds the best delay assignment of LUTs.]

Description [This procedure iterates through all the nodes of the object graph reachable from the POs and assigns the best match to each of them. If the flag fDelayOriented is set to 1, it tries to minimize the arrival time and uses the area flow as a tie-breaker. If the flag is set to 0, it considers all the cuts, whose arrival times matches the required time at the node, and minimizes the area flow using the arrival time as a tie-breaker.

Before this procedure is called, the required times should be set and the fanout counts should be computed. In the first iteration, the required times are set to very large number (by NodeCreate) and the fanout counts are set to the number of fanouts in the AIG. In the following iterations, the required times are set by the backward traversal, while the fanouts are estimated approximately.

If the arrival times of the PI nodes are given, they should be assigned to the PIs after the cuts are computed and before this procedure is called for the first time.]

SideEffects []

SeeAlso []

Definition at line 67 of file fpgaMatch.c.

|

extern |

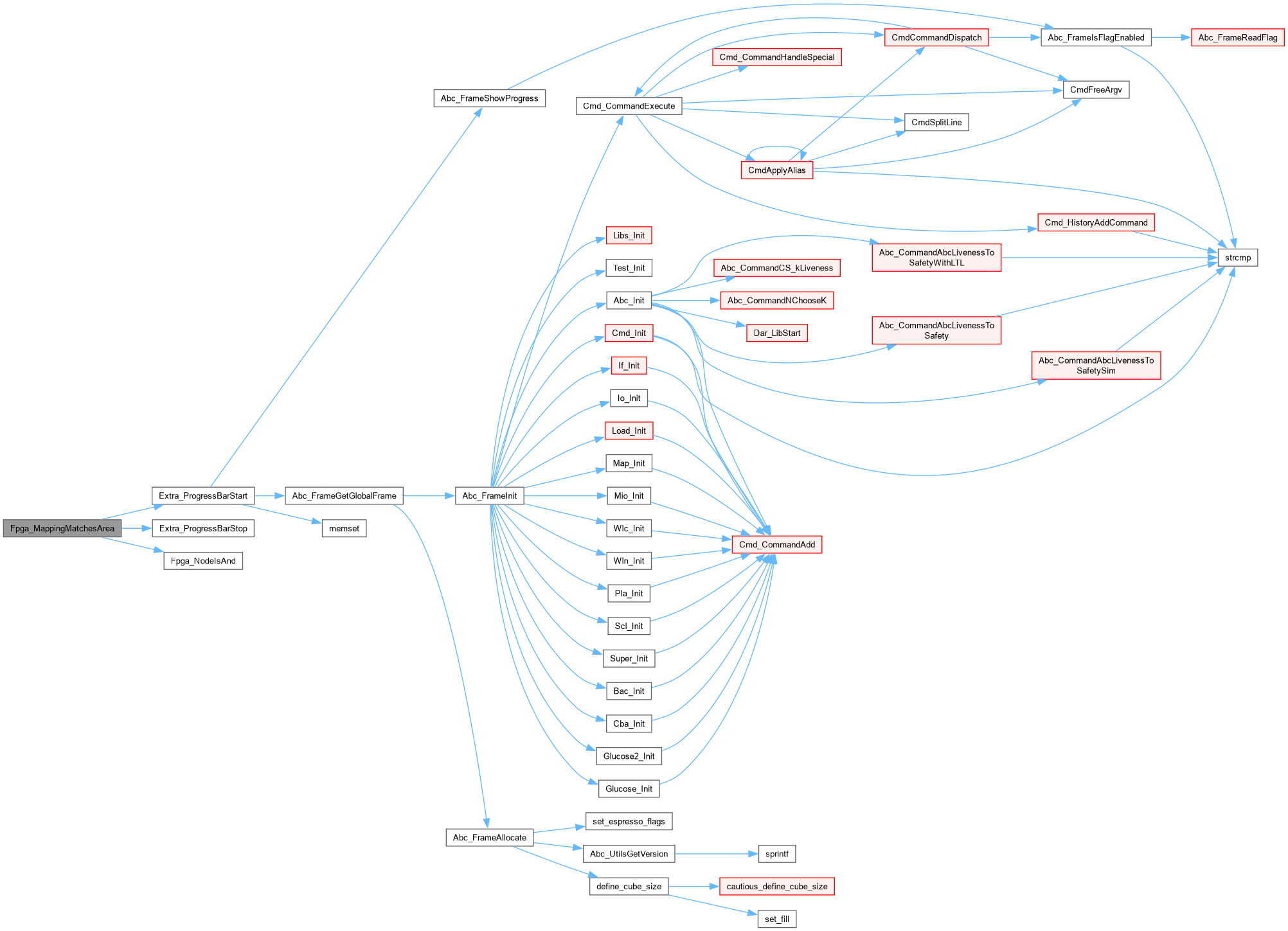

Function*************************************************************

Synopsis [Finds the best area assignment of LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 196 of file fpgaMatch.c.

|

extern |

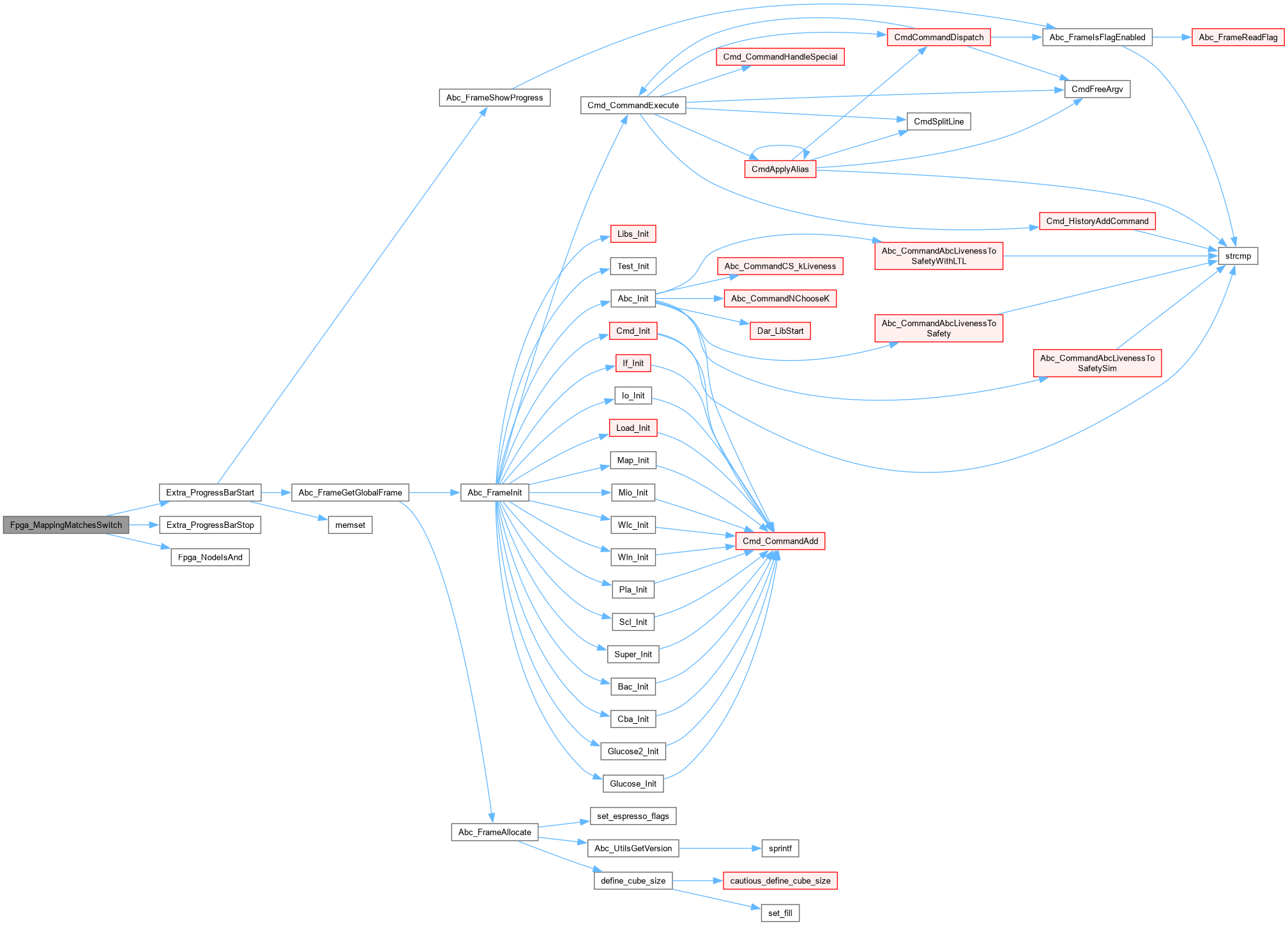

Function*************************************************************

Synopsis [Finds the best area assignment of LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 349 of file fpgaMatch.c.

|

extern |

Function*************************************************************

Synopsis [Sets up the mask.]

Description []

SideEffects []

SeeAlso []

Definition at line 804 of file fpgaUtils.c.

|

extern |

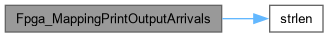

Function*************************************************************

Synopsis [Prints a bunch of latest arriving outputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 402 of file fpgaUtils.c.

|

extern |

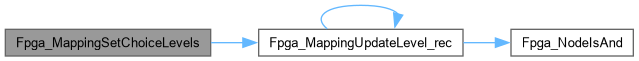

Function*************************************************************

Synopsis [Resets the levels of the nodes in the choice graph.]

Description [Makes the level of the choice nodes to be equal to the maximum of the level of the nodes in the equivalence class. This way sorting by level leads to the reverse topological order, which is needed for the required time computation.]

SideEffects []

SeeAlso []

Definition at line 876 of file fpgaUtils.c.

|

extern |

Function*************************************************************

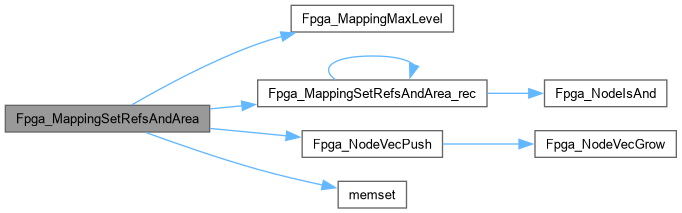

Synopsis [Sets the correct reference counts for the mapping.]

Description [Collects the nodes in reverse topological order and places in them in array pMan->vMapping.]

SideEffects []

SeeAlso []

Definition at line 299 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Sets up the mask.]

Description []

SideEffects []

SeeAlso []

Definition at line 475 of file fpgaUtils.c.

|

extern |

Function*************************************************************

Synopsis [Sets up the truth tables.]

Description []

SideEffects []

SeeAlso []

Definition at line 449 of file fpgaUtils.c.

|

extern |

|

extern |

|

extern |

Function*************************************************************

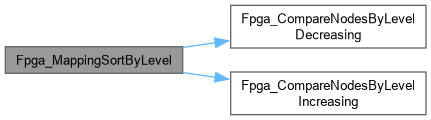

Synopsis [Orders the nodes in the decreasing order of levels.]

Description []

SideEffects []

SeeAlso []

Definition at line 584 of file fpgaUtils.c.

|

extern |

|

extern |

|

extern |

|

extern |

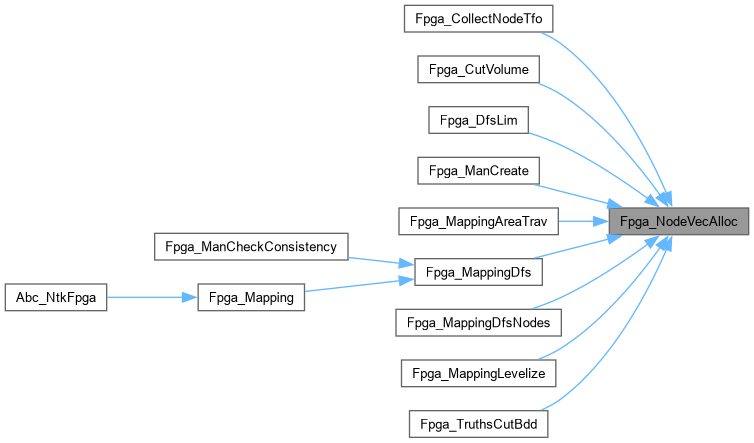

FUNCTION DEFINITIONS ///.

Function*************************************************************

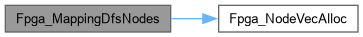

Synopsis [Allocates a vector with the given capacity.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file fpgaVec.c.

|

extern |

|

extern |

|

extern |

|

extern |

|

extern |

|

extern |

Function*************************************************************

Synopsis [Inserts a new node in the order by arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 366 of file fpgaVec.c.

|

extern |

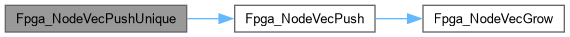

Function*************************************************************

Synopsis [Add the element while ensuring uniqueness.]

Description [Returns 1 if the element was found, and 0 if it was new. ]

SideEffects []

SeeAlso []

Definition at line 192 of file fpgaVec.c.

|

extern |

|

extern |

|

extern |

|

extern |

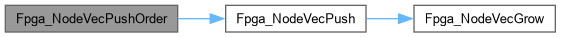

Function*************************************************************

Synopsis [Inserts a new node in the order by arrival times.]

Description []

SideEffects []

SeeAlso []

|

extern |

|

extern |

|

extern |

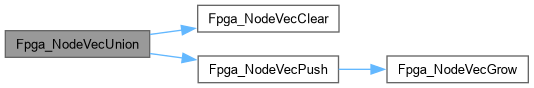

Function*************************************************************

Synopsis [Computes the union of nodes in two arrays.]

Description []

SideEffects []

SeeAlso []

Definition at line 345 of file fpgaVec.c.

|

extern |

|

extern |

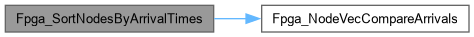

Function*************************************************************

Synopsis [Orders the nodes in the increasing order of the arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 326 of file fpgaVec.c.

|

extern |

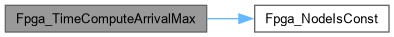

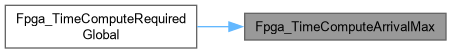

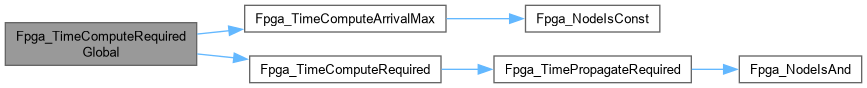

Function*************************************************************

Synopsis [Computes the maximum arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 89 of file fpgaTime.c.

|

extern |

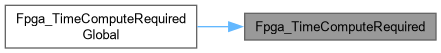

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 168 of file fpgaTime.c.

|

extern |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 136 of file fpgaTime.c.

|

extern |

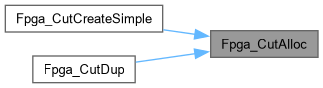

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaTime.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

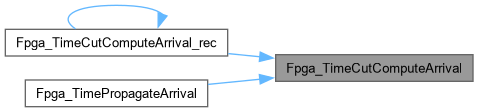

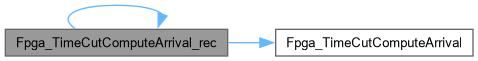

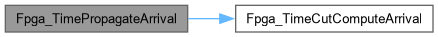

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Computes the arrival times of the cut.]

Description [Computes the maximum arrival time of the cut leaves and adds the delay of the LUT.]

SideEffects []

SeeAlso []

Definition at line 44 of file fpgaTime.c.

|

extern |

Function*************************************************************

Synopsis [Computes the arrival times of the cut recursively.]

Description [When computing the arrival time for the previously unused cuts, their arrival time may be incorrect because their fanins have incorrect arrival time. This procedure is called to fix this problem.]

SideEffects []

SeeAlso []

Definition at line 69 of file fpgaTime.c.

|

extern |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 245 of file fpgaTime.c.

|

extern |

Function*************************************************************

Synopsis [Computes the required times of the given nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 205 of file fpgaTime.c.