Go to the source code of this file.

|

| Fpga_NodeVec_t * | Fpga_NodeVecAlloc (int nCap) |

| | FUNCTION DEFINITIONS ///.

|

| |

| void | Fpga_NodeVecFree (Fpga_NodeVec_t *p) |

| |

| Fpga_Node_t ** | Fpga_NodeVecReadArray (Fpga_NodeVec_t *p) |

| |

| int | Fpga_NodeVecReadSize (Fpga_NodeVec_t *p) |

| |

| void | Fpga_NodeVecGrow (Fpga_NodeVec_t *p, int nCapMin) |

| |

| void | Fpga_NodeVecShrink (Fpga_NodeVec_t *p, int nSizeNew) |

| |

| void | Fpga_NodeVecClear (Fpga_NodeVec_t *p) |

| |

| void | Fpga_NodeVecPush (Fpga_NodeVec_t *p, Fpga_Node_t *Entry) |

| |

| int | Fpga_NodeVecPushUnique (Fpga_NodeVec_t *p, Fpga_Node_t *Entry) |

| |

| Fpga_Node_t * | Fpga_NodeVecPop (Fpga_NodeVec_t *p) |

| |

| void | Fpga_NodeVecWriteEntry (Fpga_NodeVec_t *p, int i, Fpga_Node_t *Entry) |

| |

| Fpga_Node_t * | Fpga_NodeVecReadEntry (Fpga_NodeVec_t *p, int i) |

| |

| void | Fpga_NodeVecSortByLevel (Fpga_NodeVec_t *p) |

| |

| int | Fpga_NodeVecCompareArrivals (Fpga_Node_t **ppS1, Fpga_Node_t **ppS2) |

| |

| void | Fpga_SortNodesByArrivalTimes (Fpga_NodeVec_t *p) |

| |

| void | Fpga_NodeVecUnion (Fpga_NodeVec_t *p, Fpga_NodeVec_t *p1, Fpga_NodeVec_t *p2) |

| |

| void | Fpga_NodeVecPushOrder (Fpga_NodeVec_t *vNodes, Fpga_Node_t *pNode, int fIncreasing) |

| |

| void | Fpga_NodeVecReverse (Fpga_NodeVec_t *vNodes) |

| |

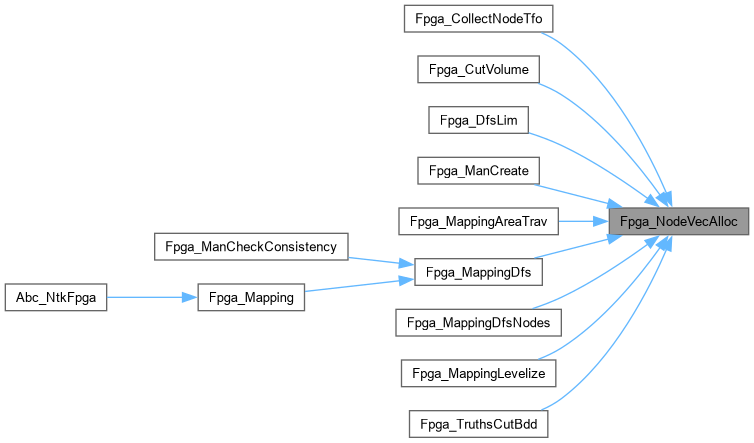

◆ Fpga_NodeVecAlloc()

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Allocates a vector with the given capacity.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file fpgaVec.c.

46{

49 if ( nCap > 0 && nCap < 16 )

50 nCap = 16;

55}

#define ABC_ALLOC(type, num)

struct Fpga_NodeStruct_t_ Fpga_Node_t

struct Fpga_NodeVecStruct_t_ Fpga_NodeVec_t

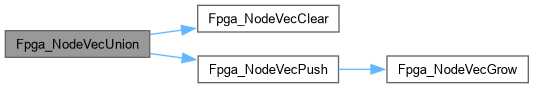

◆ Fpga_NodeVecClear()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 153 of file fpgaVec.c.

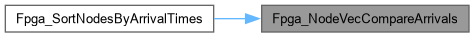

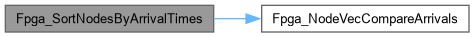

◆ Fpga_NodeVecCompareArrivals()

Function*************************************************************

Synopsis [Compares the arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 306 of file fpgaVec.c.

307{

308 if ( (*ppS1)->pCutBest->tArrival < (*ppS2)->pCutBest->tArrival )

309 return -1;

310 if ( (*ppS1)->pCutBest->tArrival > (*ppS2)->pCutBest->tArrival )

311 return 1;

312 return 0;

313}

◆ Fpga_NodeVecFree()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 68 of file fpgaVec.c.

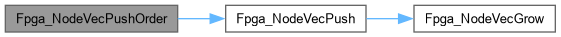

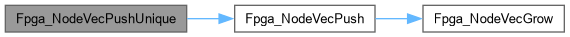

◆ Fpga_NodeVecGrow()

Function*************************************************************

Synopsis [Resizes the vector to the given capacity.]

Description []

SideEffects []

SeeAlso []

Definition at line 117 of file fpgaVec.c.

118{

119 if (

p->nCap >= nCapMin )

120 return;

123}

#define ABC_REALLOC(type, obj, num)

◆ Fpga_NodeVecPop()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 213 of file fpgaVec.c.

214{

215 return p->pArray[--

p->nSize];

216}

◆ Fpga_NodeVecPush()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 169 of file fpgaVec.c.

170{

171 if (

p->nSize ==

p->nCap )

172 {

175 else

177 }

178 p->pArray[

p->nSize++] = Entry;

179}

void Fpga_NodeVecGrow(Fpga_NodeVec_t *p, int nCapMin)

◆ Fpga_NodeVecPushOrder()

Function*************************************************************

Synopsis [Inserts a new node in the order by arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 366 of file fpgaVec.c.

367{

369 int i;

371

372 for ( i = vNodes->

nSize-1; i > 0; i-- )

373 {

374 pNode1 = vNodes->

pArray[i ];

375 pNode2 = vNodes->

pArray[i-1];

378 break;

379 vNodes->

pArray[i ] = pNode2;

380 vNodes->

pArray[i-1] = pNode1;

381 }

382}

void Fpga_NodeVecPush(Fpga_NodeVec_t *p, Fpga_Node_t *Entry)

◆ Fpga_NodeVecPushUnique()

Function*************************************************************

Synopsis [Add the element while ensuring uniqueness.]

Description [Returns 1 if the element was found, and 0 if it was new. ]

SideEffects []

SeeAlso []

Definition at line 192 of file fpgaVec.c.

193{

194 int i;

195 for ( i = 0; i <

p->nSize; i++ )

196 if (

p->pArray[i] == Entry )

197 return 1;

199 return 0;

200}

◆ Fpga_NodeVecReadArray()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 85 of file fpgaVec.c.

◆ Fpga_NodeVecReadEntry()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 246 of file fpgaVec.c.

247{

248 assert( i >= 0 && i < p->nSize );

250}

◆ Fpga_NodeVecReadSize()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 101 of file fpgaVec.c.

◆ Fpga_NodeVecReverse()

Function*************************************************************

Synopsis [Inserts a new node in the order by arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 395 of file fpgaVec.c.

396{

398 int i;

399 for ( i = 0; i < vNodes->

nSize/2; i++ )

400 {

401 pNode1 = vNodes->

pArray[i];

403 vNodes->

pArray[i] = pNode2;

405 }

406}

◆ Fpga_NodeVecShrink()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 136 of file fpgaVec.c.

137{

138 assert(

p->nSize >= nSizeNew );

140}

◆ Fpga_NodeVecSortByLevel()

Function*************************************************************

Synopsis [Sorting the entries by their integer value.]

Description []

SideEffects []

SeeAlso []

Definition at line 289 of file fpgaVec.c.

290{

291 qsort( (

void *)

p->pArray, (

size_t)

p->nSize,

sizeof(

Fpga_Node_t *),

292 (int (*)(const void *, const void *)) Fpga_NodeVecCompareLevels );

293}

◆ Fpga_NodeVecUnion()

Function*************************************************************

Synopsis [Computes the union of nodes in two arrays.]

Description []

SideEffects []

SeeAlso []

Definition at line 345 of file fpgaVec.c.

346{

347 int i;

349 for ( i = 0; i < p1->nSize; i++ )

351 for ( i = 0; i < p2->nSize; i++ )

353}

void Fpga_NodeVecClear(Fpga_NodeVec_t *p)

◆ Fpga_NodeVecWriteEntry()

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 229 of file fpgaVec.c.

230{

231 assert( i >= 0 && i < p->nSize );

232 p->pArray[i] = Entry;

233}

◆ Fpga_SortNodesByArrivalTimes()

Function*************************************************************

Synopsis [Orders the nodes in the increasing order of the arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 326 of file fpgaVec.c.

327{

328 qsort( (

void *)

p->pArray, (

size_t)

p->nSize,

sizeof(

Fpga_Node_t *),

330

331}

int Fpga_NodeVecCompareArrivals(Fpga_Node_t **ppS1, Fpga_Node_t **ppS2)