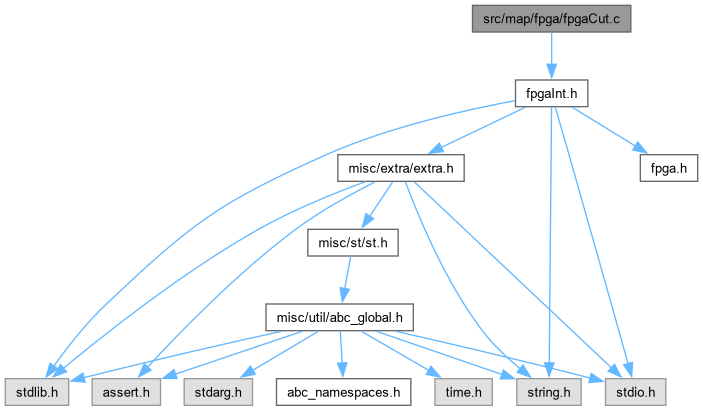

#include "fpgaInt.h"

Go to the source code of this file.

Classes | |

| struct | Fpga_CutTableStrutct_t |

Macros | |

| #define | FPGA_CUTS_MAX_COMPUTE 2000 |

| #define | FPGA_CUTS_MAX_USE 1000 |

| #define | FPGA_COUNT_ONES(u) |

| #define | Fpga_ListForEachCut(pList, pCut) |

| #define | Fpga_ListForEachCutSafe(pList, pCut, pCut2) |

Typedefs | |

| typedef typedefABC_NAMESPACE_IMPL_START struct Fpga_CutTableStrutct_t | Fpga_CutTable_t |

| DECLARATIONS ///. | |

Functions | |

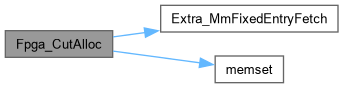

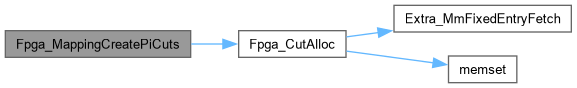

| Fpga_Cut_t * | Fpga_CutAlloc (Fpga_Man_t *p) |

| DECLARATIONS ///. | |

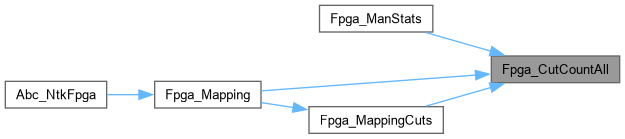

| int | Fpga_CutCountAll (Fpga_Man_t *pMan) |

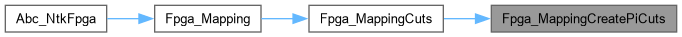

| void | Fpga_MappingCuts (Fpga_Man_t *p) |

| FUNCTION DEFINITIONS ///. | |

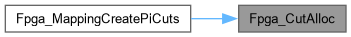

| void | Fpga_MappingCreatePiCuts (Fpga_Man_t *p) |

| Fpga_Cut_t * | Fpga_CutMergeLists2 (Fpga_Man_t *p, Fpga_CutTable_t *pTable, Fpga_Cut_t *pList1, Fpga_Cut_t *pList2, int fComp1, int fComp2, int fPivot1, int fPivot2) |

| void | Fpga_CutsCleanSign (Fpga_Man_t *pMan) |

| void | Fpga_CutsCleanRoot (Fpga_Man_t *pMan) |

| #define FPGA_COUNT_ONES | ( | u | ) |

| #define Fpga_ListForEachCut | ( | pList, | |

| pCut ) |

| #define Fpga_ListForEachCutSafe | ( | pList, | |

| pCut, | |||

| pCut2 ) |

Definition at line 94 of file fpgaCut.c.

| typedef typedefABC_NAMESPACE_IMPL_START struct Fpga_CutTableStrutct_t Fpga_CutTable_t |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaCut.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Generic technology mapping engine.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

]

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaCutUtils.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Generic technology mapping engine.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Allocates the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 43 of file fpgaCutUtils.c.

|

extern |

Function*************************************************************

Synopsis [Counts all the cuts.]

Description []

SideEffects []

SeeAlso []

Definition at line 767 of file fpgaCut.c.

| Fpga_Cut_t * Fpga_CutMergeLists2 | ( | Fpga_Man_t * | p, |

| Fpga_CutTable_t * | pTable, | ||

| Fpga_Cut_t * | pList1, | ||

| Fpga_Cut_t * | pList2, | ||

| int | fComp1, | ||

| int | fComp2, | ||

| int | fPivot1, | ||

| int | fPivot2 ) |

Function*************************************************************

Synopsis [Merges two lists of cuts.]

Description []

SideEffects []

SeeAlso []

Definition at line 539 of file fpgaCut.c.

| void Fpga_CutsCleanRoot | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Clean the signatures.]

Description []

SideEffects []

SeeAlso []

| void Fpga_CutsCleanSign | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Clean the signatures.]

Description []

SideEffects []

SeeAlso []

| void Fpga_MappingCreatePiCuts | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Performs technology mapping for variable-size-LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 181 of file fpgaCut.c.

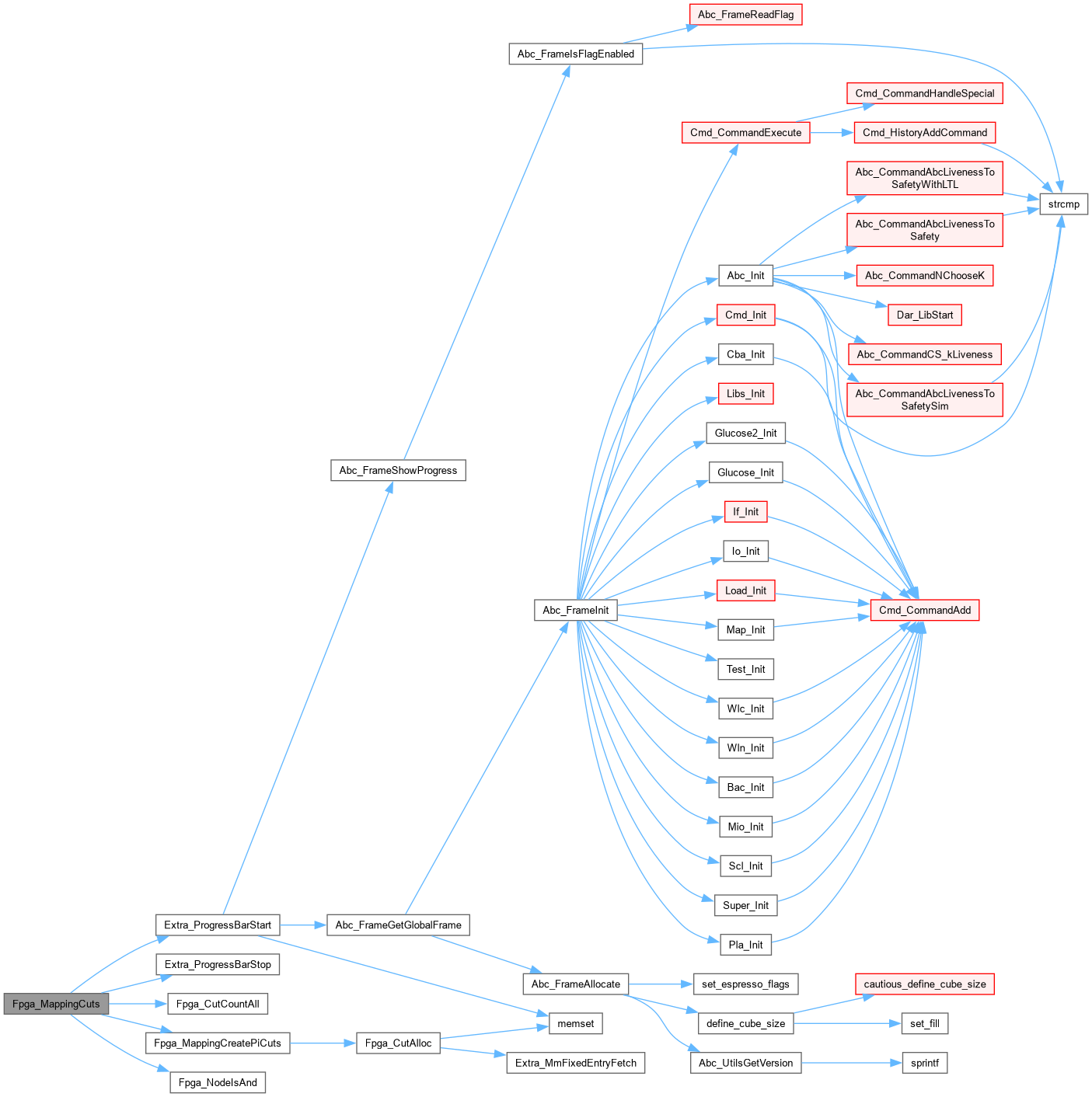

| void Fpga_MappingCuts | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///.

GLOBAL VARIABLES ///.

Function*************************************************************

Synopsis [Computes the cuts for each node in the object graph.]

Description [The cuts are computed in one sweep over the mapping graph. First, the elementary cuts, which include the node itself, are assigned to the PI nodes. The internal nodes are considered in the DFS order. Each node is two-input AND-gate. So to compute the cuts at a node, we need to merge the sets of cuts of its two predecessors. The merged set contains only unique cuts with the number of inputs equal to k or less. Finally, the elementary cut, composed of the node itself, is added to the set of cuts for the node.

This procedure is pretty fast for 5-feasible cuts, but it dramatically slows down on some "dense" networks when computing 6-feasible cuts. The problem is that there are too many cuts in this case. We should think how to heuristically trim the number of cuts in such cases, to have reasonable runtime.]

SideEffects []

SeeAlso []

Definition at line 130 of file fpgaCut.c.