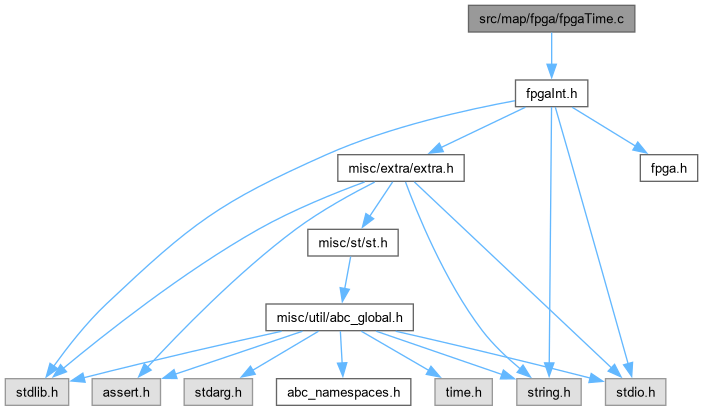

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

| ABC_NAMESPACE_IMPL_START float | Fpga_TimeCutComputeArrival (Fpga_Man_t *pMan, Fpga_Cut_t *pCut) |

| DECLARATIONS ///. | |

| float | Fpga_TimeCutComputeArrival_rec (Fpga_Man_t *pMan, Fpga_Cut_t *pCut) |

| float | Fpga_TimeComputeArrivalMax (Fpga_Man_t *p) |

| void | Fpga_TimeComputeRequiredGlobal (Fpga_Man_t *p, int fFirstTime) |

| void | Fpga_TimeComputeRequired (Fpga_Man_t *p, float fRequired) |

| void | Fpga_TimePropagateRequired (Fpga_Man_t *p, Fpga_NodeVec_t *vNodes) |

| void | Fpga_TimePropagateArrival (Fpga_Man_t *p) |

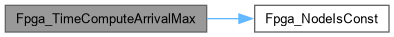

| float Fpga_TimeComputeArrivalMax | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Computes the maximum arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 89 of file fpgaTime.c.

| void Fpga_TimeComputeRequired | ( | Fpga_Man_t * | p, |

| float | fRequired ) |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 168 of file fpgaTime.c.

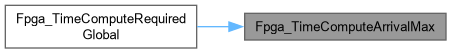

| void Fpga_TimeComputeRequiredGlobal | ( | Fpga_Man_t * | p, |

| int | fFirstTime ) |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 136 of file fpgaTime.c.

| ABC_NAMESPACE_IMPL_START float Fpga_TimeCutComputeArrival | ( | Fpga_Man_t * | pMan, |

| Fpga_Cut_t * | pCut ) |

DECLARATIONS ///.

CFile****************************************************************

FileName [fpgaTime.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Computes the arrival times of the cut.]

Description [Computes the maximum arrival time of the cut leaves and adds the delay of the LUT.]

SideEffects []

SeeAlso []

Definition at line 44 of file fpgaTime.c.

| float Fpga_TimeCutComputeArrival_rec | ( | Fpga_Man_t * | pMan, |

| Fpga_Cut_t * | pCut ) |

Function*************************************************************

Synopsis [Computes the arrival times of the cut recursively.]

Description [When computing the arrival time for the previously unused cuts, their arrival time may be incorrect because their fanins have incorrect arrival time. This procedure is called to fix this problem.]

SideEffects []

SeeAlso []

Definition at line 69 of file fpgaTime.c.

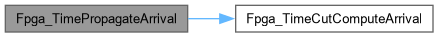

| void Fpga_TimePropagateArrival | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 245 of file fpgaTime.c.

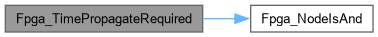

| void Fpga_TimePropagateRequired | ( | Fpga_Man_t * | p, |

| Fpga_NodeVec_t * | vNodes ) |

Function*************************************************************

Synopsis [Computes the required times of the given nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 205 of file fpgaTime.c.