Go to the source code of this file.

Functions | |

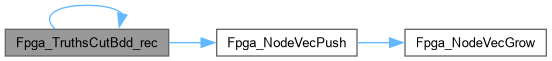

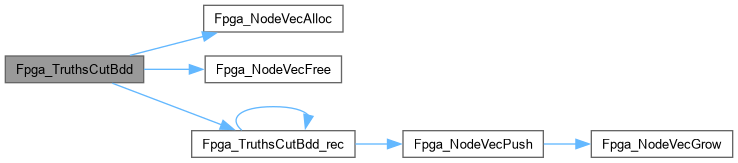

| ABC_NAMESPACE_IMPL_START DdNode * | Fpga_TruthsCutBdd_rec (DdManager *dd, Fpga_Cut_t *pCut, Fpga_NodeVec_t *vVisited) |

| DECLARATIONS ///. | |

| void * | Fpga_TruthsCutBdd (void *dd, Fpga_Cut_t *pCut) |

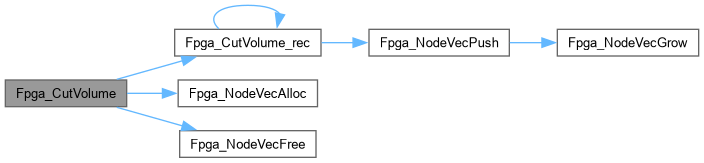

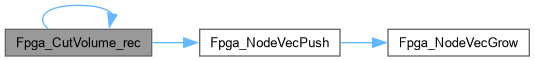

| void | Fpga_CutVolume_rec (Fpga_Cut_t *pCut, Fpga_NodeVec_t *vVisited) |

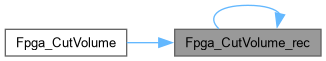

| int | Fpga_CutVolume (Fpga_Cut_t *pCut) |

| int Fpga_CutVolume | ( | Fpga_Cut_t * | pCut | ) |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 140 of file fpgaTruth.c.

| void Fpga_CutVolume_rec | ( | Fpga_Cut_t * | pCut, |

| Fpga_NodeVec_t * | vVisited ) |

Function*************************************************************

Synopsis [Recursively derives the truth table for the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 118 of file fpgaTruth.c.

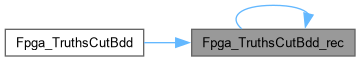

| void * Fpga_TruthsCutBdd | ( | void * | dd, |

| Fpga_Cut_t * | pCut ) |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 79 of file fpgaTruth.c.

| ABC_NAMESPACE_IMPL_START DdNode * Fpga_TruthsCutBdd_rec | ( | DdManager * | dd, |

| Fpga_Cut_t * | pCut, | ||

| Fpga_NodeVec_t * | vVisited ) |

DECLARATIONS ///.

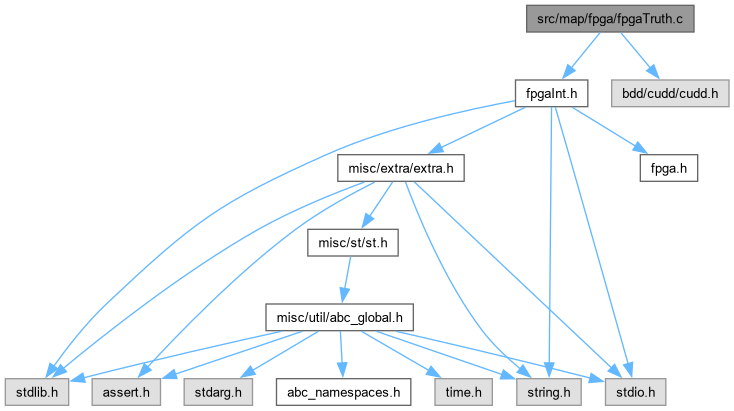

CFile****************************************************************

FileName [fpgaTruth.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Recursively derives the truth table for the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 44 of file fpgaTruth.c.