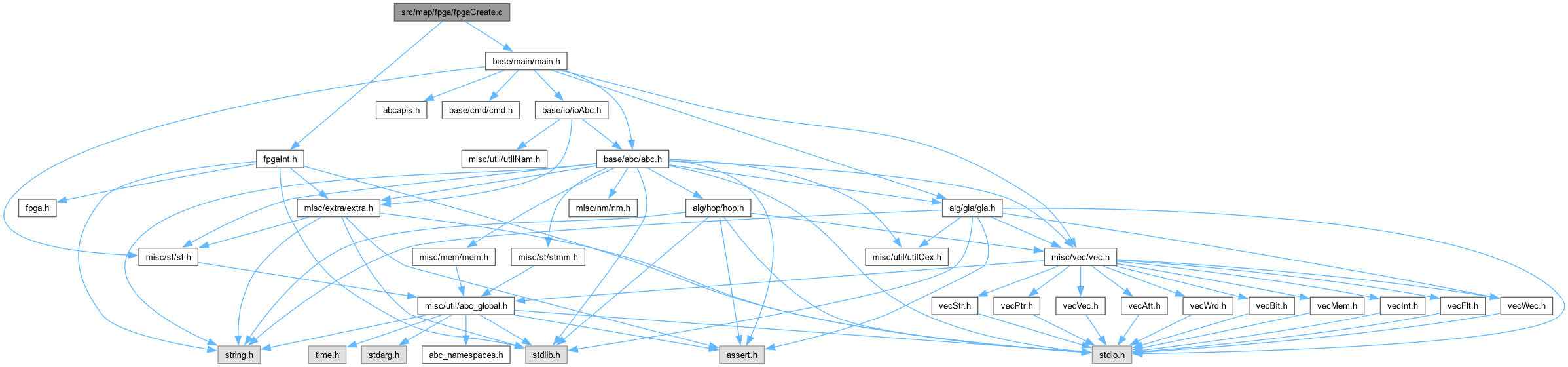

Go to the source code of this file.

| Fpga_Node_t ** Fpga_CutReadLeaves | ( | Fpga_Cut_t * | p | ) |

Definition at line 142 of file fpgaCreate.c.

| int Fpga_CutReadLeavesNum | ( | Fpga_Cut_t * | p | ) |

Function*************************************************************

Synopsis [Reads parameters from the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 141 of file fpgaCreate.c.

| int Fpga_LibReadLutMax | ( | Fpga_LutLib_t * | pLib | ) |

Function*************************************************************

Synopsis [Reads the parameters of the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 86 of file fpgaCreate.c.

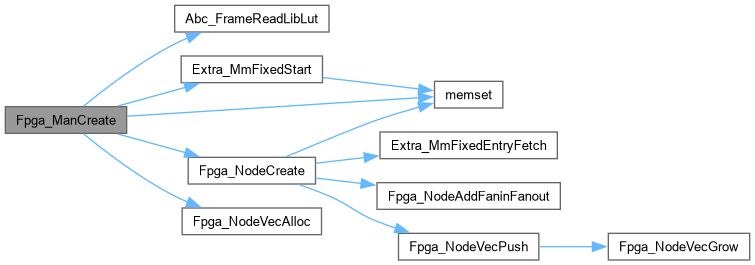

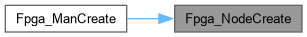

| Fpga_Man_t * Fpga_ManCreate | ( | int | nInputs, |

| int | nOutputs, | ||

| int | fVerbose ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Create the mapping manager.]

Description [The number of inputs and outputs is assumed to be known is advance. It is much simpler to have them fixed upfront. When it comes to representing the object graph in the form of AIG, the resulting manager is similar to the regular AIG manager, except that it does not use reference counting (and therefore does not have garbage collections). It does have table resizing. The data structure is more flexible to represent additional information needed for mapping.]

SideEffects []

SeeAlso []

Definition at line 163 of file fpgaCreate.c.

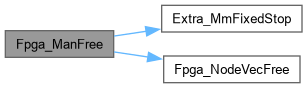

| void Fpga_ManFree | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Deallocates the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 217 of file fpgaCreate.c.

| void Fpga_ManPrintTimeStats | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints runtime statistics of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 252 of file fpgaCreate.c.

| Fpga_Node_t * Fpga_ManReadConst1 | ( | Fpga_Man_t * | p | ) |

Definition at line 55 of file fpgaCreate.c.

| float * Fpga_ManReadInputArrivals | ( | Fpga_Man_t * | p | ) |

Definition at line 56 of file fpgaCreate.c.

| int Fpga_ManReadInputNum | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Reads parameters of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 51 of file fpgaCreate.c.

| Fpga_Node_t ** Fpga_ManReadInputs | ( | Fpga_Man_t * | p | ) |

Definition at line 53 of file fpgaCreate.c.

| float * Fpga_ManReadLutAreas | ( | Fpga_Man_t * | p | ) |

Definition at line 59 of file fpgaCreate.c.

| Fpga_NodeVec_t * Fpga_ManReadMapping | ( | Fpga_Man_t * | p | ) |

Definition at line 60 of file fpgaCreate.c.

| int Fpga_ManReadOutputNum | ( | Fpga_Man_t * | p | ) |

Definition at line 52 of file fpgaCreate.c.

| Fpga_Node_t ** Fpga_ManReadOutputs | ( | Fpga_Man_t * | p | ) |

Definition at line 54 of file fpgaCreate.c.

| int Fpga_ManReadVarMax | ( | Fpga_Man_t * | p | ) |

Definition at line 58 of file fpgaCreate.c.

| int Fpga_ManReadVerbose | ( | Fpga_Man_t * | p | ) |

Definition at line 57 of file fpgaCreate.c.

| void Fpga_ManSetAreaLimit | ( | Fpga_Man_t * | p, |

| float | AreaLimit ) |

Definition at line 65 of file fpgaCreate.c.

| void Fpga_ManSetAreaRecovery | ( | Fpga_Man_t * | p, |

| int | fAreaRecovery ) |

Definition at line 63 of file fpgaCreate.c.

| void Fpga_ManSetChoiceNodeNum | ( | Fpga_Man_t * | p, |

| int | nChoiceNodes ) |

Definition at line 66 of file fpgaCreate.c.

| void Fpga_ManSetChoiceNum | ( | Fpga_Man_t * | p, |

| int | nChoices ) |

Definition at line 67 of file fpgaCreate.c.

| void Fpga_ManSetDelayLimit | ( | Fpga_Man_t * | p, |

| float | DelayLimit ) |

Definition at line 64 of file fpgaCreate.c.

| void Fpga_ManSetDelayTarget | ( | Fpga_Man_t * | p, |

| float | DelayTarget ) |

Definition at line 72 of file fpgaCreate.c.

| void Fpga_ManSetInputArrivals | ( | Fpga_Man_t * | p, |

| float * | pArrivals ) |

Definition at line 62 of file fpgaCreate.c.

| void Fpga_ManSetLatchNum | ( | Fpga_Man_t * | p, |

| int | nLatches ) |

Definition at line 71 of file fpgaCreate.c.

| void Fpga_ManSetLatchPaths | ( | Fpga_Man_t * | p, |

| int | fLatchPaths ) |

Definition at line 70 of file fpgaCreate.c.

| void Fpga_ManSetName | ( | Fpga_Man_t * | p, |

| char * | pFileName ) |

Definition at line 73 of file fpgaCreate.c.

| void Fpga_ManSetOutputNames | ( | Fpga_Man_t * | p, |

| char ** | ppNames ) |

Definition at line 61 of file fpgaCreate.c.

| void Fpga_ManSetSwitching | ( | Fpga_Man_t * | p, |

| int | fSwitching ) |

Definition at line 69 of file fpgaCreate.c.

| void Fpga_ManSetVerbose | ( | Fpga_Man_t * | p, |

| int | fVerbose ) |

Definition at line 68 of file fpgaCreate.c.

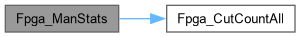

| void Fpga_ManStats | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints some interesting stats.]

Description []

SideEffects []

SeeAlso []

Definition at line 564 of file fpgaCreate.c.

| Fpga_Node_t * Fpga_NodeAnd | ( | Fpga_Man_t * | p, |

| Fpga_Node_t * | p1, | ||

| Fpga_Node_t * | p2 ) |

Function*************************************************************

Synopsis [Elementary AND operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 470 of file fpgaCreate.c.

| int Fpga_NodeComparePhase | ( | Fpga_Node_t * | p1, |

| Fpga_Node_t * | p2 ) |

Definition at line 128 of file fpgaCreate.c.

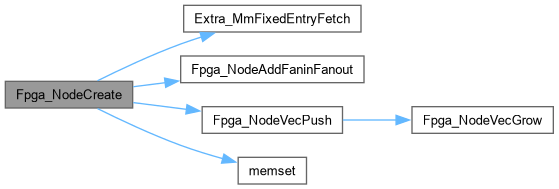

| Fpga_Node_t * Fpga_NodeCreate | ( | Fpga_Man_t * | p, |

| Fpga_Node_t * | p1, | ||

| Fpga_Node_t * | p2 ) |

Function*************************************************************

Synopsis [Creates a new node.]

Description [This procedure should be called to create the constant node and the PI nodes first.]

SideEffects []

SeeAlso []

Definition at line 293 of file fpgaCreate.c.

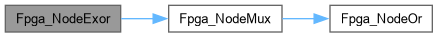

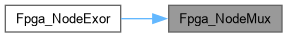

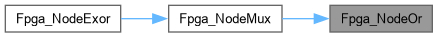

| Fpga_Node_t * Fpga_NodeExor | ( | Fpga_Man_t * | p, |

| Fpga_Node_t * | p1, | ||

| Fpga_Node_t * | p2 ) |

Function*************************************************************

Synopsis [Elementary EXOR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 506 of file fpgaCreate.c.

| int Fpga_NodeIsAnd | ( | Fpga_Node_t * | p | ) |

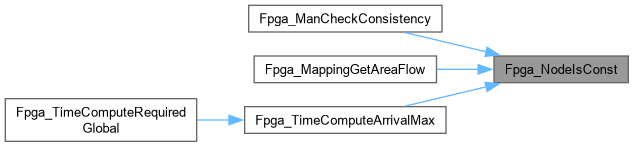

| int Fpga_NodeIsConst | ( | Fpga_Node_t * | p | ) |

Function*************************************************************

Synopsis [Checks the type of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 125 of file fpgaCreate.c.

| int Fpga_NodeIsVar | ( | Fpga_Node_t * | p | ) |

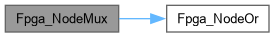

| Fpga_Node_t * Fpga_NodeMux | ( | Fpga_Man_t * | p, |

| Fpga_Node_t * | pC, | ||

| Fpga_Node_t * | pT, | ||

| Fpga_Node_t * | pE ) |

Function*************************************************************

Synopsis [Elementary MUX operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 522 of file fpgaCreate.c.

| Fpga_Node_t * Fpga_NodeOr | ( | Fpga_Man_t * | p, |

| Fpga_Node_t * | p1, | ||

| Fpga_Node_t * | p2 ) |

Function*************************************************************

Synopsis [Elementary OR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 488 of file fpgaCreate.c.

| Fpga_Cut_t * Fpga_NodeReadCutBest | ( | Fpga_Node_t * | p | ) |

Definition at line 105 of file fpgaCreate.c.

| Fpga_Cut_t * Fpga_NodeReadCuts | ( | Fpga_Node_t * | p | ) |

Definition at line 104 of file fpgaCreate.c.

| char * Fpga_NodeReadData0 | ( | Fpga_Node_t * | p | ) |

Function*************************************************************

Synopsis [Reads parameters of the mapping node.]

Description []

SideEffects []

SeeAlso []

Definition at line 99 of file fpgaCreate.c.

| Fpga_Node_t * Fpga_NodeReadData1 | ( | Fpga_Node_t * | p | ) |

Definition at line 100 of file fpgaCreate.c.

| int Fpga_NodeReadLevel | ( | Fpga_Node_t * | p | ) |

Definition at line 103 of file fpgaCreate.c.

| int Fpga_NodeReadNum | ( | Fpga_Node_t * | p | ) |

Definition at line 102 of file fpgaCreate.c.

| Fpga_Node_t * Fpga_NodeReadOne | ( | Fpga_Node_t * | p | ) |

Definition at line 106 of file fpgaCreate.c.

| int Fpga_NodeReadRefs | ( | Fpga_Node_t * | p | ) |

Definition at line 101 of file fpgaCreate.c.

| Fpga_Node_t * Fpga_NodeReadTwo | ( | Fpga_Node_t * | p | ) |

Definition at line 107 of file fpgaCreate.c.

| void Fpga_NodeSetChoice | ( | Fpga_Man_t * | pMan, |

| Fpga_Node_t * | pNodeOld, | ||

| Fpga_Node_t * | pNodeNew ) |

Function*************************************************************

Synopsis [Sets the node to be equivalent to the given one.]

Description [This procedure is a work-around for the equivalence check. Does not verify the equivalence. Use at the user's risk.]

SideEffects []

SeeAlso []

Definition at line 544 of file fpgaCreate.c.

| void Fpga_NodeSetData0 | ( | Fpga_Node_t * | p, |

| char * | pData ) |

Definition at line 108 of file fpgaCreate.c.

| void Fpga_NodeSetData1 | ( | Fpga_Node_t * | p, |

| Fpga_Node_t * | pNode ) |

Definition at line 109 of file fpgaCreate.c.

| void Fpga_NodeSetNextE | ( | Fpga_Node_t * | p, |

| Fpga_Node_t * | pNextE ) |

Definition at line 110 of file fpgaCreate.c.

| void Fpga_NodeSetRepr | ( | Fpga_Node_t * | p, |

| Fpga_Node_t * | pRepr ) |

Definition at line 111 of file fpgaCreate.c.

| void Fpga_NodeSetSwitching | ( | Fpga_Node_t * | p, |

| float | Switching ) |

Definition at line 112 of file fpgaCreate.c.