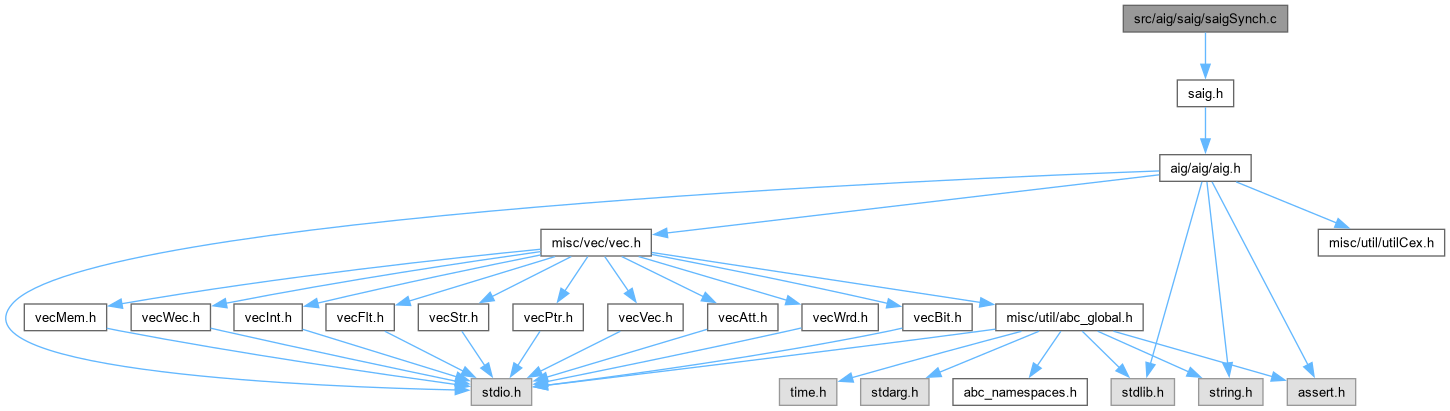

#include "saig.h"

Go to the source code of this file.

Function*************************************************************

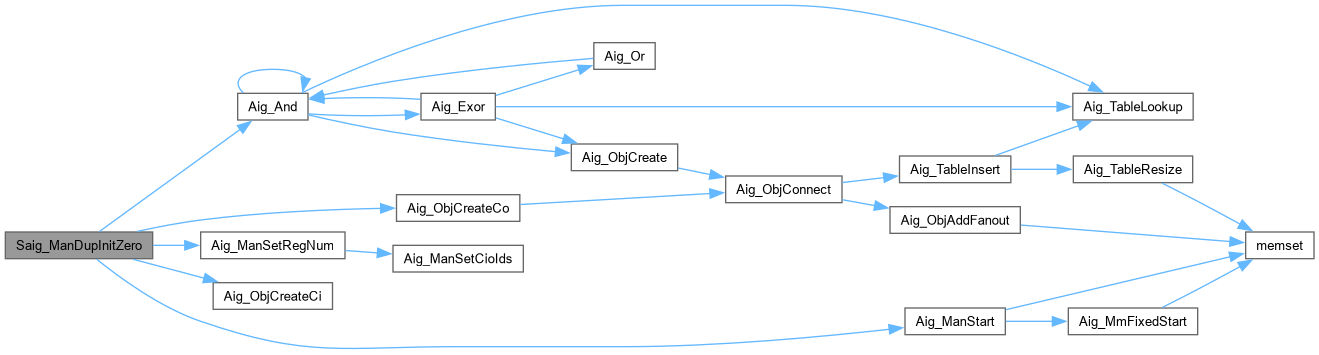

Synopsis [Duplicates the AIG to have constant-0 initial state.]

Description []

SideEffects []

SeeAlso []

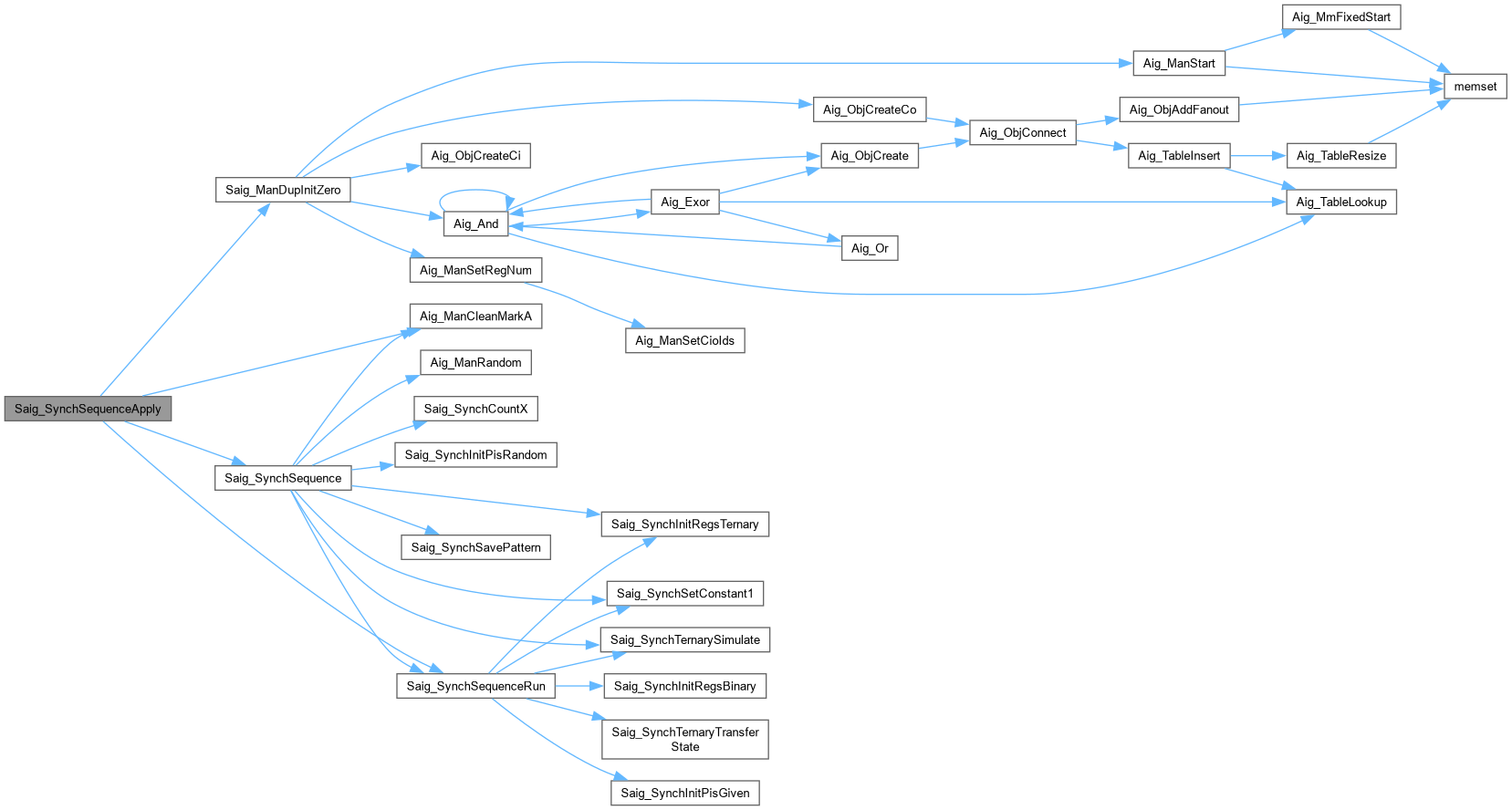

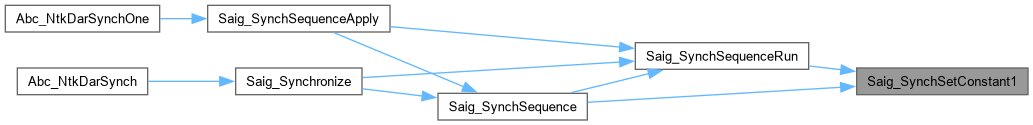

Definition at line 468 of file saigSynch.c.

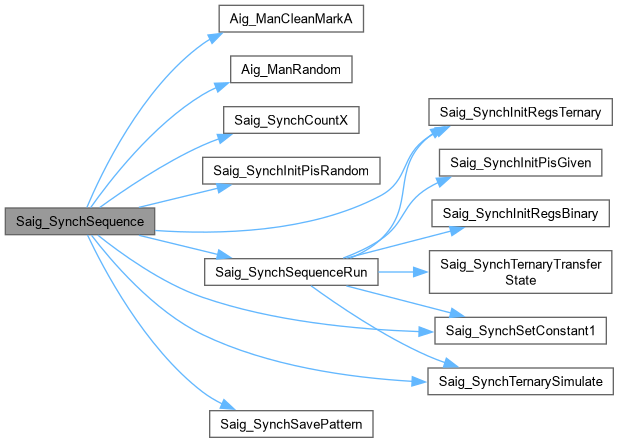

Function*************************************************************

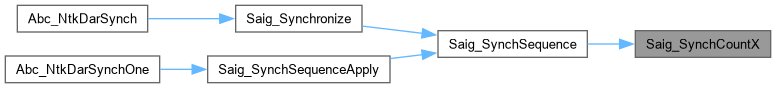

Synopsis [Returns the number of Xs in the smallest ternary pattern.]

Description [Returns the number of this pattern.]

SideEffects []

SeeAlso []

Definition at line 279 of file saigSynch.c.

Function*************************************************************

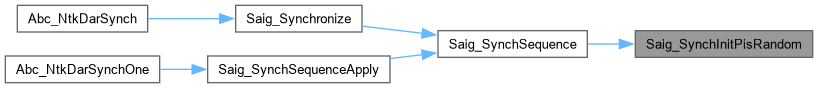

Synopsis [Initializes random binary primary inputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 169 of file saigSynch.c.

Function*************************************************************

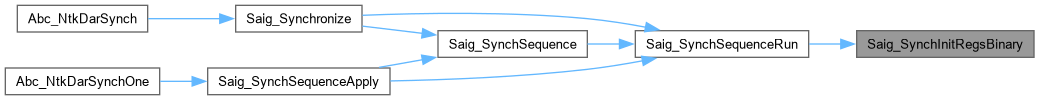

Synopsis [Initializes random binary primary inputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 145 of file saigSynch.c.

Function*************************************************************

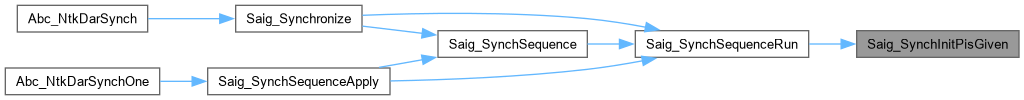

Synopsis [Initializes registers to the given binary state.]

Description [The binary state is stored in pObj->fMarkA.]

SideEffects []

SeeAlso []

Definition at line 121 of file saigSynch.c.

Function*************************************************************

Synopsis [Initializes registers to the ternary state.]

Description []

SideEffects []

SeeAlso []

Definition at line 97 of file saigSynch.c.

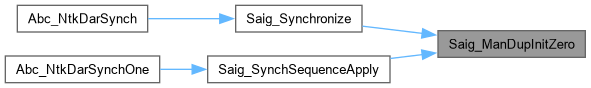

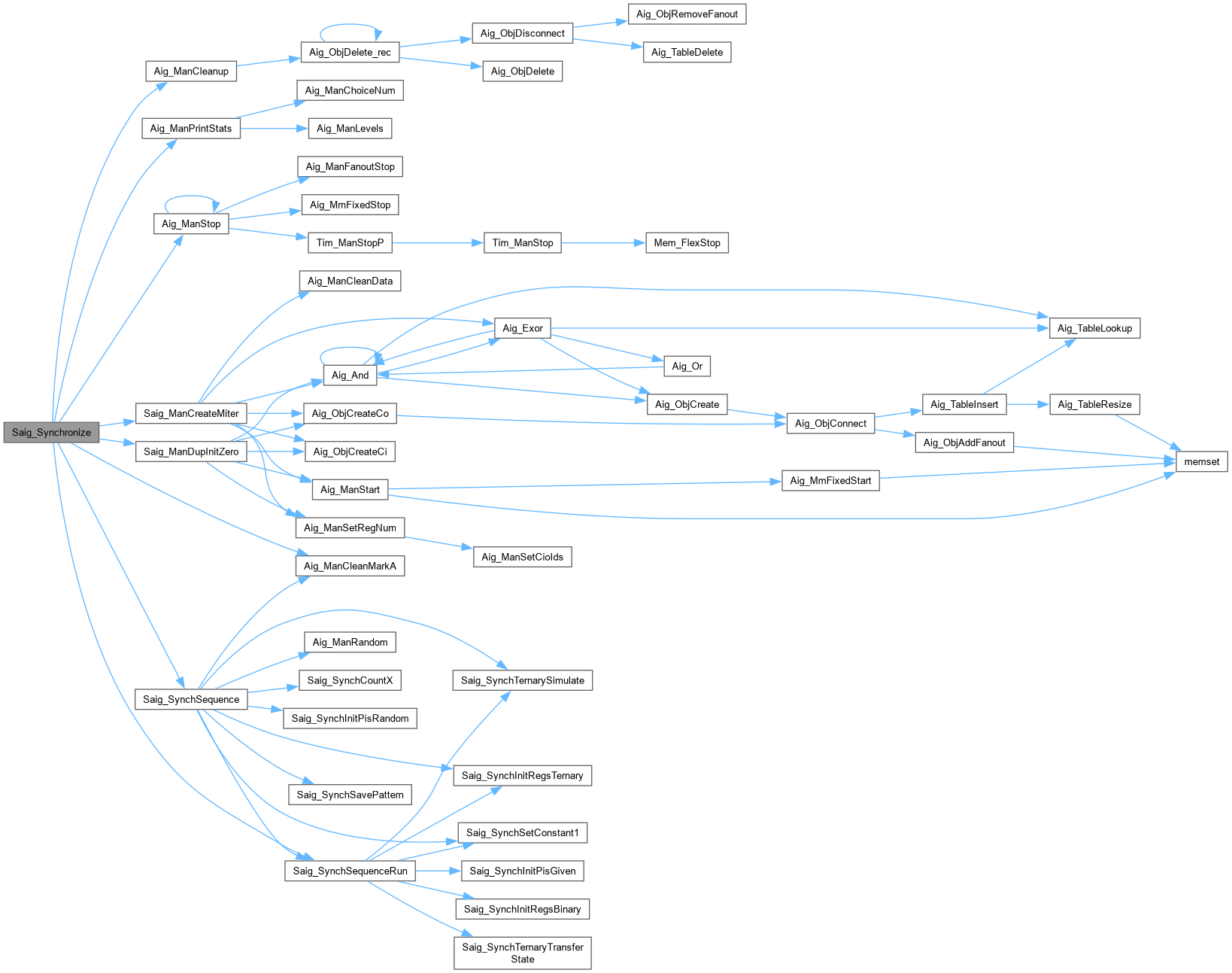

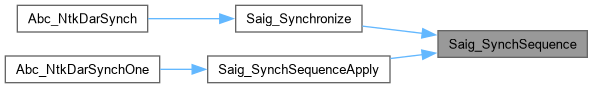

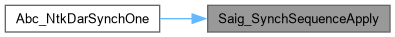

Function*************************************************************

Synopsis [Creates SEC miter for two designs without initial state.]

Description [The designs (pAig1 and pAig2) are assumed to have ternary initial state. Determines synchronizing sequences using ternary simulation. Simulates the sequences on both designs to come up with equivalent binary initial states. Create seq miter for the designs starting in these states.]

SideEffects []

SeeAlso []

Definition at line 556 of file saigSynch.c.

| int Saig_SynchSavePattern | ( | Aig_Man_t * | pAig, |

| Vec_Ptr_t * | vSimInfo, | ||

| int | nWords, | ||

| int | iPat, | ||

| Vec_Str_t * | vSequence ) |

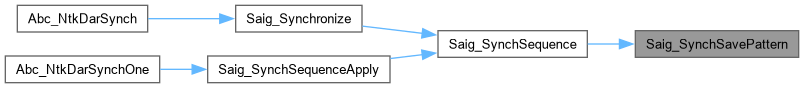

Function*************************************************************

Synopsis [Saves the best pattern found and initializes the registers.]

Description []

SideEffects []

SeeAlso []

Definition at line 322 of file saigSynch.c.

Function*************************************************************

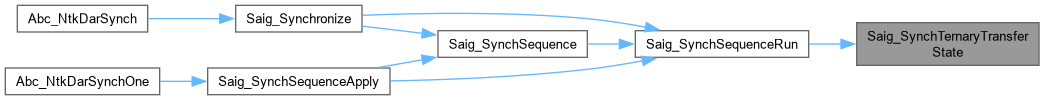

Synopsis [Determines synchronizing sequence using ternary simulation.]

Description []

SideEffects []

SeeAlso []

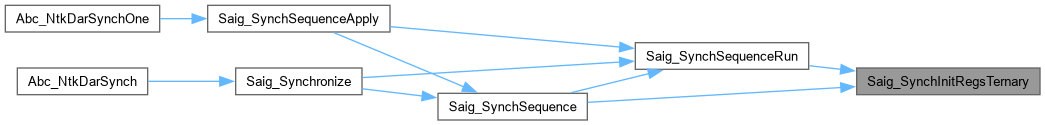

Definition at line 403 of file saigSynch.c.

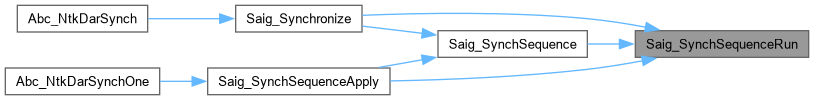

Function*************************************************************

Synopsis [Determines synchronizing sequence using ternary simulation.]

Description []

SideEffects []

SeeAlso []

Definition at line 502 of file saigSynch.c.

| int Saig_SynchSequenceRun | ( | Aig_Man_t * | pAig, |

| Vec_Ptr_t * | vSimInfo, | ||

| Vec_Str_t * | vSequence, | ||

| int | fTernary ) |

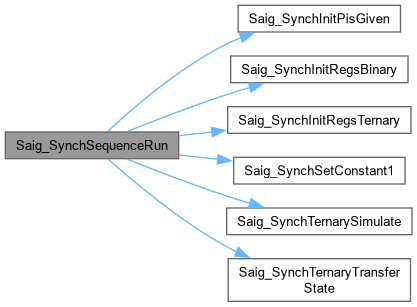

Function*************************************************************

Synopsis [Implement synchronizing sequence.]

Description []

SideEffects []

SeeAlso []

Definition at line 361 of file saigSynch.c.

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Initializes registers to the ternary state.]

Description []

SideEffects []

SeeAlso []

Definition at line 75 of file saigSynch.c.

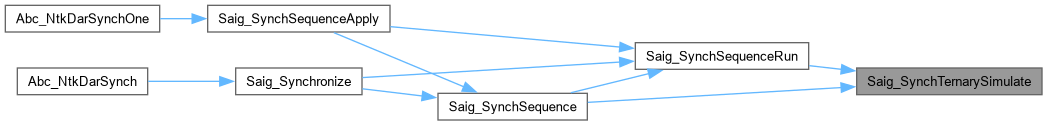

Function*************************************************************

Synopsis [Performs ternary simulation of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 193 of file saigSynch.c.

Function*************************************************************

Synopsis [Performs ternary simulation of the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 254 of file saigSynch.c.