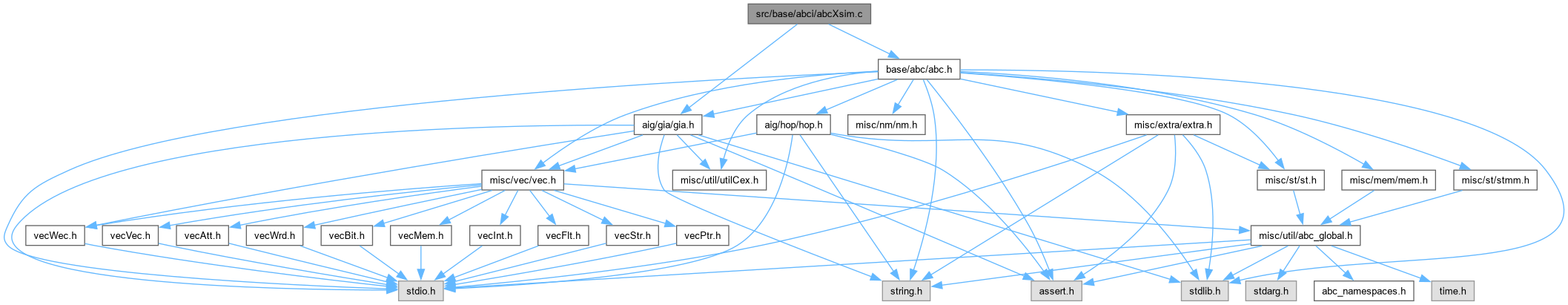

Go to the source code of this file.

Macros | |

| #define | XVS0 ABC_INIT_ZERO |

| DECLARATIONS ///. | |

| #define | XVS1 ABC_INIT_ONE |

| #define | XVSX ABC_INIT_DC |

Functions | |

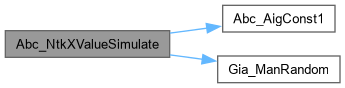

| void | Abc_NtkXValueSimulate (Abc_Ntk_t *pNtk, int nFrames, int fXInputs, int fXState, int fVerbose) |

| FUNCTION DEFINITIONS ///. | |

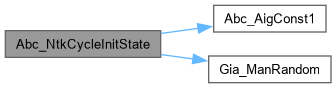

| void | Abc_NtkCycleInitState (Abc_Ntk_t *pNtk, int nFrames, int fUseXval, int fVerbose) |

| #define XVS0 ABC_INIT_ZERO |

DECLARATIONS ///.

CFile****************************************************************

FileName [abcXsim.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Using X-valued simulation.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

| #define XVS1 ABC_INIT_ONE |

| #define XVSX ABC_INIT_DC |

| void Abc_NtkCycleInitState | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | fUseXval, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Cycles the circuit to create a new initial state.]

Description [Simulates the circuit with random (or ternary) input for the given number of timeframes to get a better initial state.]

SideEffects []

SeeAlso []

Definition at line 192 of file abcXsim.c.

| void Abc_NtkXValueSimulate | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | fXInputs, | ||

| int | fXState, | ||

| int | fVerbose ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Performs X-valued simulation of the sequential network.]

Description []

SideEffects []

SeeAlso []

Definition at line 111 of file abcXsim.c.