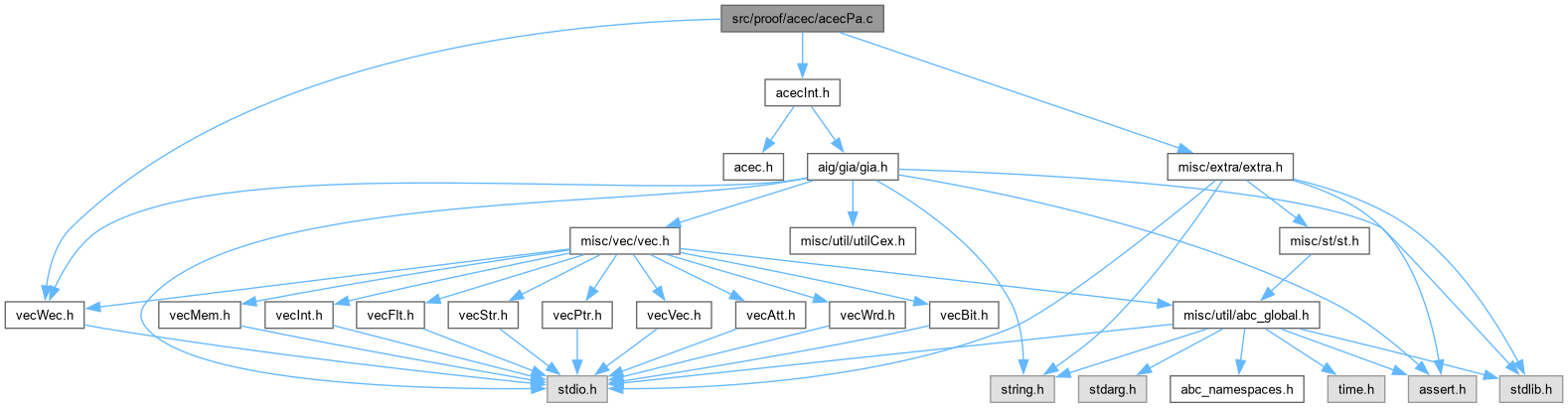

Go to the source code of this file.

Functions | |

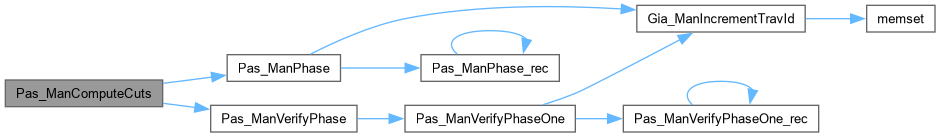

| ABC_NAMESPACE_IMPL_START int | Pas_ManVerifyPhaseOne_rec (Gia_Man_t *p, Gia_Obj_t *pObj) |

| DECLARATIONS ///. | |

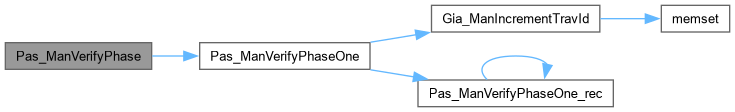

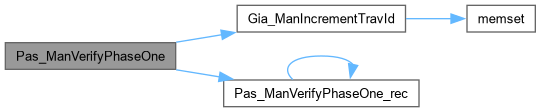

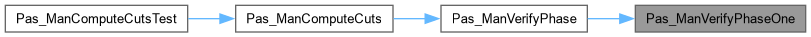

| void | Pas_ManVerifyPhaseOne (Gia_Man_t *p, Vec_Int_t *vAdds, int iBox, Vec_Bit_t *vPhase) |

| void | Pas_ManVerifyPhase (Gia_Man_t *p, Vec_Int_t *vAdds, Vec_Int_t *vOrder, Vec_Bit_t *vPhase) |

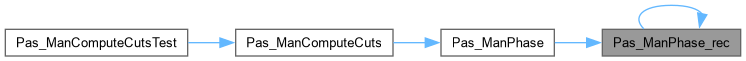

| void | Pas_ManPhase_rec (Gia_Man_t *p, Vec_Int_t *vAdds, Vec_Int_t *vMap, Gia_Obj_t *pObj, int fPhase, Vec_Bit_t *vPhase, Vec_Bit_t *vConstPhase) |

| Vec_Bit_t * | Pas_ManPhase (Gia_Man_t *p, Vec_Int_t *vAdds, Vec_Int_t *vMap, Vec_Int_t *vRoots, Vec_Bit_t **pvConstPhase) |

| int | Pas_ManComputeCuts (Gia_Man_t *p, Vec_Int_t *vAdds, Vec_Int_t *vOrder, Vec_Int_t *vIns, Vec_Int_t *vOuts) |

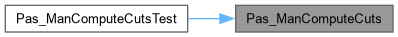

| void | Pas_ManComputeCutsTest (Gia_Man_t *p) |

| int Pas_ManComputeCuts | ( | Gia_Man_t * | p, |

| Vec_Int_t * | vAdds, | ||

| Vec_Int_t * | vOrder, | ||

| Vec_Int_t * | vIns, | ||

| Vec_Int_t * | vOuts ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 176 of file acecPa.c.

| void Pas_ManComputeCutsTest | ( | Gia_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 249 of file acecPa.c.

| Vec_Bit_t * Pas_ManPhase | ( | Gia_Man_t * | p, |

| Vec_Int_t * | vAdds, | ||

| Vec_Int_t * | vMap, | ||

| Vec_Int_t * | vRoots, | ||

| Vec_Bit_t ** | pvConstPhase ) |

Definition at line 153 of file acecPa.c.

| void Pas_ManPhase_rec | ( | Gia_Man_t * | p, |

| Vec_Int_t * | vAdds, | ||

| Vec_Int_t * | vMap, | ||

| Gia_Obj_t * | pObj, | ||

| int | fPhase, | ||

| Vec_Bit_t * | vPhase, | ||

| Vec_Bit_t * | vConstPhase ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 122 of file acecPa.c.

| void Pas_ManVerifyPhase | ( | Gia_Man_t * | p, |

| Vec_Int_t * | vAdds, | ||

| Vec_Int_t * | vOrder, | ||

| Vec_Bit_t * | vPhase ) |

Definition at line 104 of file acecPa.c.

Definition at line 61 of file acecPa.c.

| ABC_NAMESPACE_IMPL_START int Pas_ManVerifyPhaseOne_rec | ( | Gia_Man_t * | p, |

| Gia_Obj_t * | pObj ) |

DECLARATIONS ///.

CFile****************************************************************

FileName [acecPa.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [CEC for arithmetic circuits.]

Synopsis [Core procedures.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 47 of file acecPa.c.