Go to the source code of this file.

Classes | |

| struct | Cec_ManS_t_ |

Macros | |

| #define | SIM_RANDS 113 |

| DECLARATIONS ///. | |

Typedefs | |

| typedef struct Cec_ManS_t_ | Cec_ManS_t |

Functions | |

| Cec_ManS_t * | Cec_ManSStart (Gia_Man_t *pAig, int nWords) |

| FUNCTION DEFINITIONS ///. | |

| void | Cec_ManSStop (Cec_ManS_t *p) |

| int | Cec_ManSVerify_rec (Gia_Man_t *p, int iObj) |

| void | Cec_ManSVerifyTwo (Gia_Man_t *p, int iObj0, int iObj1) |

| void | Cec_ManSVerify (Cec_ManS_t *p, int iObj0, int iObj1) |

| void | Cec_ManSRunImply (Cec_ManS_t *p, int iNode) |

| int | Cec_ManSRunPropagate (Cec_ManS_t *p, int iNode) |

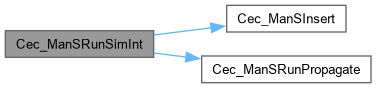

| void | Cec_ManSInsert (Cec_ManS_t *p, int iNode) |

| int | Cec_ManSRunSimInt (Cec_ManS_t *p) |

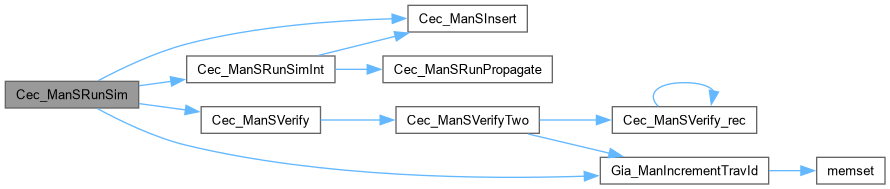

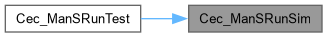

| int | Cec_ManSRunSim (Cec_ManS_t *p, int iNode0, int iNode1) |

| void | Cec_ManSRunTest (Gia_Man_t *pAig) |

| #define SIM_RANDS 113 |

DECLARATIONS ///.

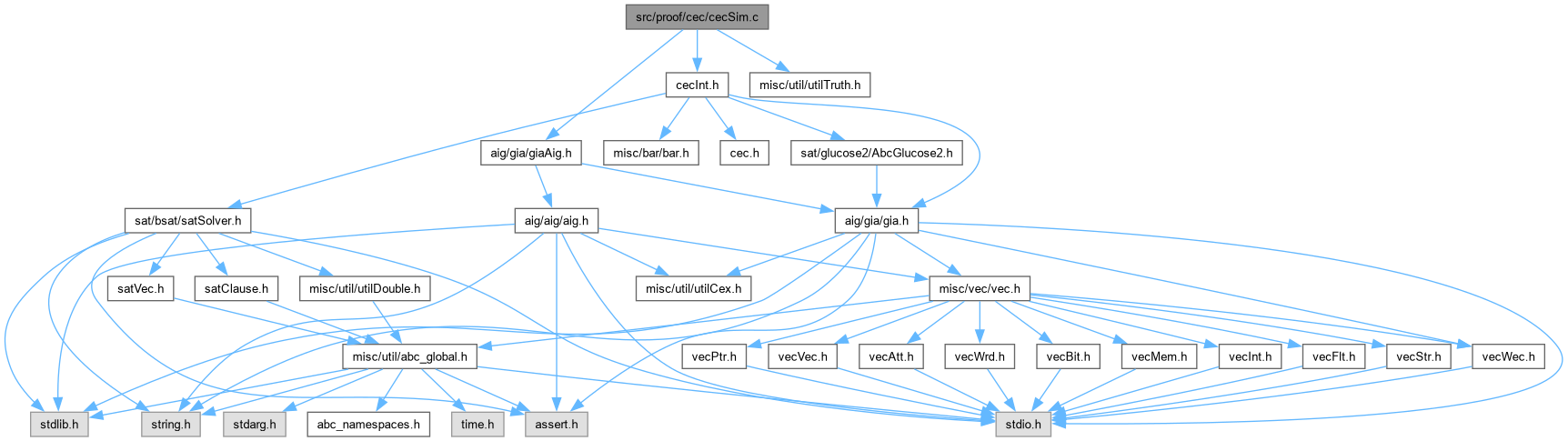

CFile****************************************************************

FileName [cecSim.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Combinational equivalence checking.]

Synopsis [Simulation.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

| typedef struct Cec_ManS_t_ Cec_ManS_t |

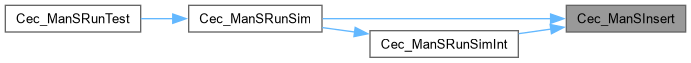

| void Cec_ManSInsert | ( | Cec_ManS_t * | p, |

| int | iNode ) |

Definition at line 282 of file cecSim.c.

| void Cec_ManSRunImply | ( | Cec_ManS_t * | p, |

| int | iNode ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 184 of file cecSim.c.

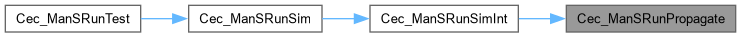

| int Cec_ManSRunPropagate | ( | Cec_ManS_t * | p, |

| int | iNode ) |

Definition at line 217 of file cecSim.c.

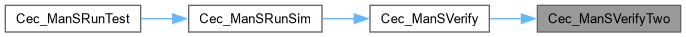

| int Cec_ManSRunSim | ( | Cec_ManS_t * | p, |

| int | iNode0, | ||

| int | iNode1 ) |

Definition at line 327 of file cecSim.c.

| int Cec_ManSRunSimInt | ( | Cec_ManS_t * | p | ) |

Definition at line 303 of file cecSim.c.

| void Cec_ManSRunTest | ( | Gia_Man_t * | pAig | ) |

Definition at line 383 of file cecSim.c.

| Cec_ManS_t * Cec_ManSStart | ( | Gia_Man_t * | pAig, |

| int | nWords ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 71 of file cecSim.c.

| void Cec_ManSStop | ( | Cec_ManS_t * | p | ) |

| void Cec_ManSVerify | ( | Cec_ManS_t * | p, |

| int | iObj0, | ||

| int | iObj1 ) |

Definition at line 134 of file cecSim.c.

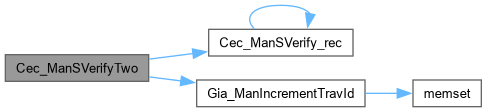

| int Cec_ManSVerify_rec | ( | Gia_Man_t * | p, |

| int | iObj ) |

Function*************************************************************

Synopsis [Verify counter-example.]

Description []

SideEffects []

SeeAlso []

Definition at line 108 of file cecSim.c.

| void Cec_ManSVerifyTwo | ( | Gia_Man_t * | p, |

| int | iObj0, | ||

| int | iObj1 ) |

Definition at line 123 of file cecSim.c.