Go to the source code of this file.

Functions | |

| void | Io_WriteVerilog (Abc_Ntk_t *pNtk, char *pFileName, int fOnlyAnds, int fNewInterface) |

| FUNCTION DEFINITIONS ///. | |

| void | Io_WriteLutModule (FILE *pFile, int nLutSize) |

| void | Io_WriteFixedModules (FILE *pFile) |

| void | Io_WriteVerilogObjectsLut (FILE *pFile, Abc_Ntk_t *pNtk, int nLutSize, int fFixed) |

| void | Io_WriteVerilogLutInt (FILE *pFile, Abc_Ntk_t *pNtk, int nLutSize, int fFixed, int fNewInterface) |

| void | Io_WriteVerilogLut (Abc_Ntk_t *pNtk, char *pFileName, int nLutSize, int fFixed, int fNoModules, int fNewInterface) |

| void Io_WriteFixedModules | ( | FILE * | pFile | ) |

Definition at line 743 of file ioWriteVerilog.c.

| void Io_WriteLutModule | ( | FILE * | pFile, |

| int | nLutSize ) |

Function*************************************************************

Synopsis [Write the network of K-input LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 737 of file ioWriteVerilog.c.

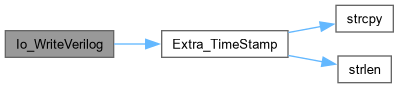

| void Io_WriteVerilog | ( | Abc_Ntk_t * | pNtk, |

| char * | pFileName, | ||

| int | fOnlyAnds, | ||

| int | fNewInterface ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Write verilog.]

Description []

SideEffects []

SeeAlso []

Definition at line 58 of file ioWriteVerilog.c.

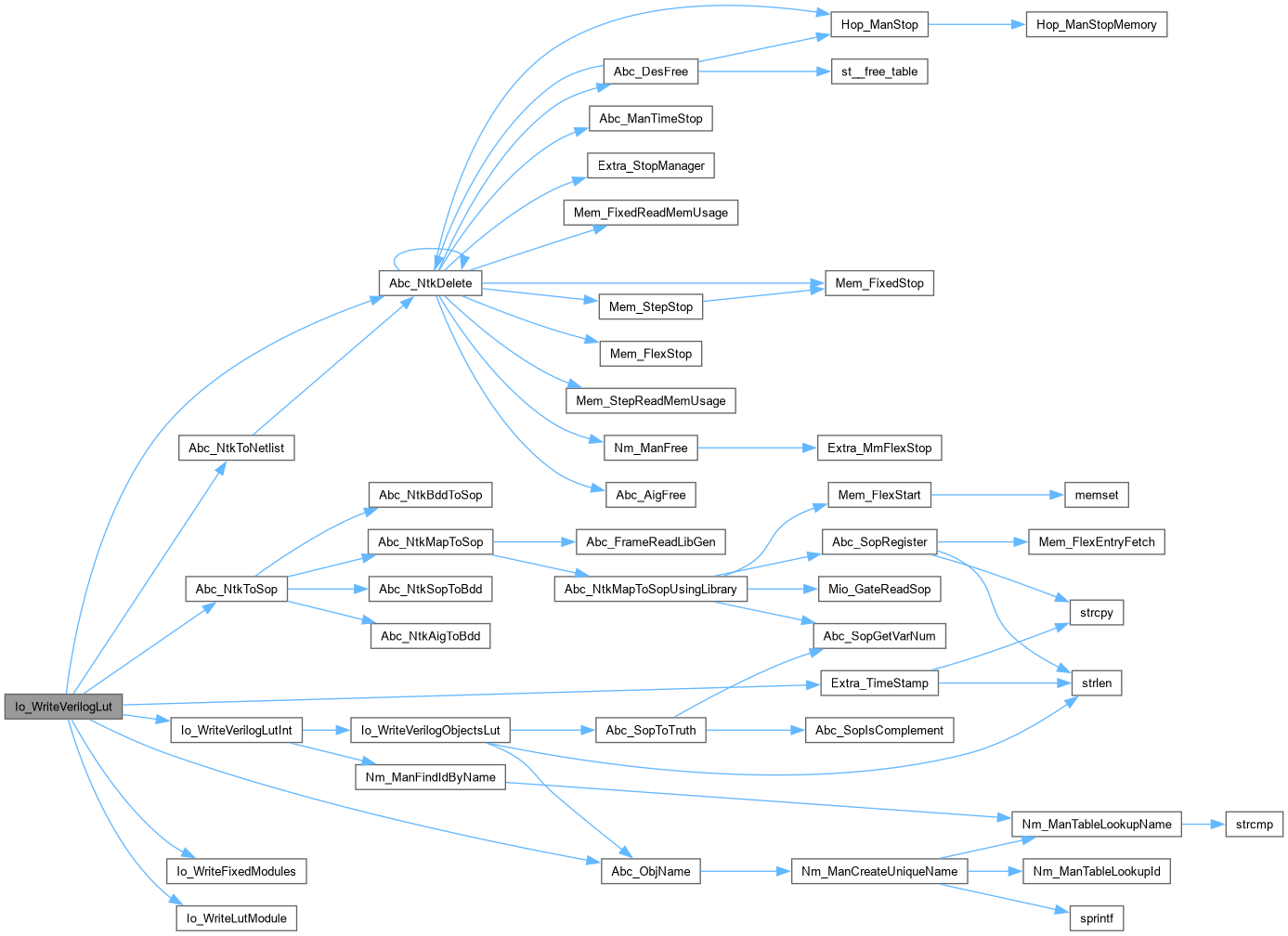

| void Io_WriteVerilogLut | ( | Abc_Ntk_t * | pNtk, |

| char * | pFileName, | ||

| int | nLutSize, | ||

| int | fFixed, | ||

| int | fNoModules, | ||

| int | fNewInterface ) |

Definition at line 923 of file ioWriteVerilog.c.

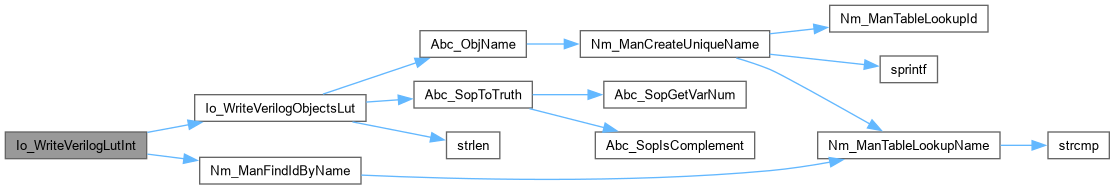

| void Io_WriteVerilogLutInt | ( | FILE * | pFile, |

| Abc_Ntk_t * | pNtk, | ||

| int | nLutSize, | ||

| int | fFixed, | ||

| int | fNewInterface ) |

Definition at line 859 of file ioWriteVerilog.c.

| void Io_WriteVerilogObjectsLut | ( | FILE * | pFile, |

| Abc_Ntk_t * | pNtk, | ||

| int | nLutSize, | ||

| int | fFixed ) |

Definition at line 775 of file ioWriteVerilog.c.