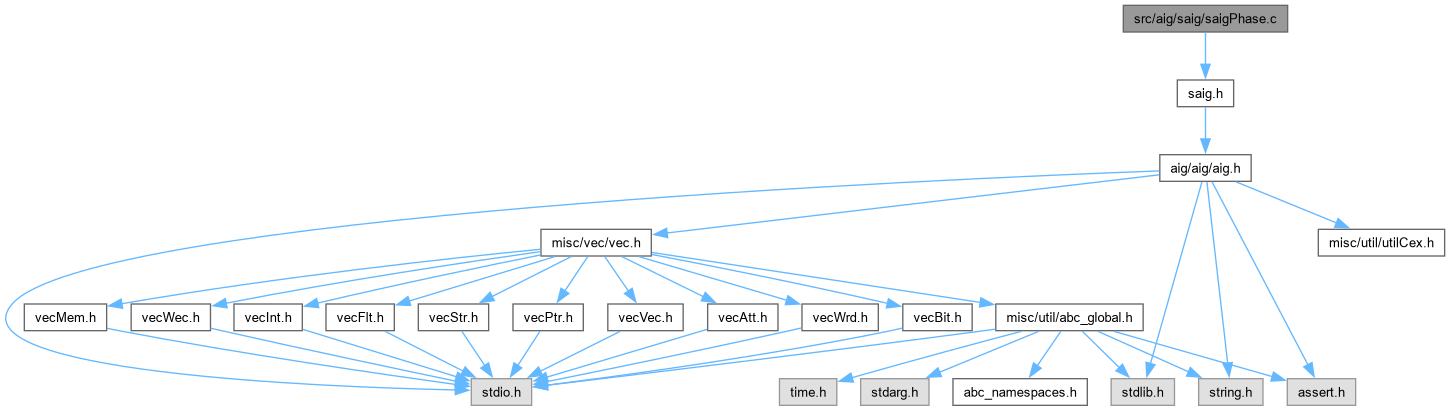

#include "saig.h"

Go to the source code of this file.

Classes | |

| struct | Saig_Tsim_t_ |

Macros | |

| #define | TSIM_MAX_ROUNDS 10000 |

| #define | TSIM_ONE_SERIES 3000 |

| #define | SAIG_XVS0 1 |

| #define | SAIG_XVS1 2 |

| #define | SAIG_XVSX 3 |

Typedefs | |

| typedef struct Saig_Tsim_t_ | Saig_Tsim_t |

| #define SAIG_XVS0 1 |

Definition at line 36 of file saigPhase.c.

| #define SAIG_XVS1 2 |

Definition at line 37 of file saigPhase.c.

| #define SAIG_XVSX 3 |

Definition at line 38 of file saigPhase.c.

| #define TSIM_MAX_ROUNDS 10000 |

CFile****************************************************************

FileName [saigPhase.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Sequential AIG package.]

Synopsis [Automated phase abstraction.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

Definition at line 33 of file saigPhase.c.

| #define TSIM_ONE_SERIES 3000 |

Definition at line 34 of file saigPhase.c.

| typedef struct Saig_Tsim_t_ Saig_Tsim_t |

Definition at line 103 of file saigPhase.c.

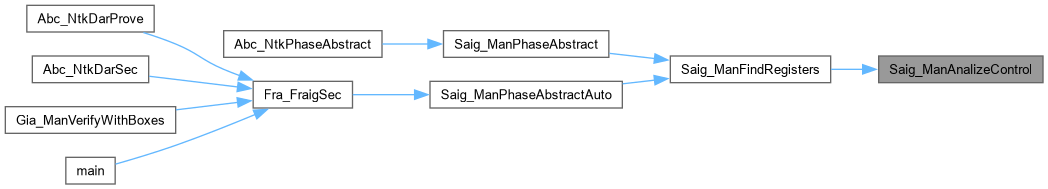

| void Saig_ManAnalizeControl | ( | Aig_Man_t * | p, |

| int | Reg ) |

Function*************************************************************

Synopsis [Analize initial value of the selected register.]

Description []

SideEffects []

SeeAlso []

Definition at line 612 of file saigPhase.c.

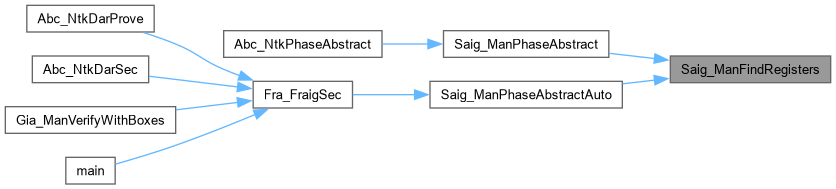

| int Saig_ManFindRegisters | ( | Saig_Tsim_t * | pTsi, |

| int | nFrames, | ||

| int | fIgnore, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Finds the registers to phase-abstract.]

Description []

SideEffects []

SeeAlso []

Definition at line 666 of file saigPhase.c.

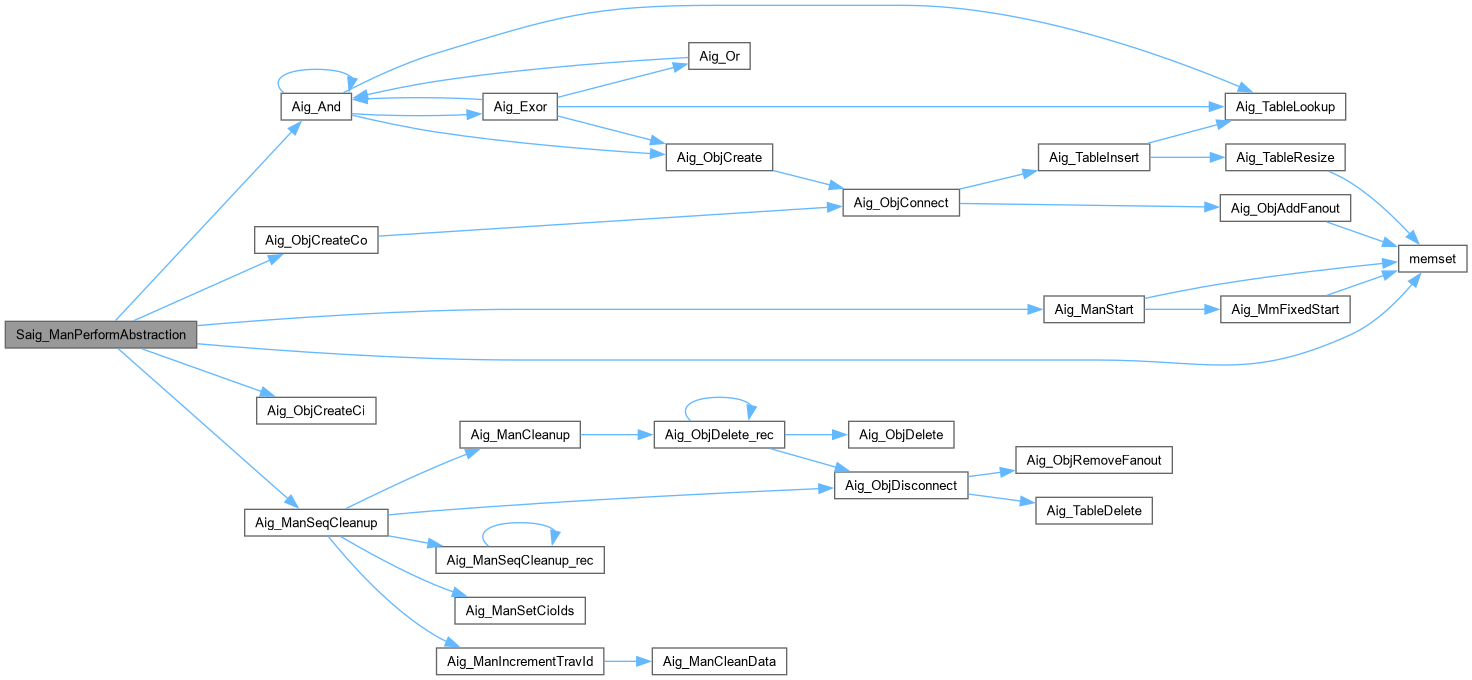

| Aig_Man_t * Saig_ManPerformAbstraction | ( | Saig_Tsim_t * | pTsi, |

| int | nFrames, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs phase abstraction by unrolling the circuit.]

Description []

SideEffects []

SeeAlso []

Definition at line 748 of file saigPhase.c.

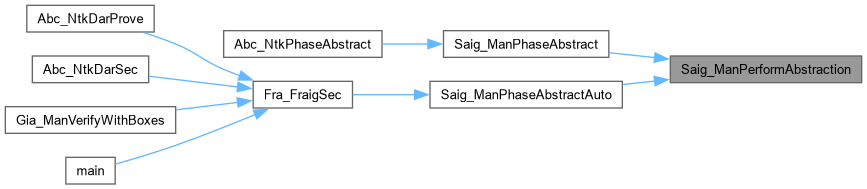

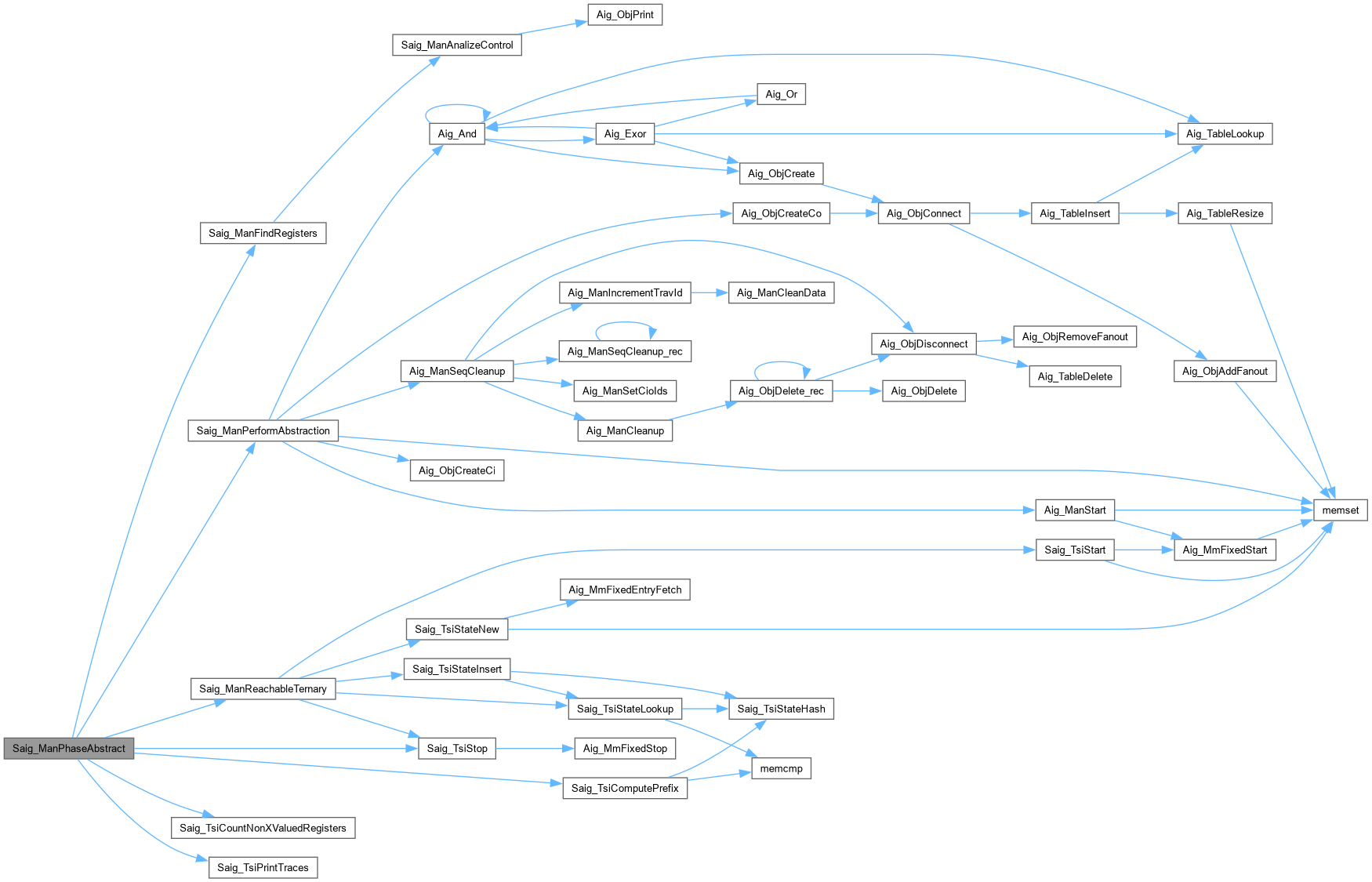

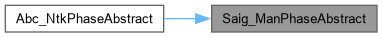

| Aig_Man_t * Saig_ManPhaseAbstract | ( | Aig_Man_t * | p, |

| Vec_Int_t * | vInits, | ||

| int | nFrames, | ||

| int | nPref, | ||

| int | fIgnore, | ||

| int | fPrint, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs automated phase abstraction.]

Description [Takes the AIG manager and the array of initial states.]

SideEffects []

SeeAlso []

Definition at line 911 of file saigPhase.c.

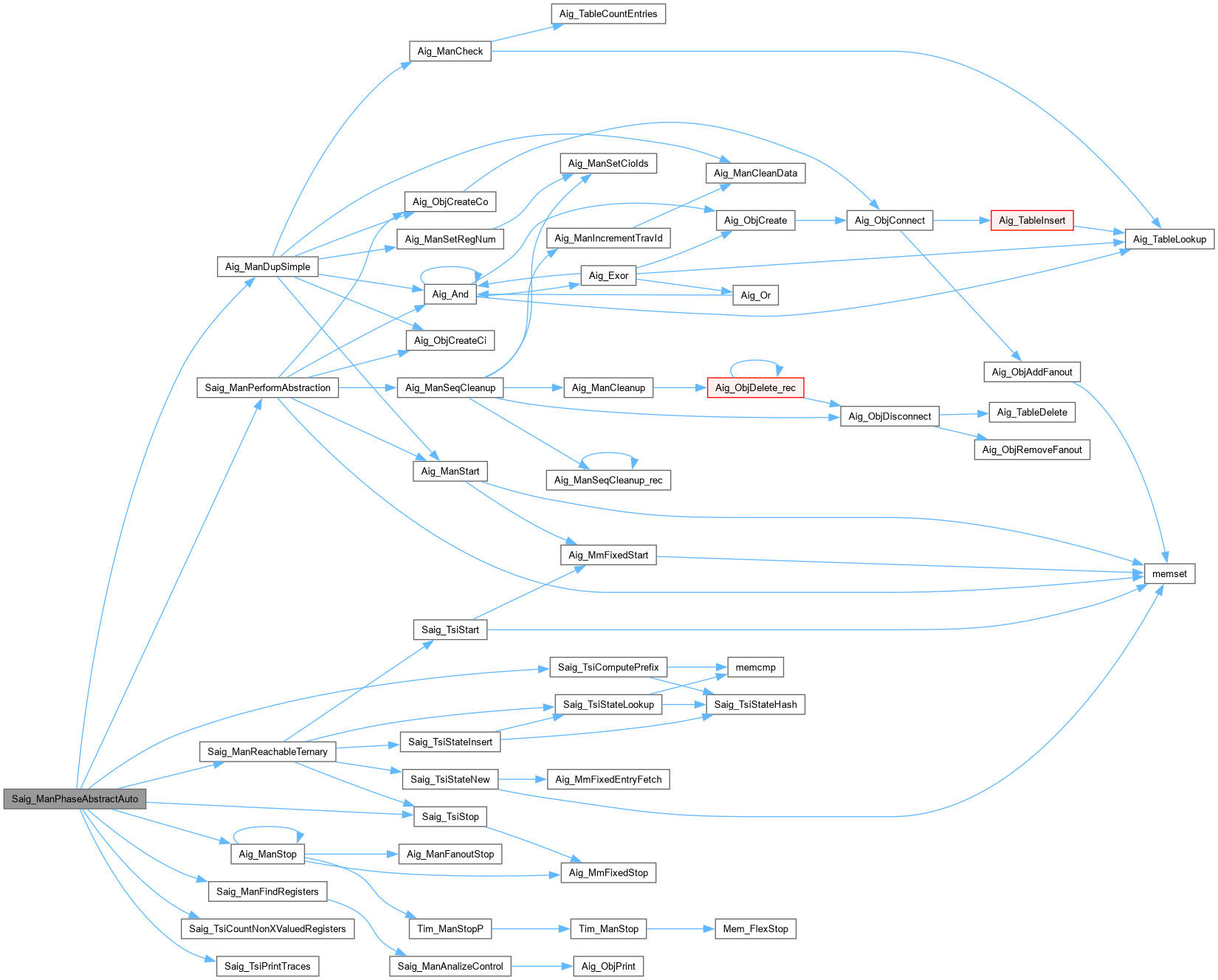

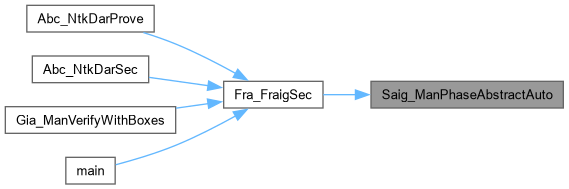

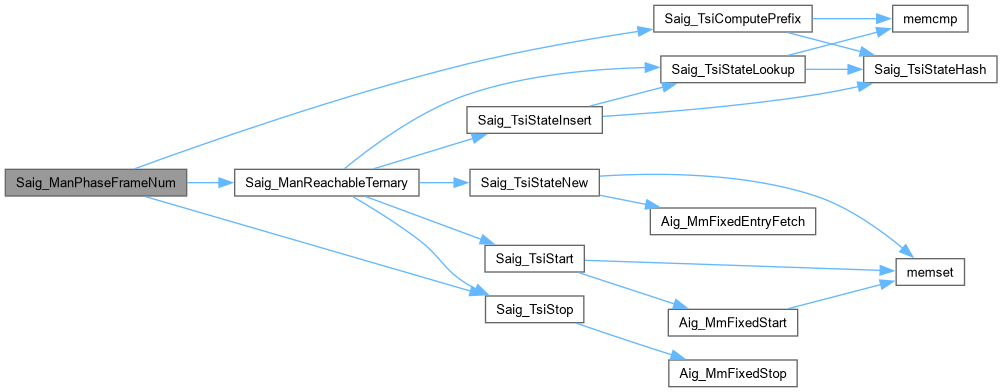

Function*************************************************************

Synopsis [Performs automated phase abstraction.]

Description [Takes the AIG manager and the array of initial states.]

SideEffects []

SeeAlso []

Definition at line 965 of file saigPhase.c.

Function*************************************************************

Synopsis [Performs automated phase abstraction.]

Description [Takes the AIG manager and the array of initial states.]

SideEffects []

SeeAlso []

Definition at line 841 of file saigPhase.c.

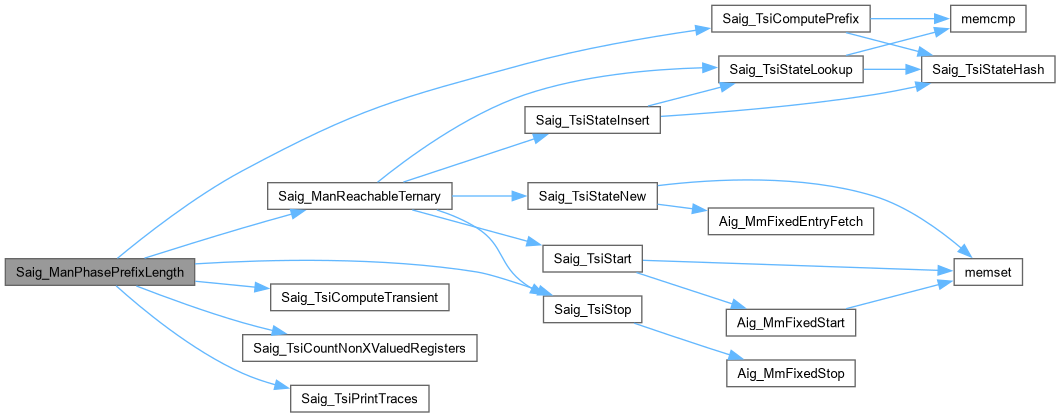

| int Saig_ManPhasePrefixLength | ( | Aig_Man_t * | p, |

| int | fVerbose, | ||

| int | fVeryVerbose, | ||

| Vec_Int_t ** | pvTrans ) |

Function*************************************************************

Synopsis [Performs automated phase abstraction.]

Description [Takes the AIG manager and the array of initial states.]

SideEffects []

SeeAlso []

Definition at line 871 of file saigPhase.c.

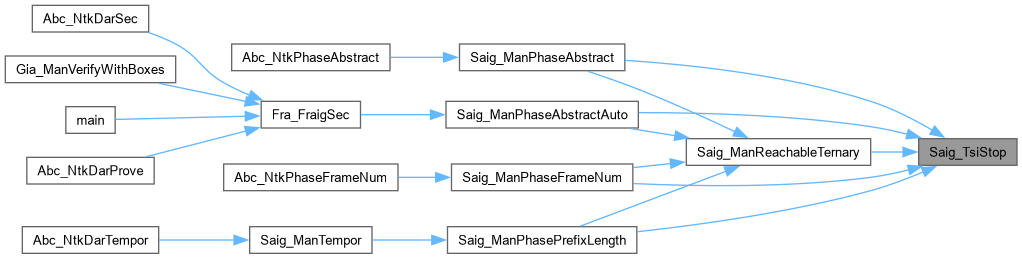

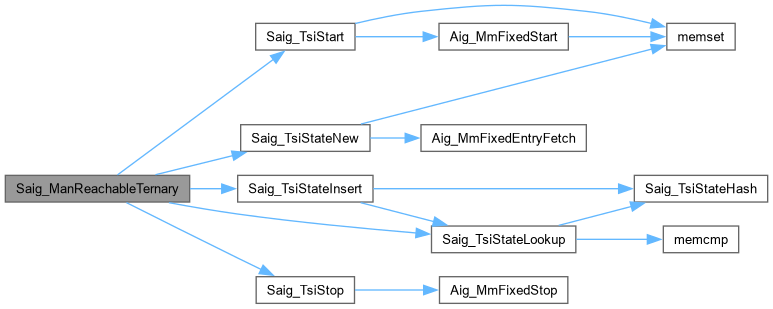

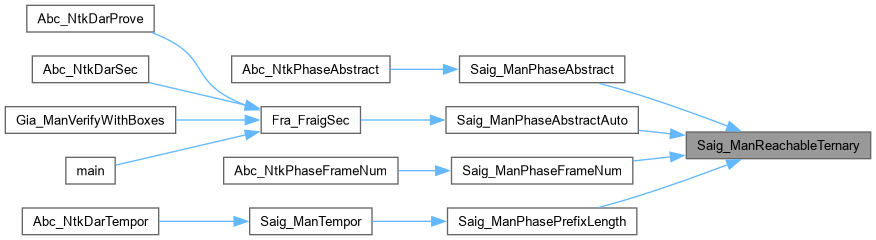

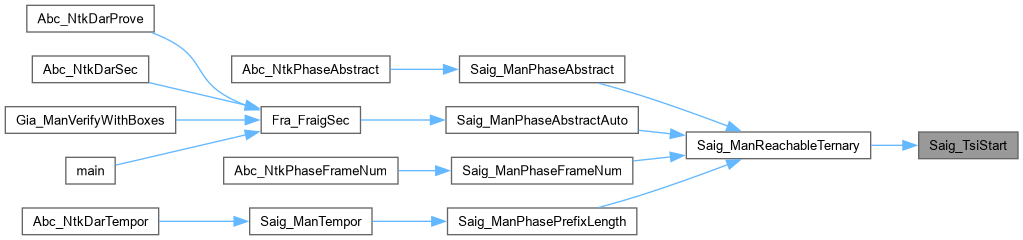

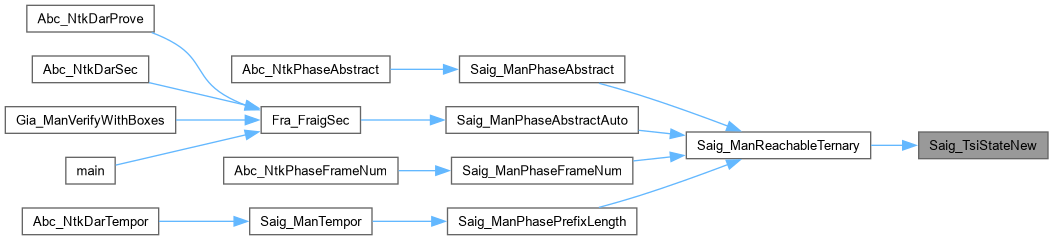

| Saig_Tsim_t * Saig_ManReachableTernary | ( | Aig_Man_t * | p, |

| Vec_Int_t * | vInits, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Cycles the circuit to create a new initial state.]

Description [Simulates the circuit with random input for the given number of timeframes to get a better initial state.]

SideEffects []

SeeAlso []

Definition at line 531 of file saigPhase.c.

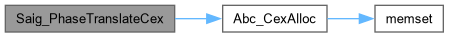

Function*************************************************************

Synopsis [Derives CEX for the original AIG from CEX of the unrolled AIG.]

Description [The number of PIs of the given CEX should divide by the number of PIs of the original AIG without a remainder.]

SideEffects []

SeeAlso []

Definition at line 1045 of file saigPhase.c.

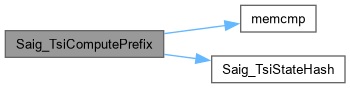

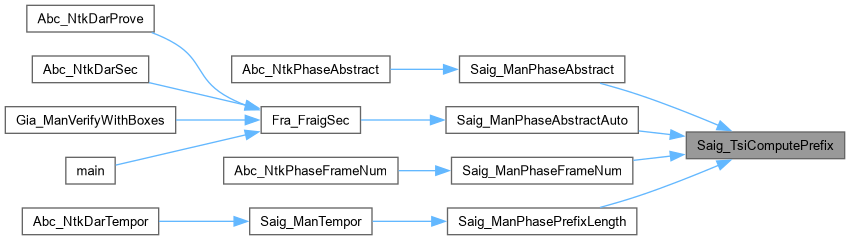

| int Saig_TsiComputePrefix | ( | Saig_Tsim_t * | p, |

| unsigned * | pState, | ||

| int | nWords ) |

Function*************************************************************

Synopsis [Returns the number of the state.]

Description []

SideEffects []

SeeAlso []

Definition at line 365 of file saigPhase.c.

| Vec_Int_t * Saig_TsiComputeTransient | ( | Saig_Tsim_t * | p, |

| int | nPref ) |

Function*************************************************************

Synopsis [Computes flops that are stuck-at constant.]

Description []

SideEffects []

SeeAlso []

Definition at line 258 of file saigPhase.c.

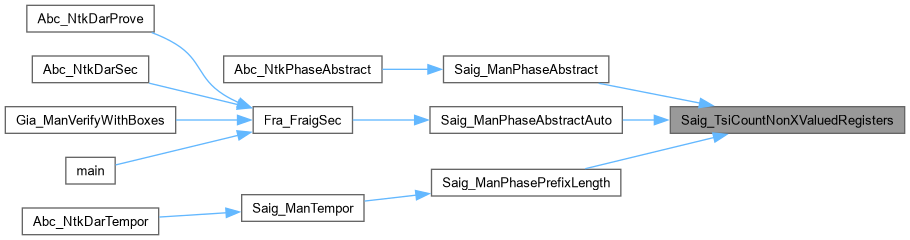

| int Saig_TsiCountNonXValuedRegisters | ( | Saig_Tsim_t * | p, |

| int | nPref ) |

Function*************************************************************

Synopsis [Count non-X-valued registers in the simulation data.]

Description []

SideEffects []

SeeAlso []

Definition at line 225 of file saigPhase.c.

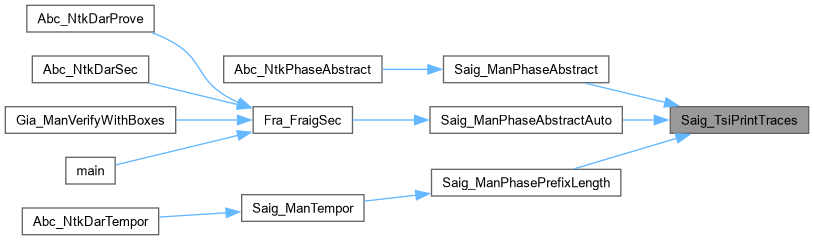

| void Saig_TsiPrintTraces | ( | Saig_Tsim_t * | p, |

| int | nWords, | ||

| int | nPrefix, | ||

| int | nLoop ) |

Function*************************************************************

Synopsis [Count non-X-valued registers in the simulation data.]

Description []

SideEffects []

SeeAlso []

Definition at line 305 of file saigPhase.c.

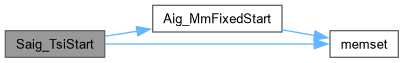

| Saig_Tsim_t * Saig_TsiStart | ( | Aig_Man_t * | pAig | ) |

DECLARATIONS ///.

FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Allocates simulation manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 142 of file saigPhase.c.

| int Saig_TsiStateCount | ( | Saig_Tsim_t * | p, |

| unsigned * | pState ) |

Function*************************************************************

Synopsis [Count constant values in the state.]

Description []

SideEffects []

SeeAlso []

Definition at line 485 of file saigPhase.c.

| int Saig_TsiStateHash | ( | unsigned * | pState, |

| int | nWords, | ||

| int | nTableSize ) |

Function*************************************************************

Synopsis [Computes hash value of the node using its simulation info.]

Description []

SideEffects []

SeeAlso []

Definition at line 189 of file saigPhase.c.

| void Saig_TsiStateInsert | ( | Saig_Tsim_t * | p, |

| unsigned * | pState, | ||

| int | nWords ) |

Function*************************************************************

Synopsis [Inserts value into the table.]

Description []

SideEffects []

SeeAlso []

Definition at line 417 of file saigPhase.c.

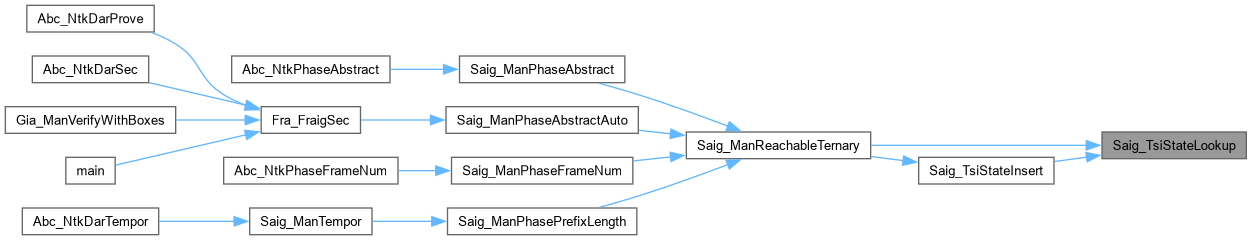

| int Saig_TsiStateLookup | ( | Saig_Tsim_t * | p, |

| unsigned * | pState, | ||

| int | nWords ) |

Function*************************************************************

Synopsis [Checks if the value exists in the table.]

Description []

SideEffects []

SeeAlso []

Definition at line 395 of file saigPhase.c.

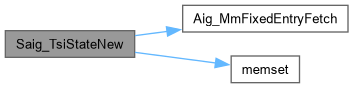

| unsigned * Saig_TsiStateNew | ( | Saig_Tsim_t * | p | ) |

Function*************************************************************

Synopsis [Inserts value into the table.]

Description []

SideEffects []

SeeAlso []

Definition at line 436 of file saigPhase.c.

| void Saig_TsiStateOrAll | ( | Saig_Tsim_t * | pTsi, |

| unsigned * | pState ) |

Function*************************************************************

Synopsis [Count constant values in the state.]

Description []

SideEffects []

SeeAlso []

Definition at line 508 of file saigPhase.c.

| void Saig_TsiStatePrint | ( | Saig_Tsim_t * | p, |

| unsigned * | pState ) |

Function*************************************************************

Synopsis [Inserts value into the table.]

Description []

SideEffects []

SeeAlso []

Definition at line 456 of file saigPhase.c.

| void Saig_TsiStop | ( | Saig_Tsim_t * | p | ) |

Function*************************************************************

Synopsis [Deallocates simulation manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 168 of file saigPhase.c.