Go to the source code of this file.

Classes | |

| struct | Raig_Man_t_ |

Typedefs | |

| typedef typedefABC_NAMESPACE_IMPL_START struct Raig_Man_t_ | Raig_Man_t |

| DECLARATIONS ///. | |

Functions | |

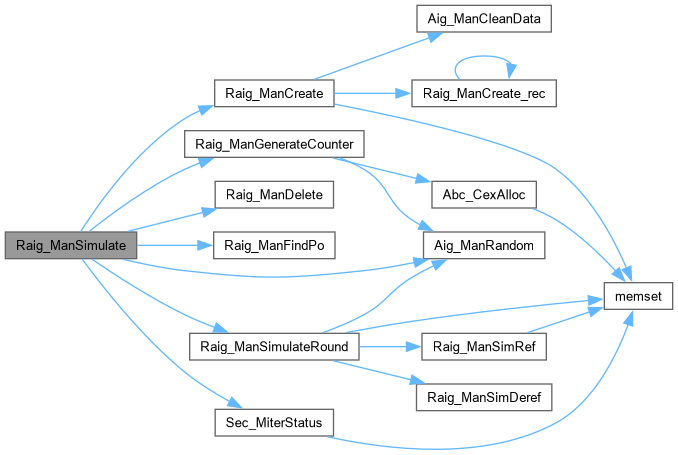

| int | Raig_ManFindPo (Aig_Man_t *pAig, int iNode) |

| FUNCTION DEFINITIONS ///. | |

| int | Raig_ManCreate_rec (Raig_Man_t *p, Aig_Obj_t *pObj) |

| Raig_Man_t * | Raig_ManCreate (Aig_Man_t *pAig) |

| void | Raig_ManDelete (Raig_Man_t *p) |

| unsigned * | Raig_ManSimRef (Raig_Man_t *p, int i) |

| unsigned * | Raig_ManSimDeref (Raig_Man_t *p, int i) |

| int | Raig_ManSimulateRound (Raig_Man_t *p, int fMiter, int fFirst, int *piPat) |

| Abc_Cex_t * | Raig_ManGenerateCounter (Aig_Man_t *pAig, int iFrame, int iOut, int nWords, int iPat, Vec_Int_t *vCis2Ids) |

| int | Raig_ManSimulate (Aig_Man_t *pAig, int nWords, int nIters, int TimeLimit, int fMiter, int fVerbose) |

| typedef typedefABC_NAMESPACE_IMPL_START struct Raig_Man_t_ Raig_Man_t |

DECLARATIONS ///.

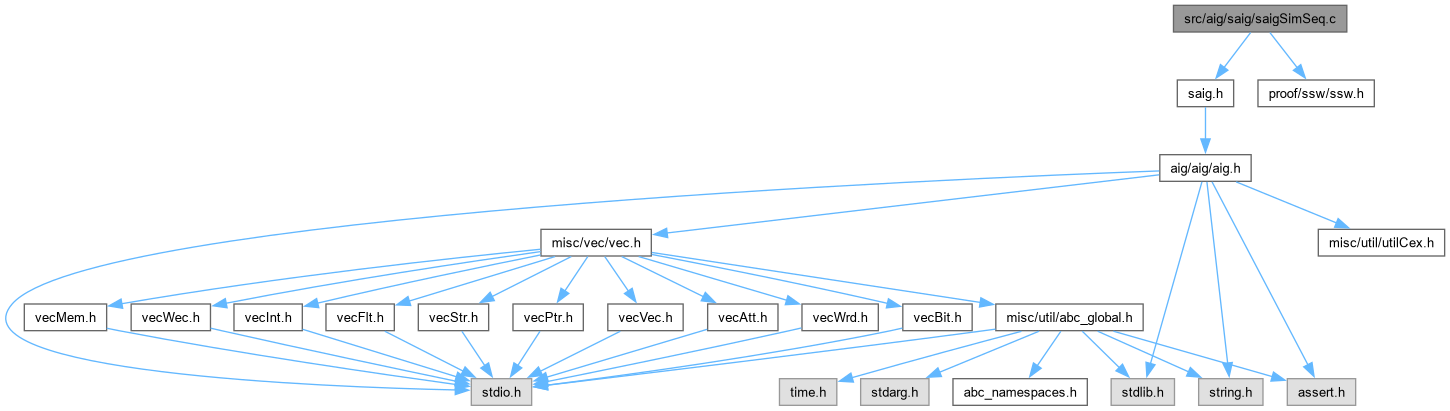

CFile****************************************************************

FileName [saigSimSeq.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Sequential AIG package.]

Synopsis [Fast sequential AIG simulator.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

Definition at line 32 of file saigSimSeq.c.

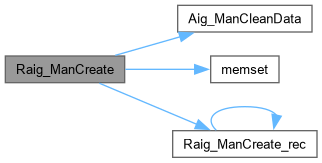

| Raig_Man_t * Raig_ManCreate | ( | Aig_Man_t * | pAig | ) |

Function*************************************************************

Synopsis [Creates fast simulation manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 146 of file saigSimSeq.c.

| int Raig_ManCreate_rec | ( | Raig_Man_t * | p, |

| Aig_Obj_t * | pObj ) |

Function*************************************************************

Synopsis [Creates fast simulation manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 104 of file saigSimSeq.c.

| void Raig_ManDelete | ( | Raig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Creates fast simulation manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 203 of file saigSimSeq.c.

| int Raig_ManFindPo | ( | Aig_Man_t * | pAig, |

| int | iNode ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Find the PO corresponding to the PO driver.]

Description []

SideEffects []

SeeAlso []

Definition at line 83 of file saigSimSeq.c.

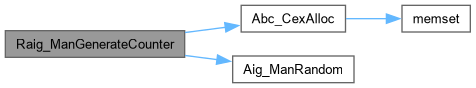

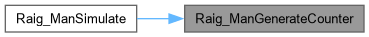

| Abc_Cex_t * Raig_ManGenerateCounter | ( | Aig_Man_t * | pAig, |

| int | iFrame, | ||

| int | iOut, | ||

| int | nWords, | ||

| int | iPat, | ||

| Vec_Int_t * | vCis2Ids ) |

Function*************************************************************

Synopsis [Returns the counter-example.]

Description []

SideEffects []

SeeAlso []

Definition at line 416 of file saigSimSeq.c.

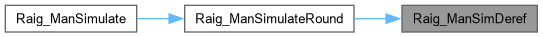

| unsigned * Raig_ManSimDeref | ( | Raig_Man_t * | p, |

| int | i ) |

Function*************************************************************

Synopsis [Dereference simulaton info.]

Description []

SideEffects []

SeeAlso []

Definition at line 275 of file saigSimSeq.c.

| unsigned * Raig_ManSimRef | ( | Raig_Man_t * | p, |

| int | i ) |

Function*************************************************************

Synopsis [References simulation info.]

Description []

SideEffects []

SeeAlso []

Definition at line 227 of file saigSimSeq.c.

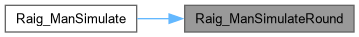

| int Raig_ManSimulate | ( | Aig_Man_t * | pAig, |

| int | nWords, | ||

| int | nIters, | ||

| int | TimeLimit, | ||

| int | fMiter, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Returns 1 if the bug is detected, 0 otherwise.]

Description []

SideEffects []

SeeAlso []

Definition at line 454 of file saigSimSeq.c.

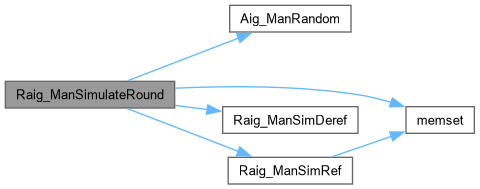

| int Raig_ManSimulateRound | ( | Raig_Man_t * | p, |

| int | fMiter, | ||

| int | fFirst, | ||

| int * | piPat ) |

Function*************************************************************

Synopsis [Simulates one round.]

Description [Returns the number of PO entry if failed; 0 otherwise.]

SideEffects []

SeeAlso []

Definition at line 304 of file saigSimSeq.c.