#include "sswInt.h"

Go to the source code of this file.

Functions | |

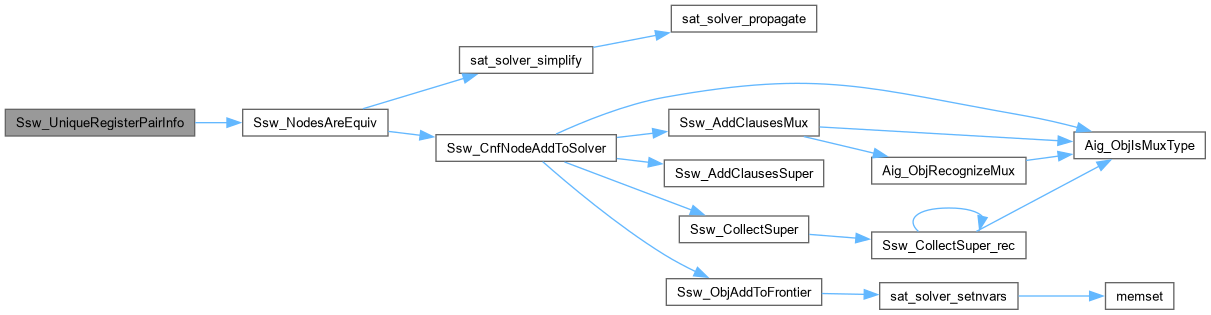

| ABC_NAMESPACE_IMPL_START void | Ssw_UniqueRegisterPairInfo (Ssw_Man_t *p) |

| DECLARATIONS ///. | |

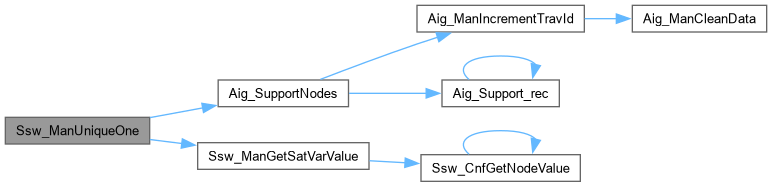

| int | Ssw_ManUniqueOne (Ssw_Man_t *p, Aig_Obj_t *pRepr, Aig_Obj_t *pObj, int fVerbose) |

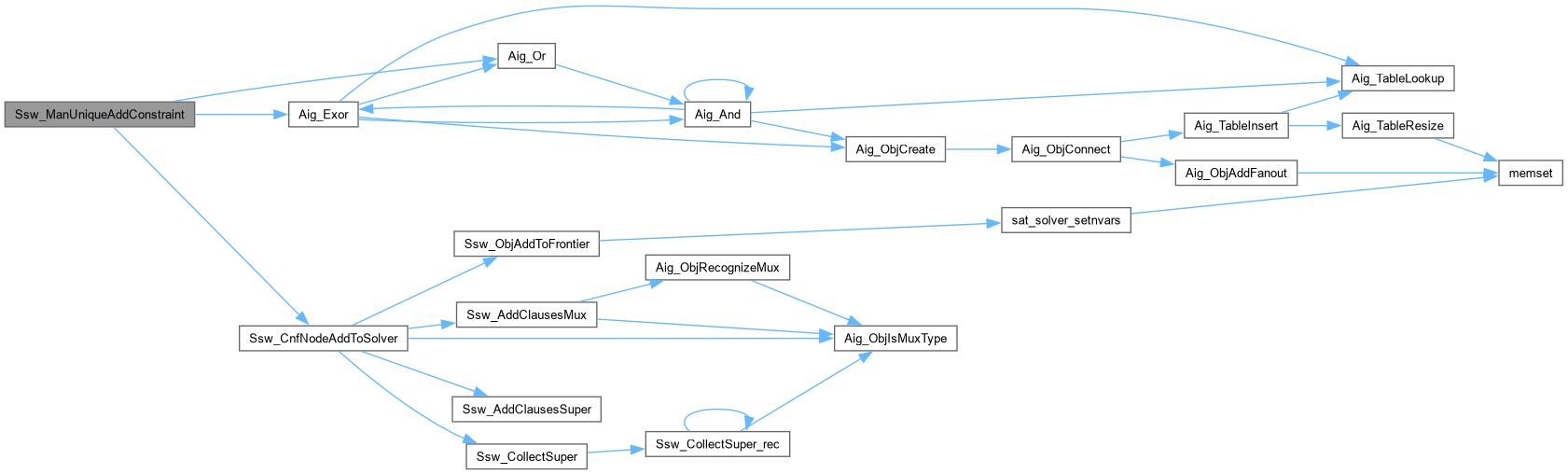

| int | Ssw_ManUniqueAddConstraint (Ssw_Man_t *p, Vec_Ptr_t *vCommon, int f1, int f2) |

Function*************************************************************

Synopsis [Returns the output of the uniqueness constraint.]

Description []

SideEffects []

SeeAlso []

Definition at line 151 of file sswUnique.c.

Function*************************************************************

Synopsis [Returns 1 if uniqueness constraints can be added.]

Description []

SideEffects []

SeeAlso []

Definition at line 90 of file sswUnique.c.

| ABC_NAMESPACE_IMPL_START void Ssw_UniqueRegisterPairInfo | ( | Ssw_Man_t * | p | ) |

DECLARATIONS ///.

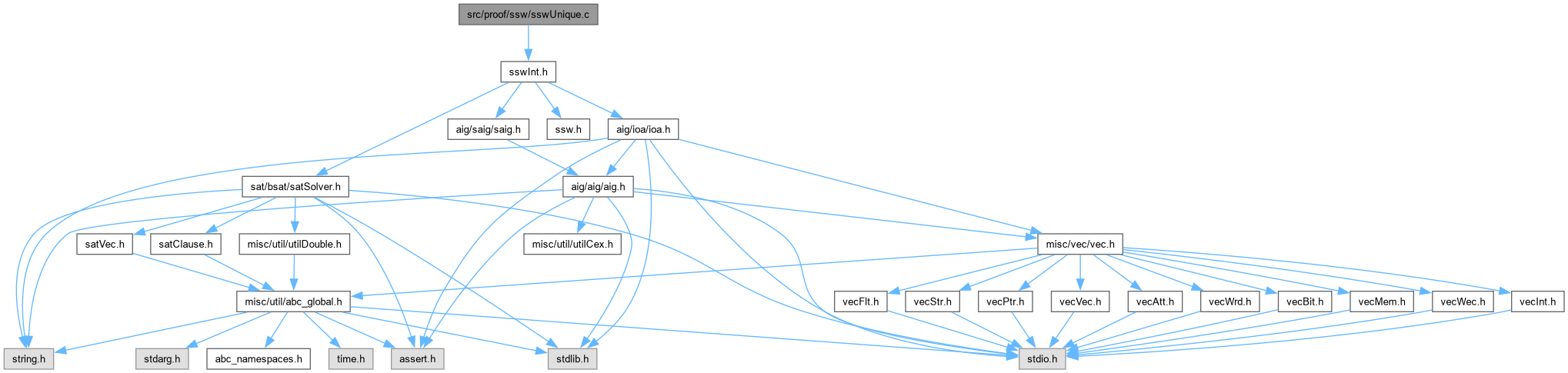

CFile****************************************************************

FileName [sswSat.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Inductive prover with constraints.]

Synopsis [On-demand uniqueness constraints.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 1, 2008.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Performs computation of signal correspondence with constraints.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file sswUnique.c.