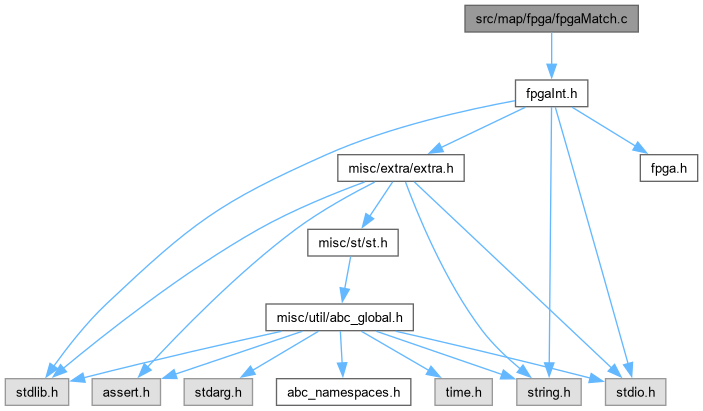

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

| int | Fpga_MappingMatches (Fpga_Man_t *p, int fDelayOriented) |

| FUNCTION DEFINITIONS ///. | |

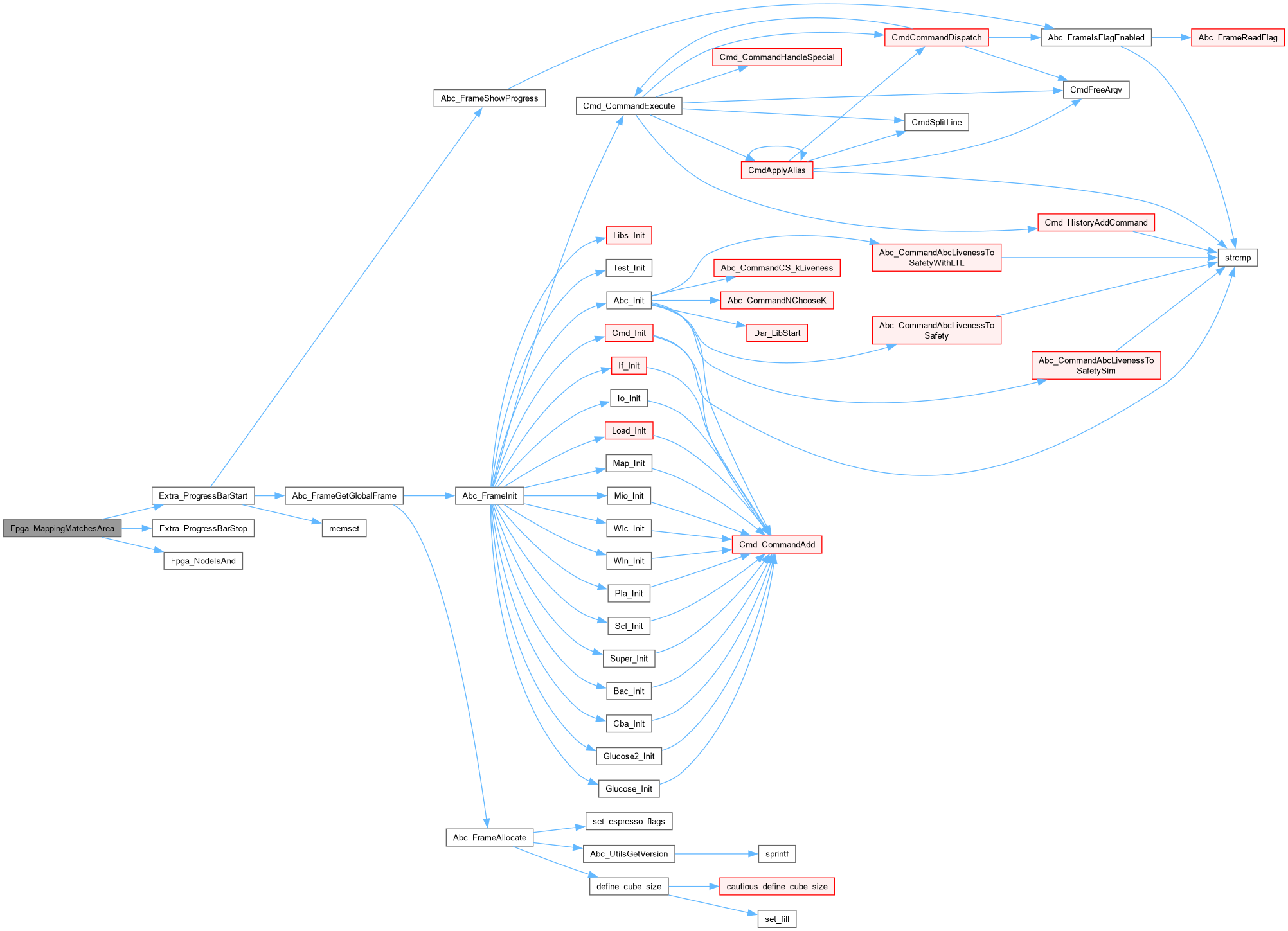

| int | Fpga_MappingMatchesArea (Fpga_Man_t *p) |

| int | Fpga_MappingMatchesSwitch (Fpga_Man_t *p) |

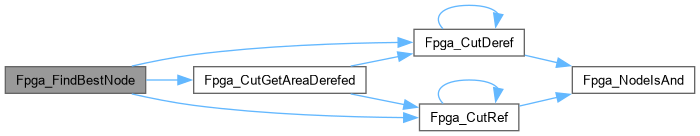

| float | Fpga_FindBestNode (Fpga_Man_t *p, Fpga_NodeVec_t *vNodes, Fpga_Node_t **ppNode, Fpga_Cut_t **ppCutBest) |

| float Fpga_FindBestNode | ( | Fpga_Man_t * | p, |

| Fpga_NodeVec_t * | vNodes, | ||

| Fpga_Node_t ** | ppNode, | ||

| Fpga_Cut_t ** | ppCutBest ) |

function*************************************************************

synopsis [Performs area minimization using a heuristic algorithm.]

description []

sideeffects []

seealso []

Definition at line 756 of file fpgaMatch.c.

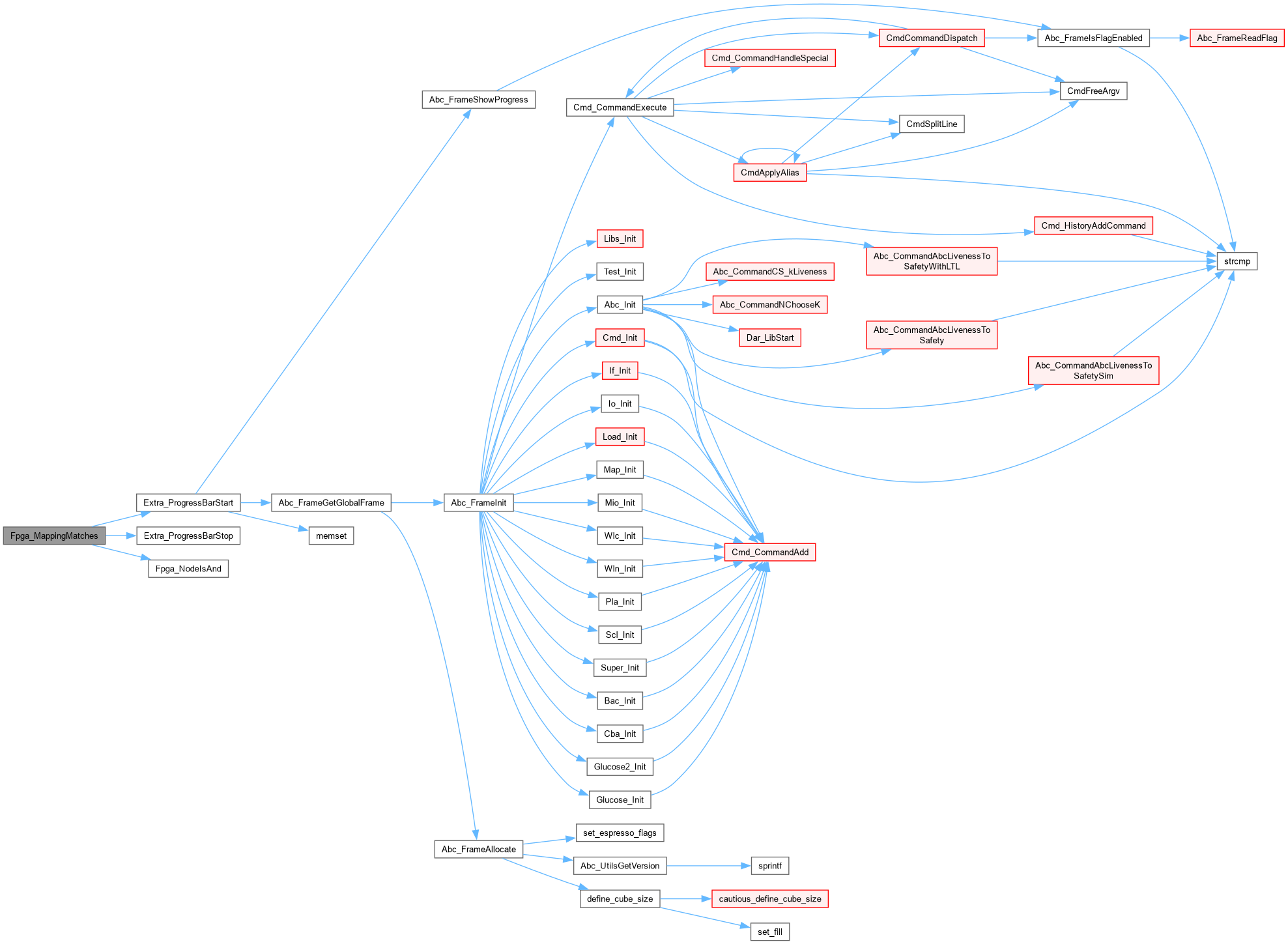

| int Fpga_MappingMatches | ( | Fpga_Man_t * | p, |

| int | fDelayOriented ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Finds the best delay assignment of LUTs.]

Description [This procedure iterates through all the nodes of the object graph reachable from the POs and assigns the best match to each of them. If the flag fDelayOriented is set to 1, it tries to minimize the arrival time and uses the area flow as a tie-breaker. If the flag is set to 0, it considers all the cuts, whose arrival times matches the required time at the node, and minimizes the area flow using the arrival time as a tie-breaker.

Before this procedure is called, the required times should be set and the fanout counts should be computed. In the first iteration, the required times are set to very large number (by NodeCreate) and the fanout counts are set to the number of fanouts in the AIG. In the following iterations, the required times are set by the backward traversal, while the fanouts are estimated approximately.

If the arrival times of the PI nodes are given, they should be assigned to the PIs after the cuts are computed and before this procedure is called for the first time.]

SideEffects []

SeeAlso []

Definition at line 67 of file fpgaMatch.c.

| int Fpga_MappingMatchesArea | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Finds the best area assignment of LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 196 of file fpgaMatch.c.

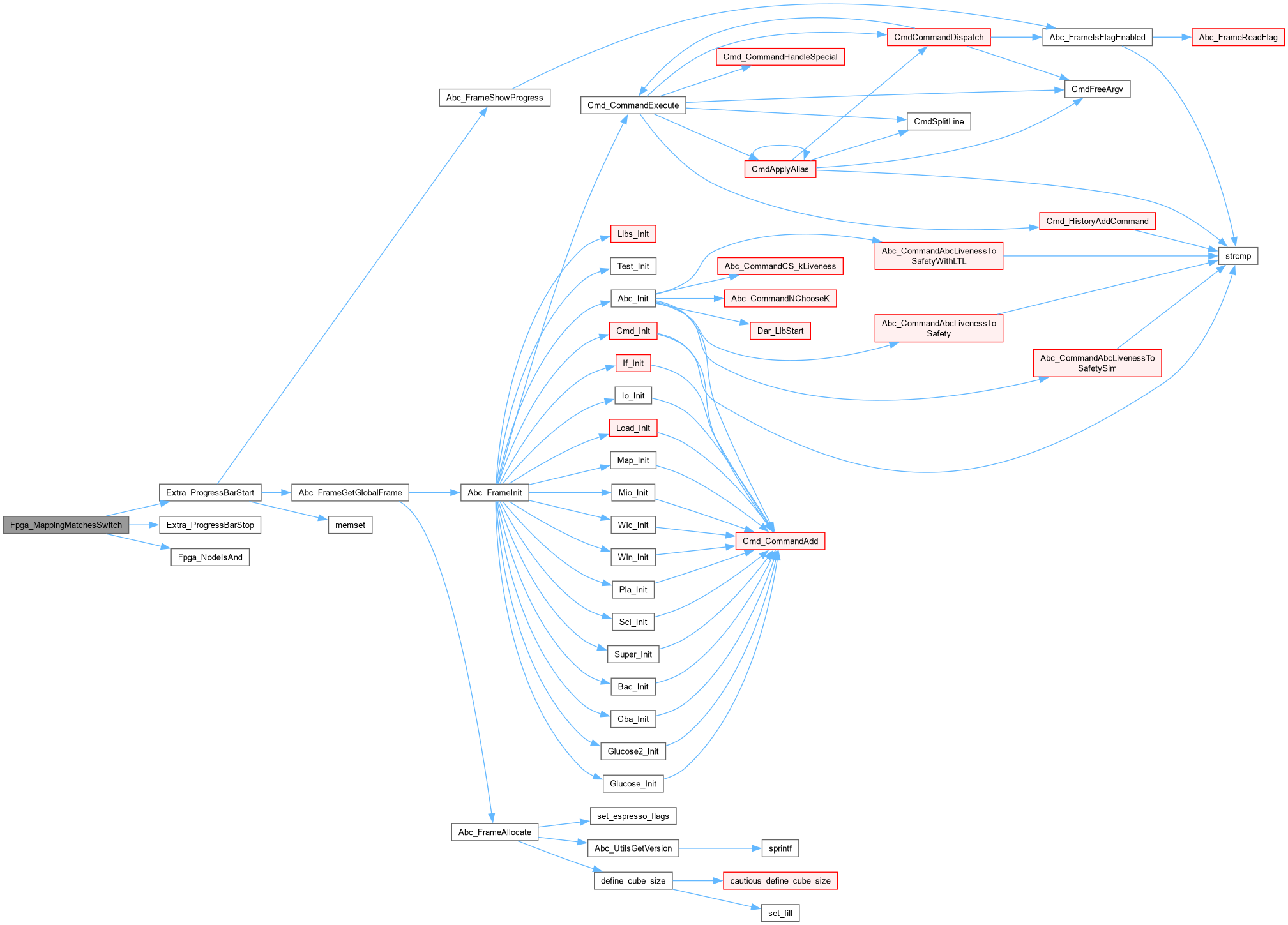

| int Fpga_MappingMatchesSwitch | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Finds the best area assignment of LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 349 of file fpgaMatch.c.