#include <stdio.h>#include "base/main/main.h"#include "aig/aig/aig.h"#include "aig/saig/saig.h"#include <string.h>#include "base/main/mainInt.h"

Go to the source code of this file.

Macros | |

| #define | PROPAGATE_NAMES |

| #define | MULTIPLE_LTL_FORMULA |

| #define | ALLOW_SAFETY_PROPERTIES |

| #define | FULL_BIERE_MODE 0 |

| #define | IGNORE_LIVENESS_KEEP_SAFETY_MODE 1 |

| #define | IGNORE_SAFETY_KEEP_LIVENESS_MODE 2 |

| #define | IGNORE_SAFETY_KEEP_LIVENESS_ONE_LOOP_MODE 3 |

| #define | FULL_BIERE_ONE_LOOP_MODE 4 |

Typedefs | |

| typedef struct ltlNode_t | ltlNode |

Variables | |

| Vec_Ptr_t * | vecPis |

| Vec_Ptr_t * | vecPiNames |

| Vec_Ptr_t * | vecLos |

| Vec_Ptr_t * | vecLoNames |

| #define ALLOW_SAFETY_PROPERTIES |

Definition at line 32 of file liveness.c.

| #define FULL_BIERE_MODE 0 |

Definition at line 34 of file liveness.c.

| #define FULL_BIERE_ONE_LOOP_MODE 4 |

Definition at line 38 of file liveness.c.

| #define IGNORE_LIVENESS_KEEP_SAFETY_MODE 1 |

Definition at line 35 of file liveness.c.

| #define IGNORE_SAFETY_KEEP_LIVENESS_MODE 2 |

Definition at line 36 of file liveness.c.

| #define IGNORE_SAFETY_KEEP_LIVENESS_ONE_LOOP_MODE 3 |

Definition at line 37 of file liveness.c.

| #define MULTIPLE_LTL_FORMULA |

Definition at line 31 of file liveness.c.

| #define PROPAGATE_NAMES |

CFile****************************************************************

FileName [liveness.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Liveness property checking.]

Synopsis [Main implementation module.]

Author [Sayak Ray]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - January 1, 2009.]

Revision [

]

Definition at line 30 of file liveness.c.

Definition at line 48 of file liveness.c.

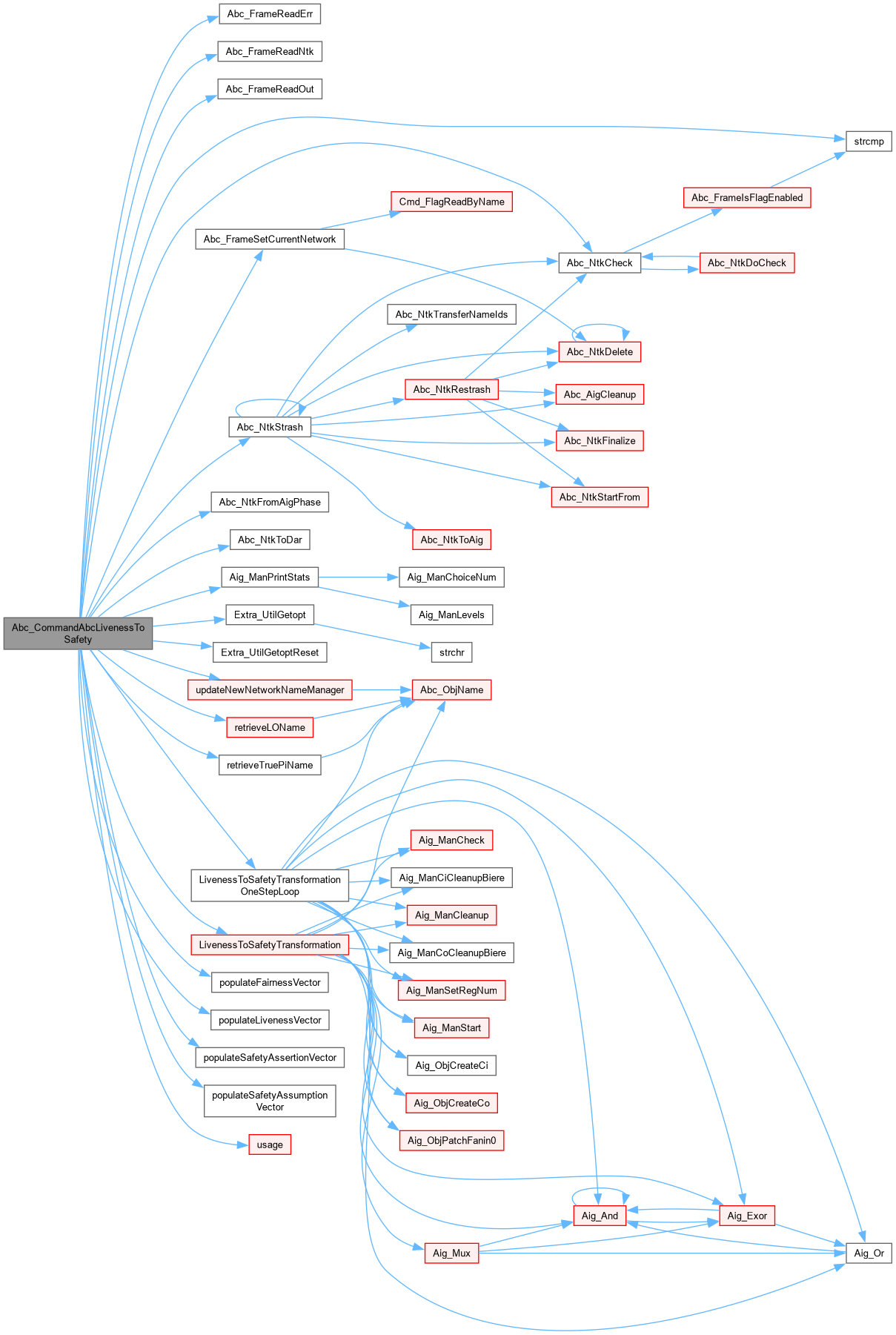

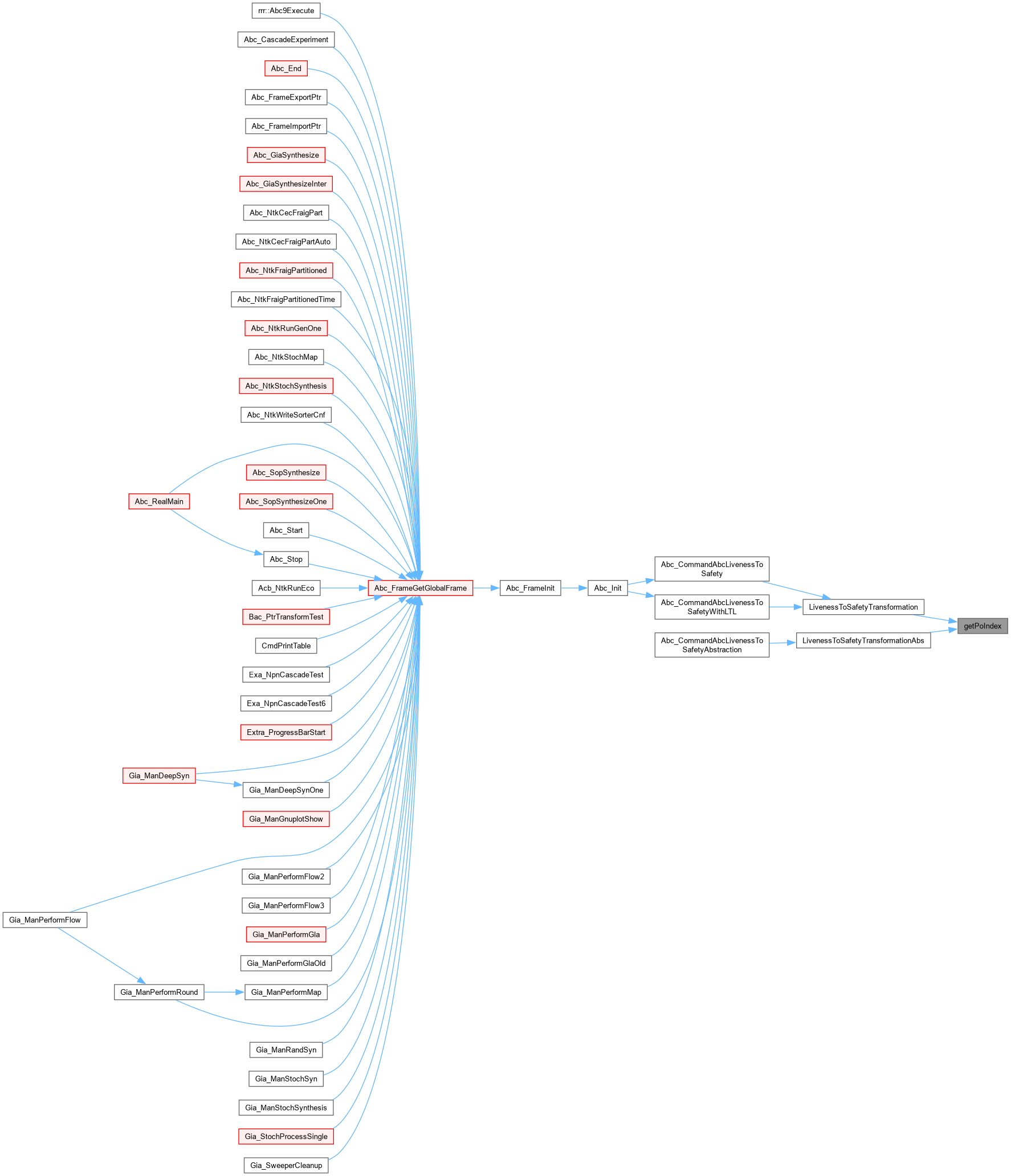

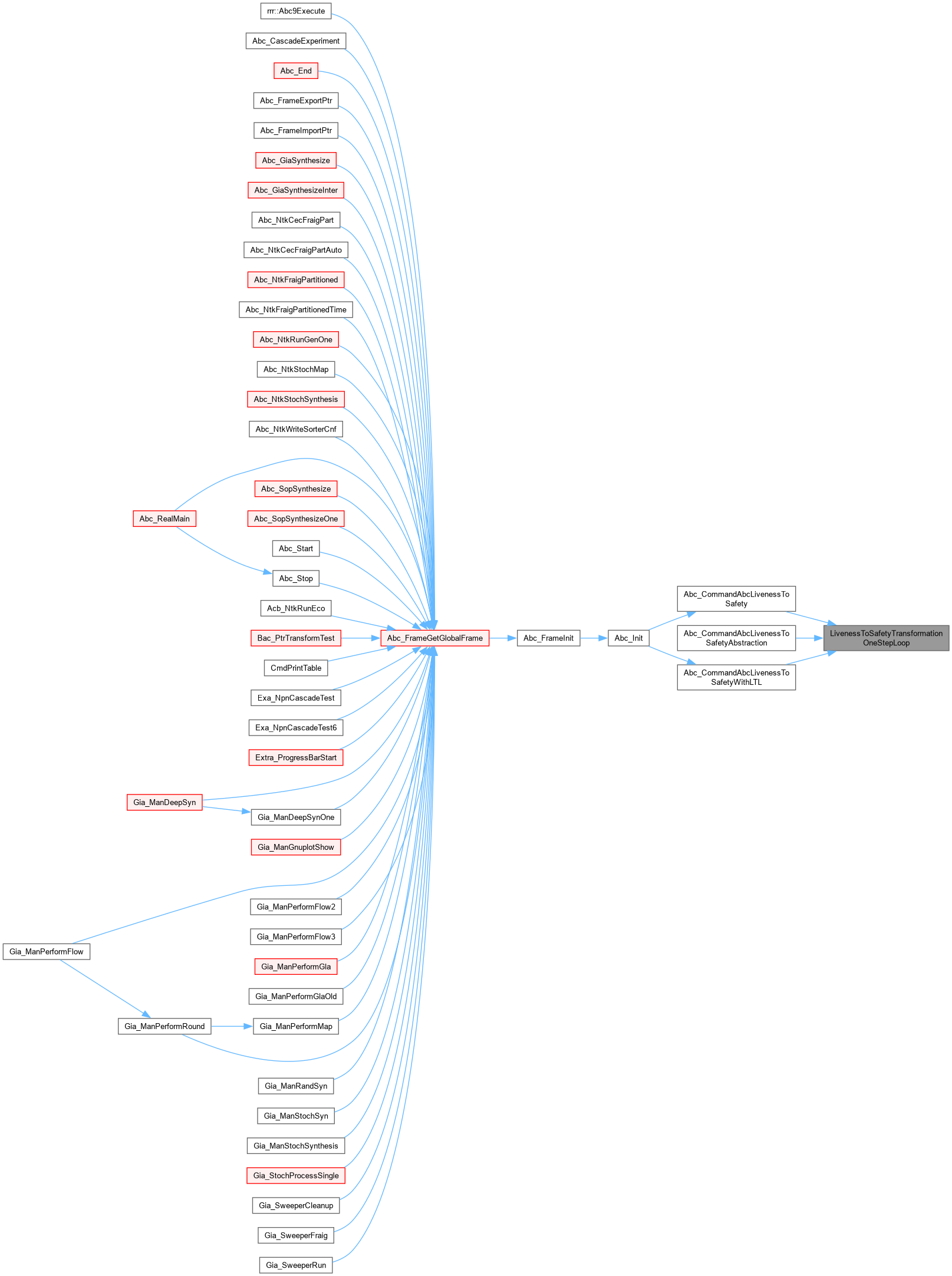

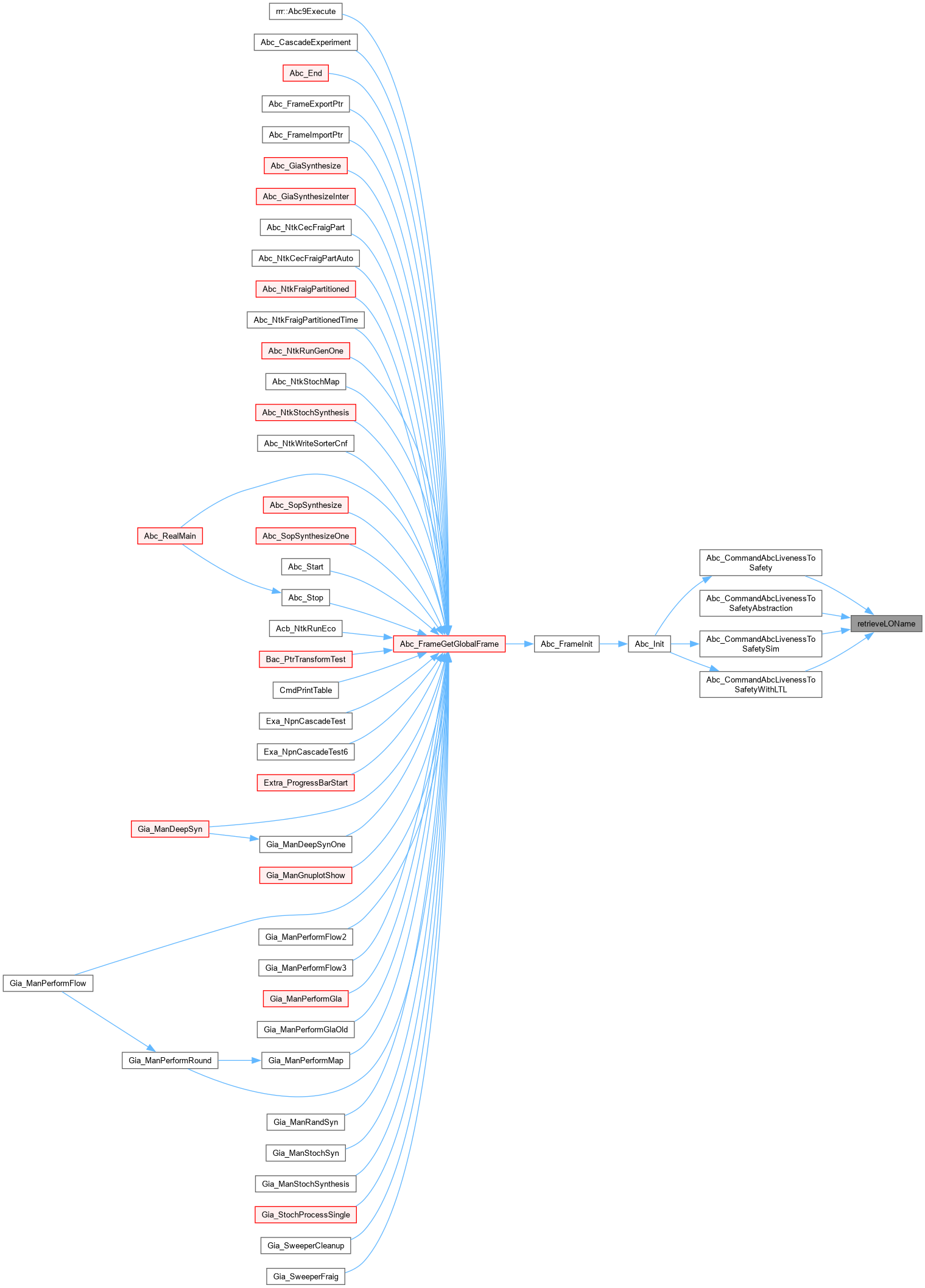

| int Abc_CommandAbcLivenessToSafety | ( | Abc_Frame_t * | pAbc, |

| int | argc, | ||

| char ** | argv ) |

Definition at line 1254 of file liveness.c.

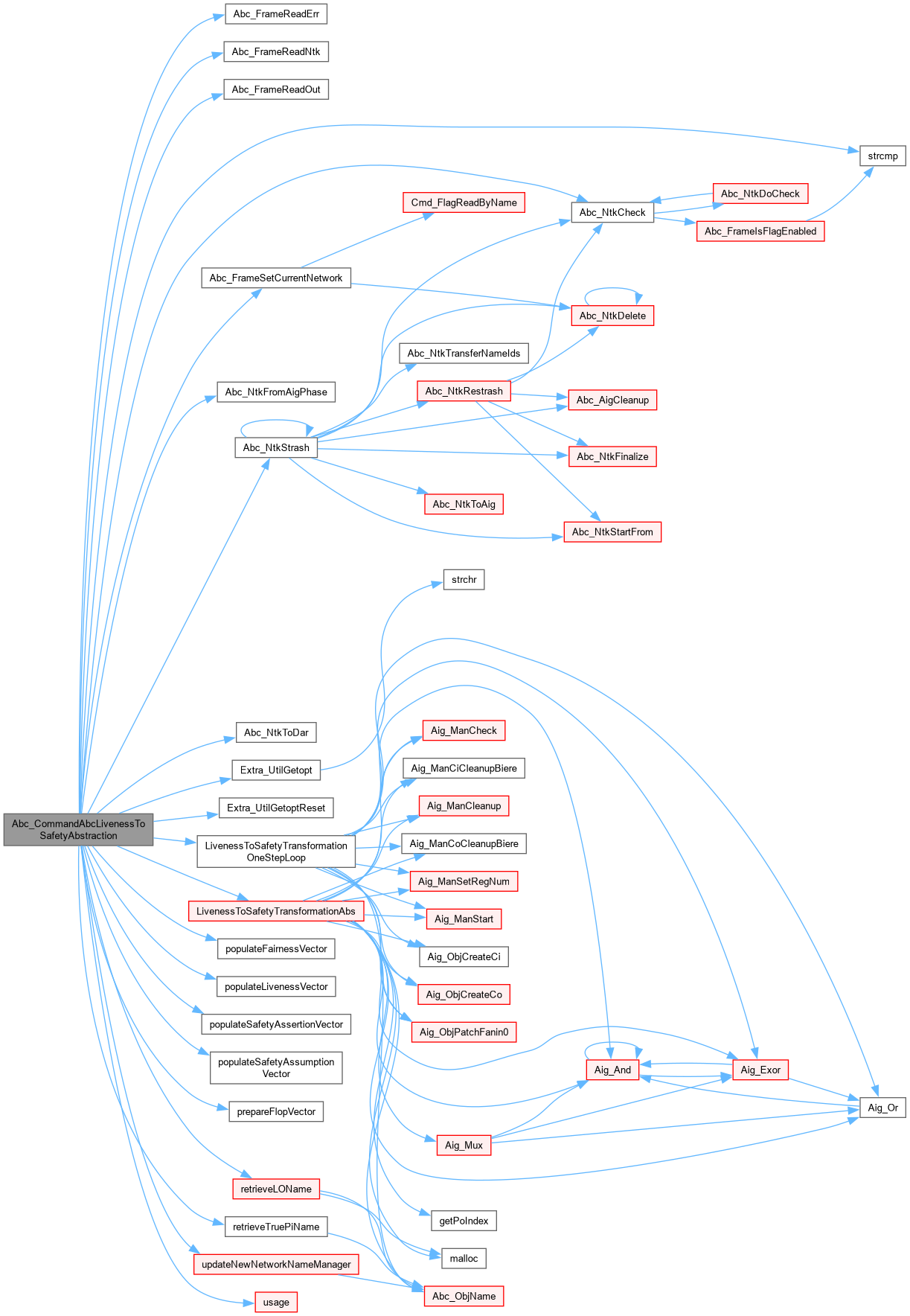

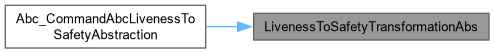

| int Abc_CommandAbcLivenessToSafetyAbstraction | ( | Abc_Frame_t * | pAbc, |

| int | argc, | ||

| char ** | argv ) |

Definition at line 1599 of file liveness.c.

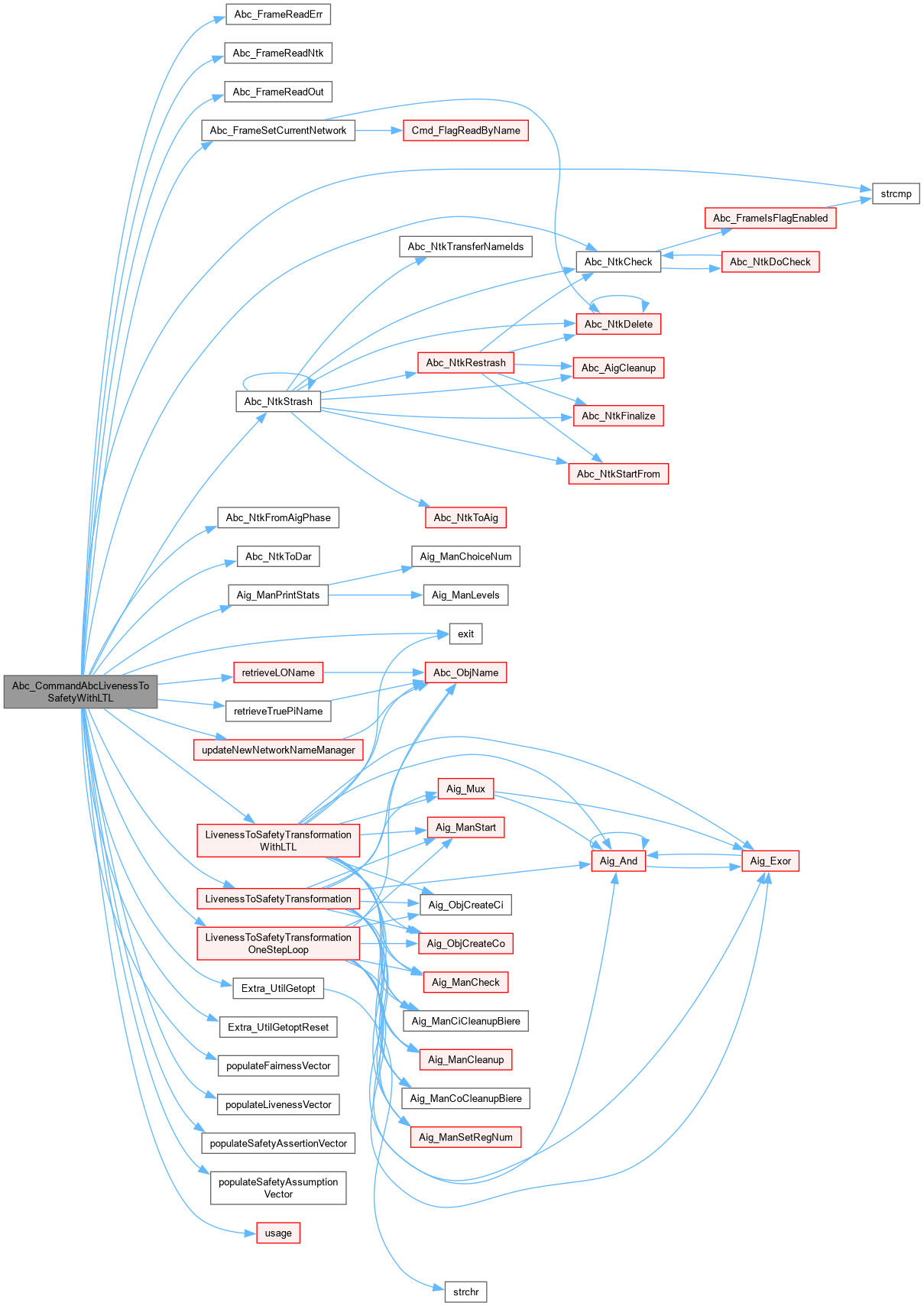

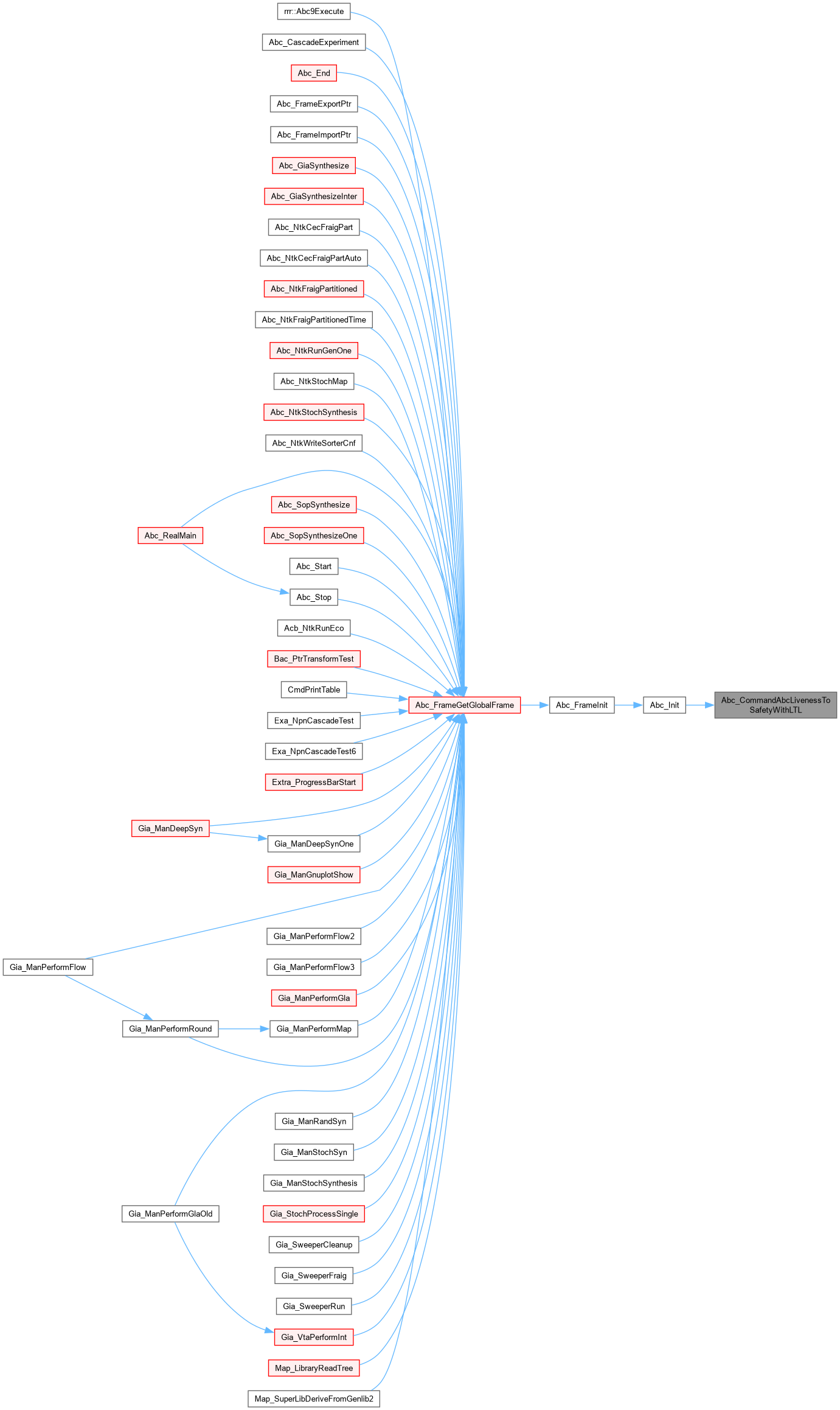

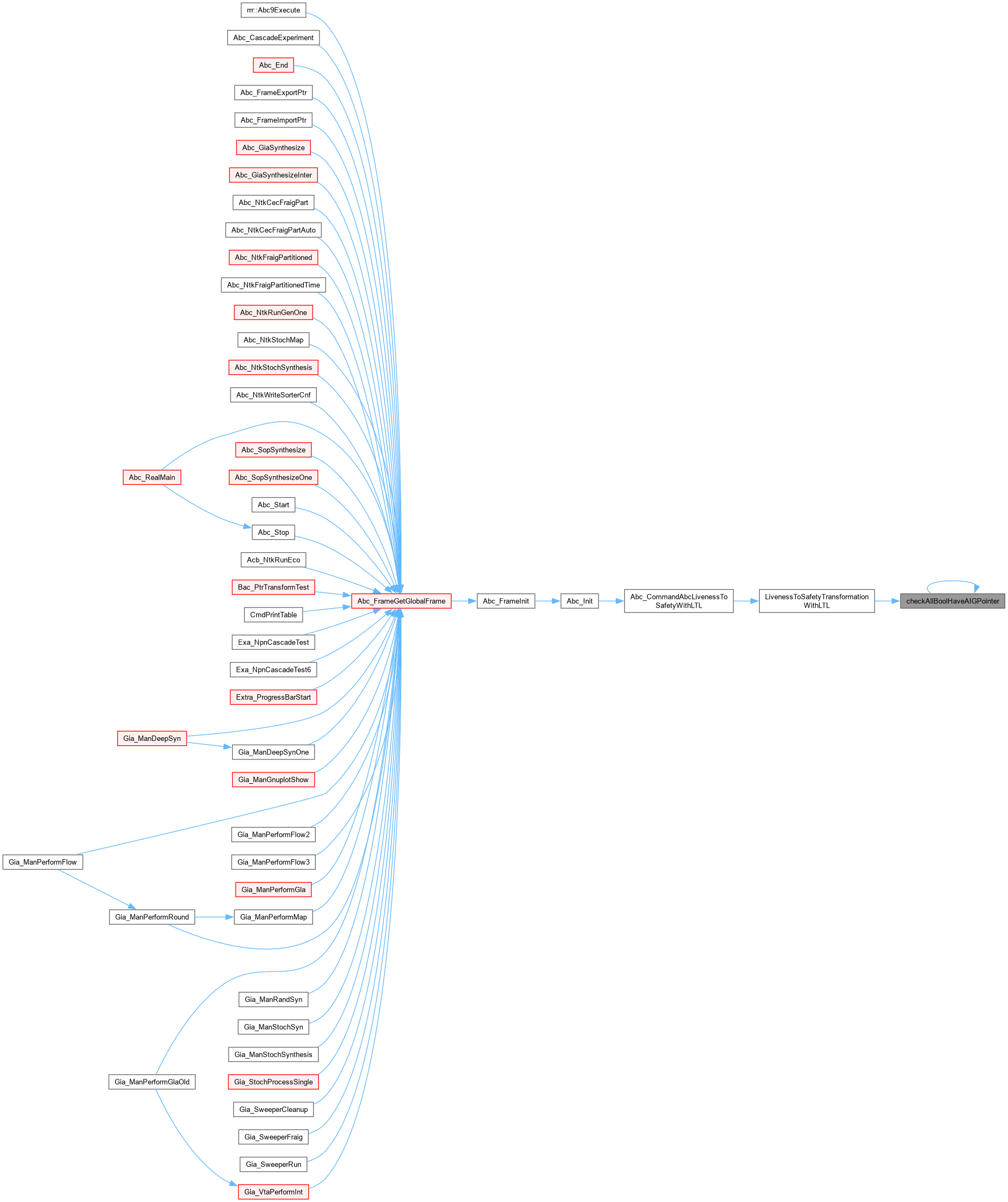

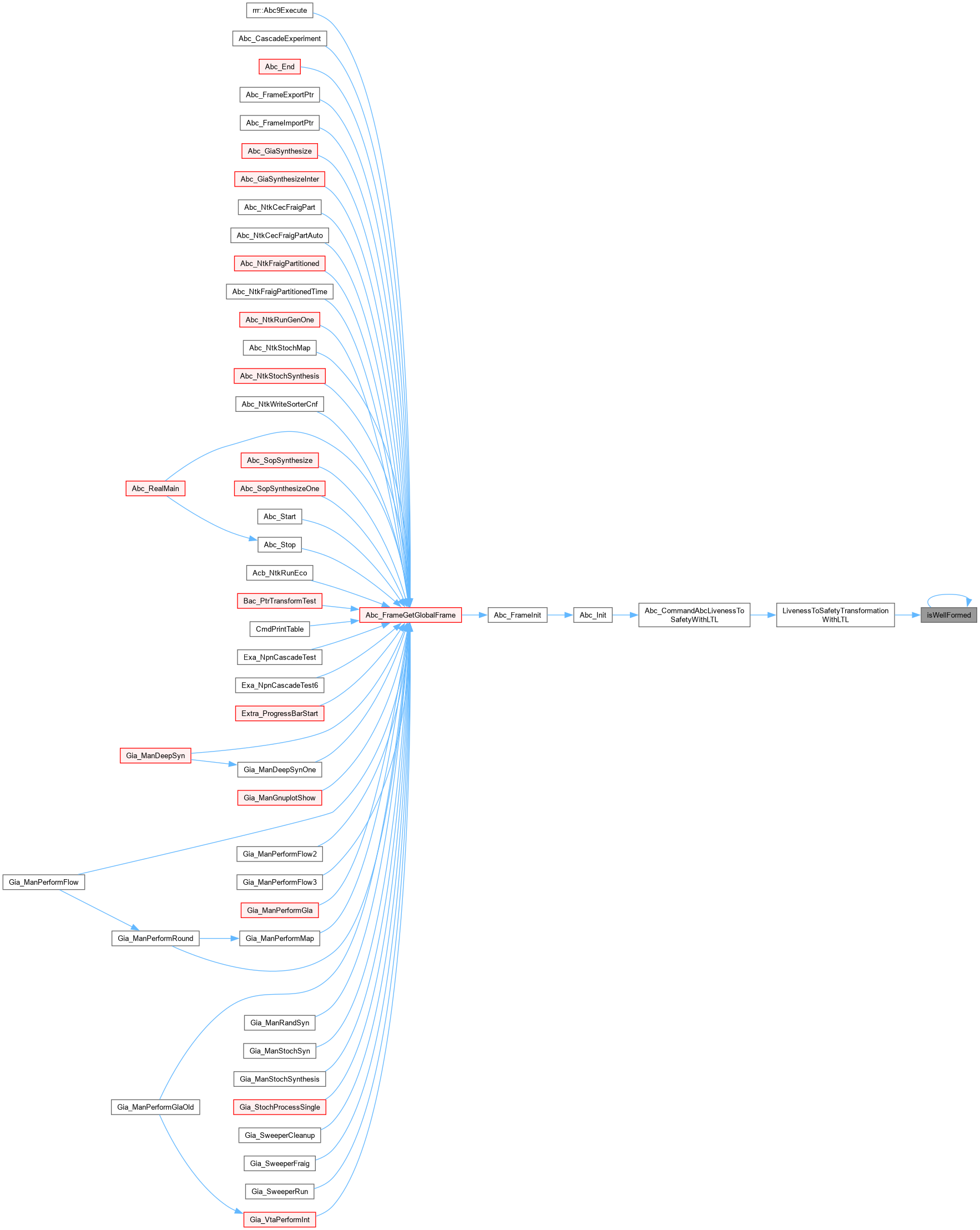

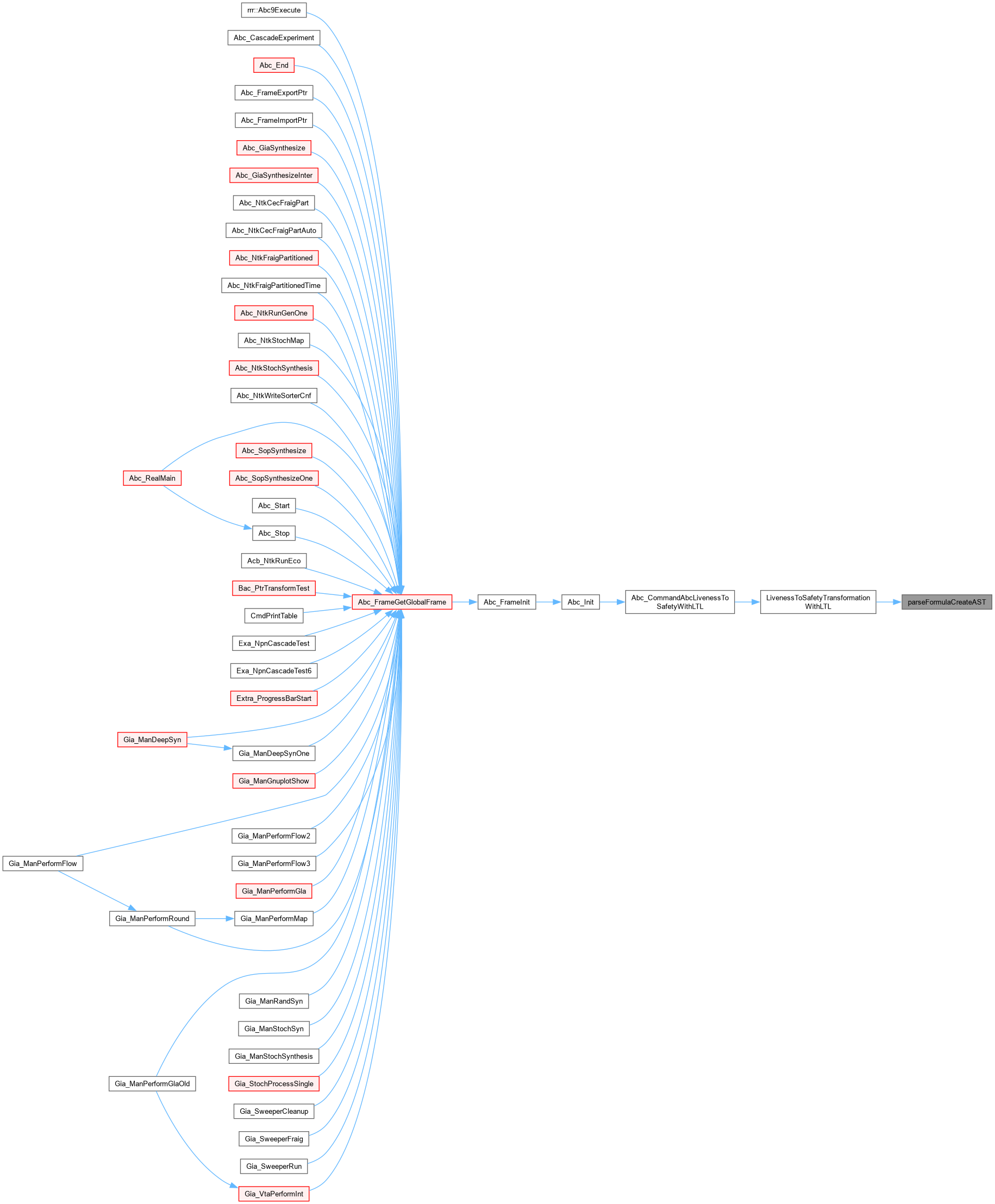

| int Abc_CommandAbcLivenessToSafetyWithLTL | ( | Abc_Frame_t * | pAbc, |

| int | argc, | ||

| char ** | argv ) |

Definition at line 2268 of file liveness.c.

DECLARATIONS ///.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [This procedure should be called after seq sweeping, which changes the number of registers.]

SideEffects []

SeeAlso []

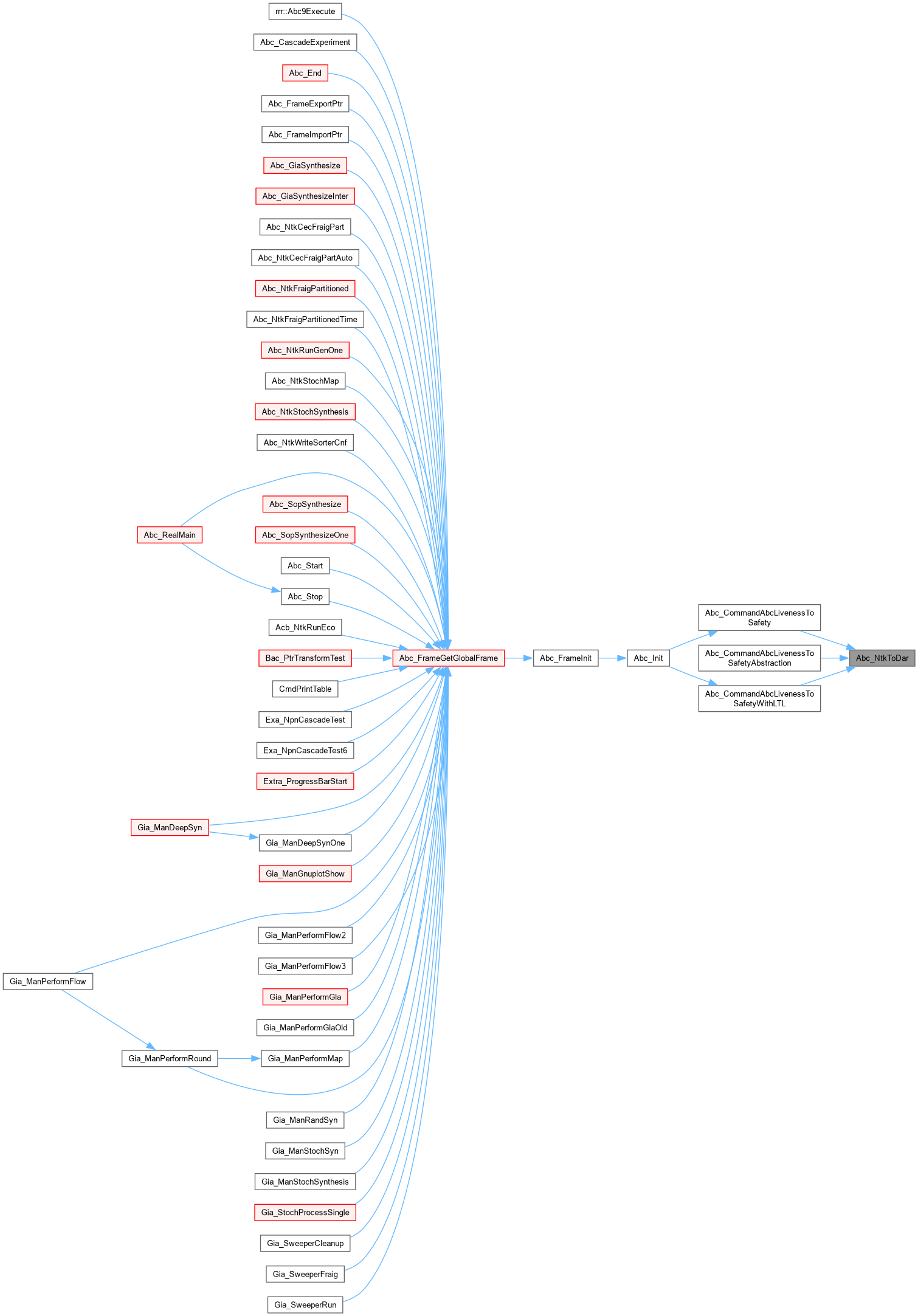

Definition at line 595 of file abcDar.c.

DECLARATIONS ///.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [Assumes that registers are ordered after PIs/POs.]

SideEffects []

SeeAlso []

Definition at line 237 of file abcDar.c.

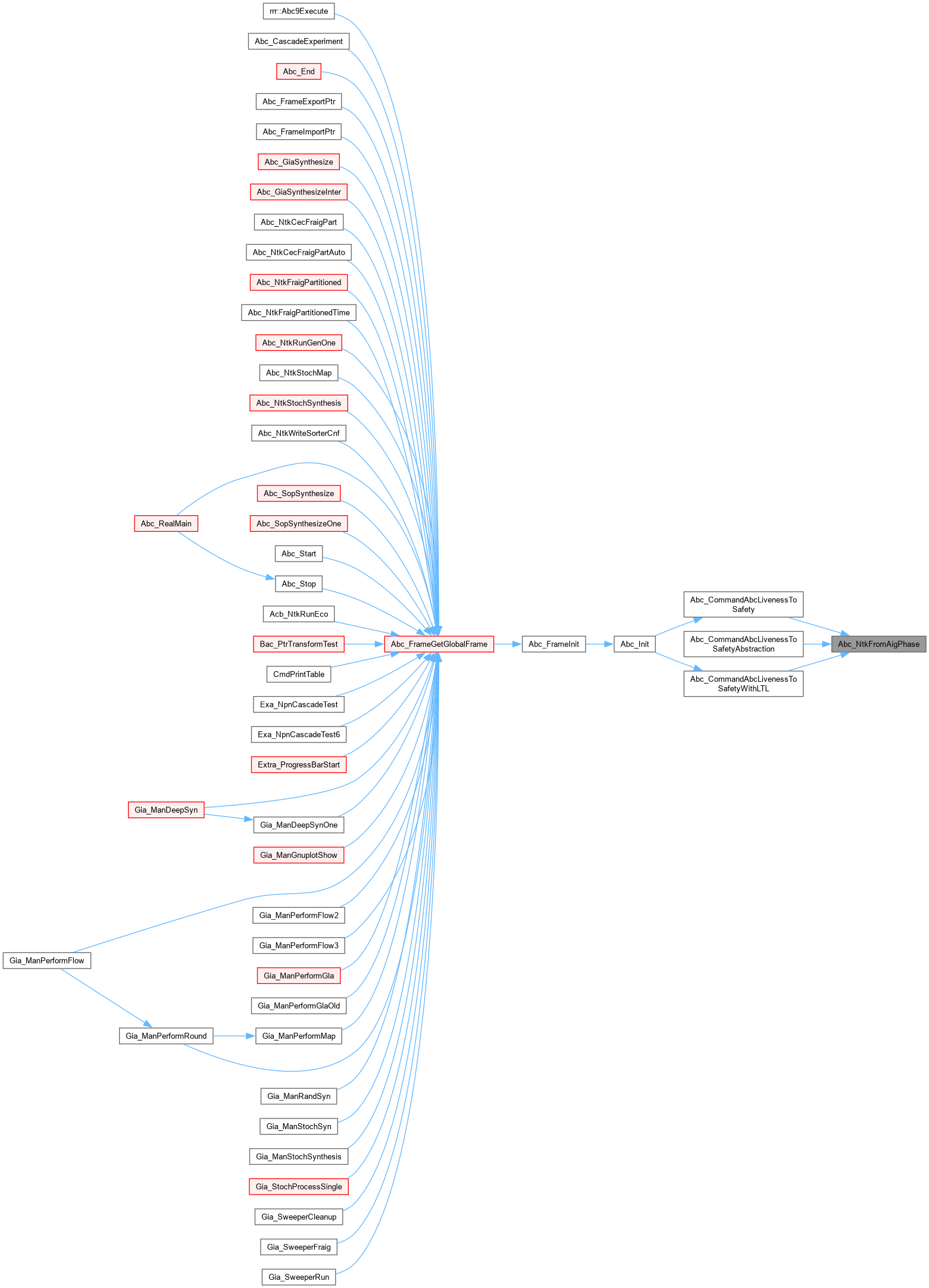

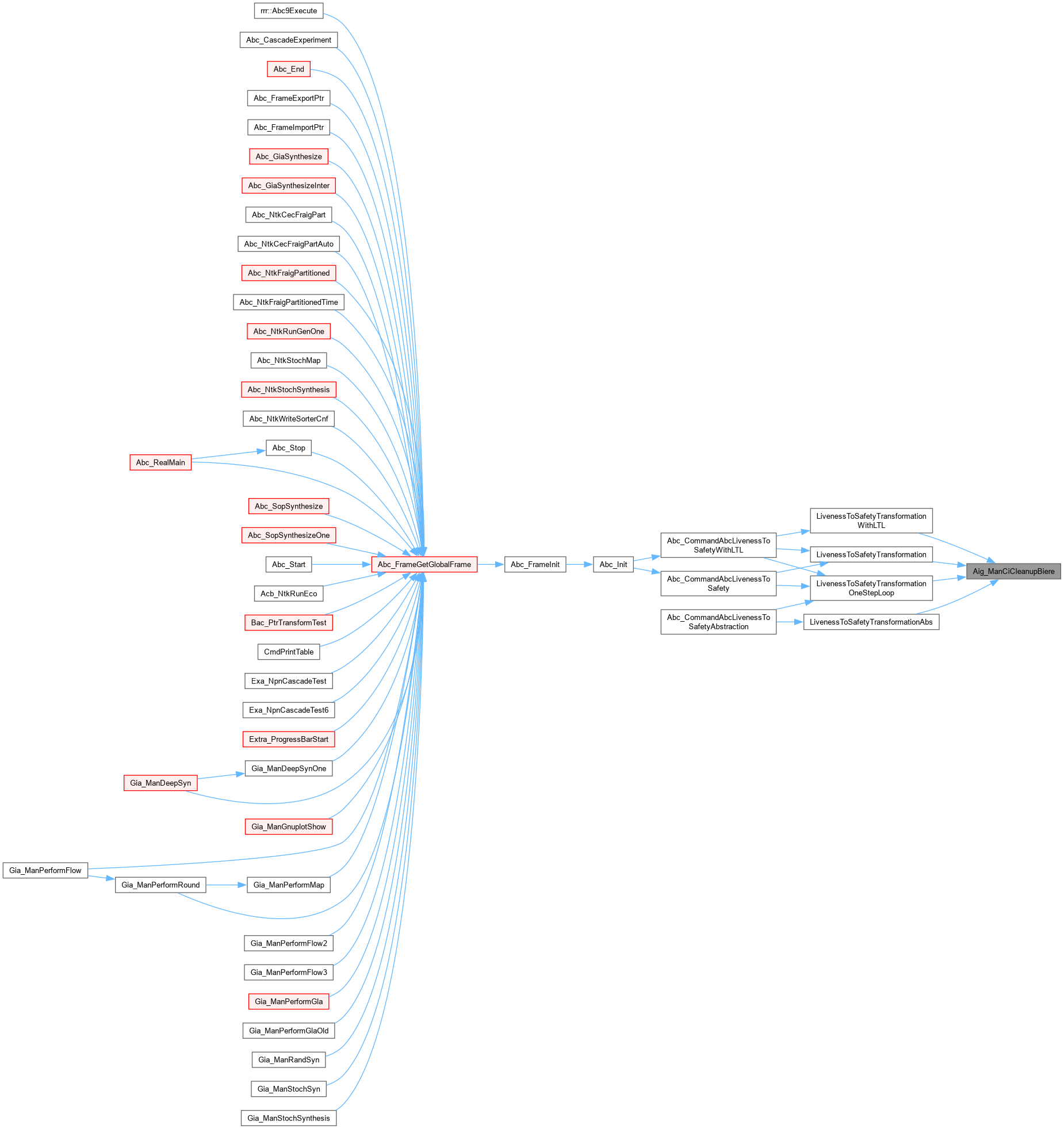

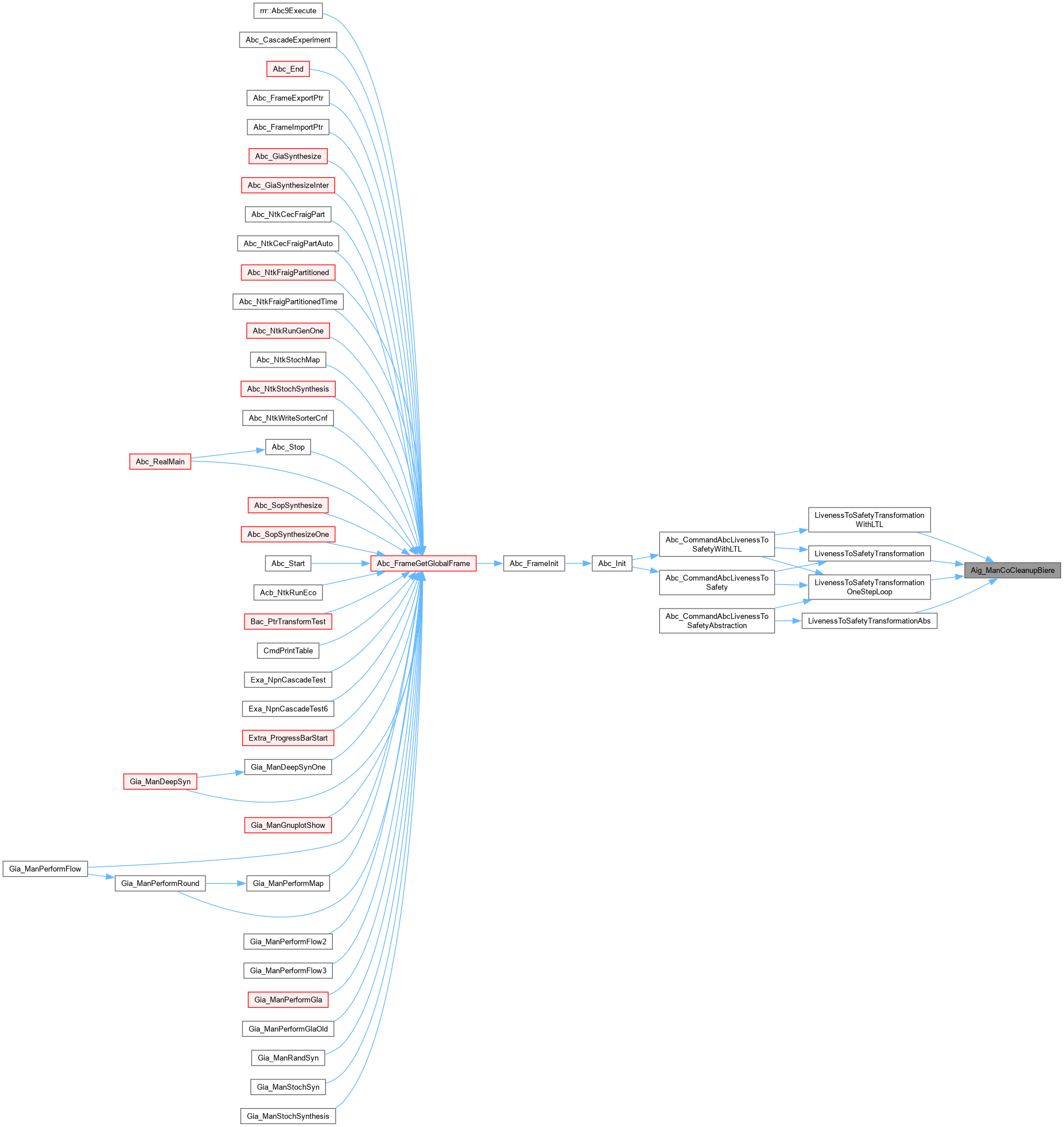

| int Aig_ManCiCleanupBiere | ( | Aig_Man_t * | p | ) |

Definition at line 222 of file liveness.c.

| int Aig_ManCoCleanupBiere | ( | Aig_Man_t * | p | ) |

Definition at line 234 of file liveness.c.

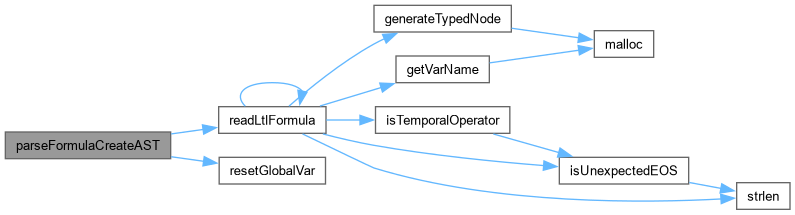

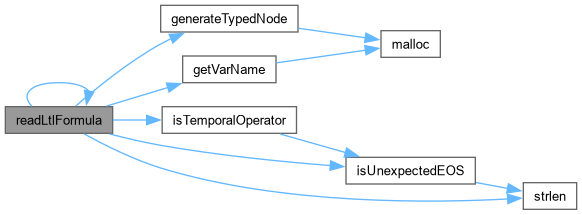

Definition at line 601 of file ltl_parser.c.

|

extern |

Definition at line 795 of file ltl_parser.c.

Definition at line 699 of file ltl_parser.c.

Definition at line 102 of file liveness.c.

|

extern |

Definition at line 661 of file ltl_parser.c.

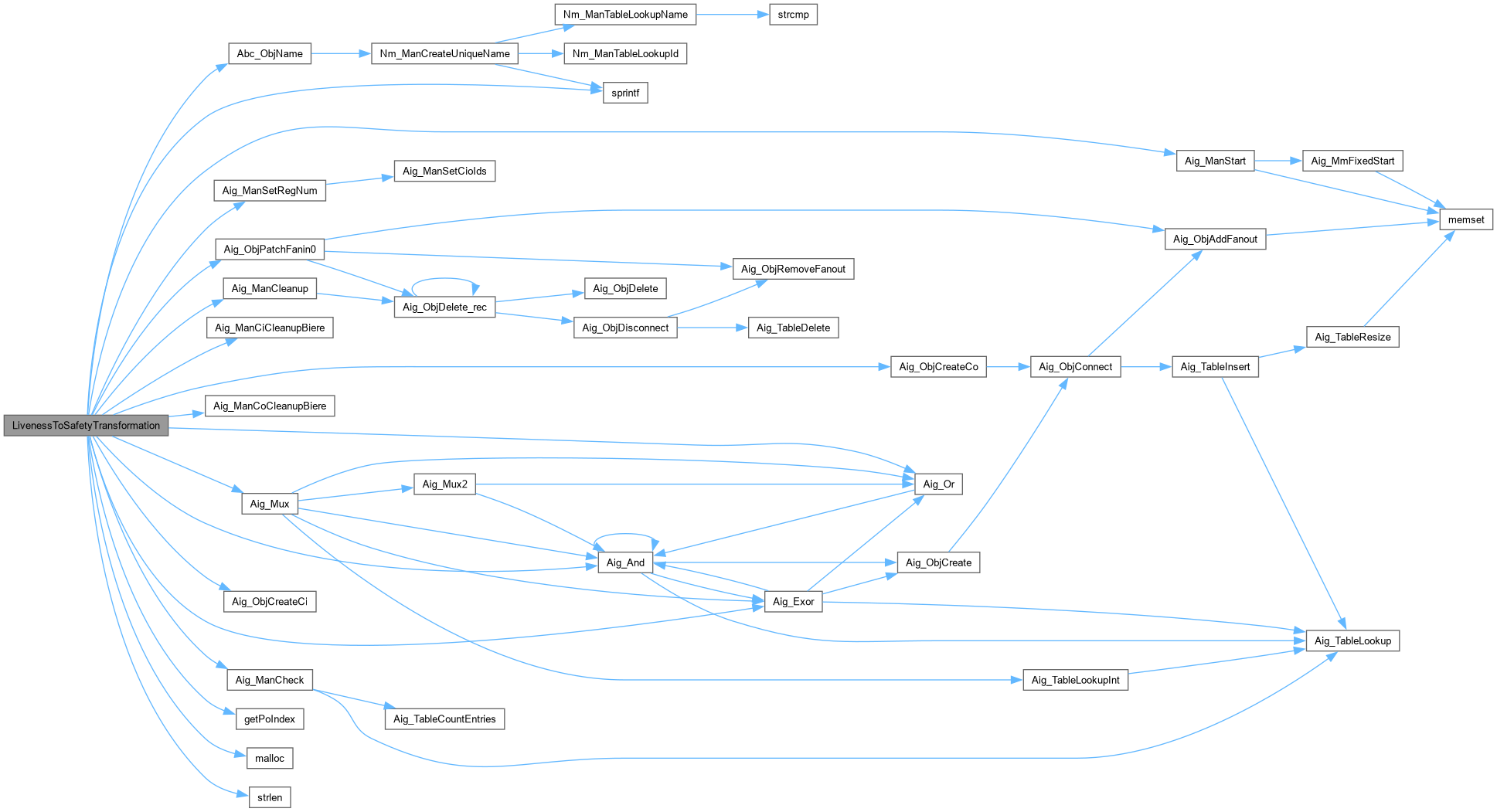

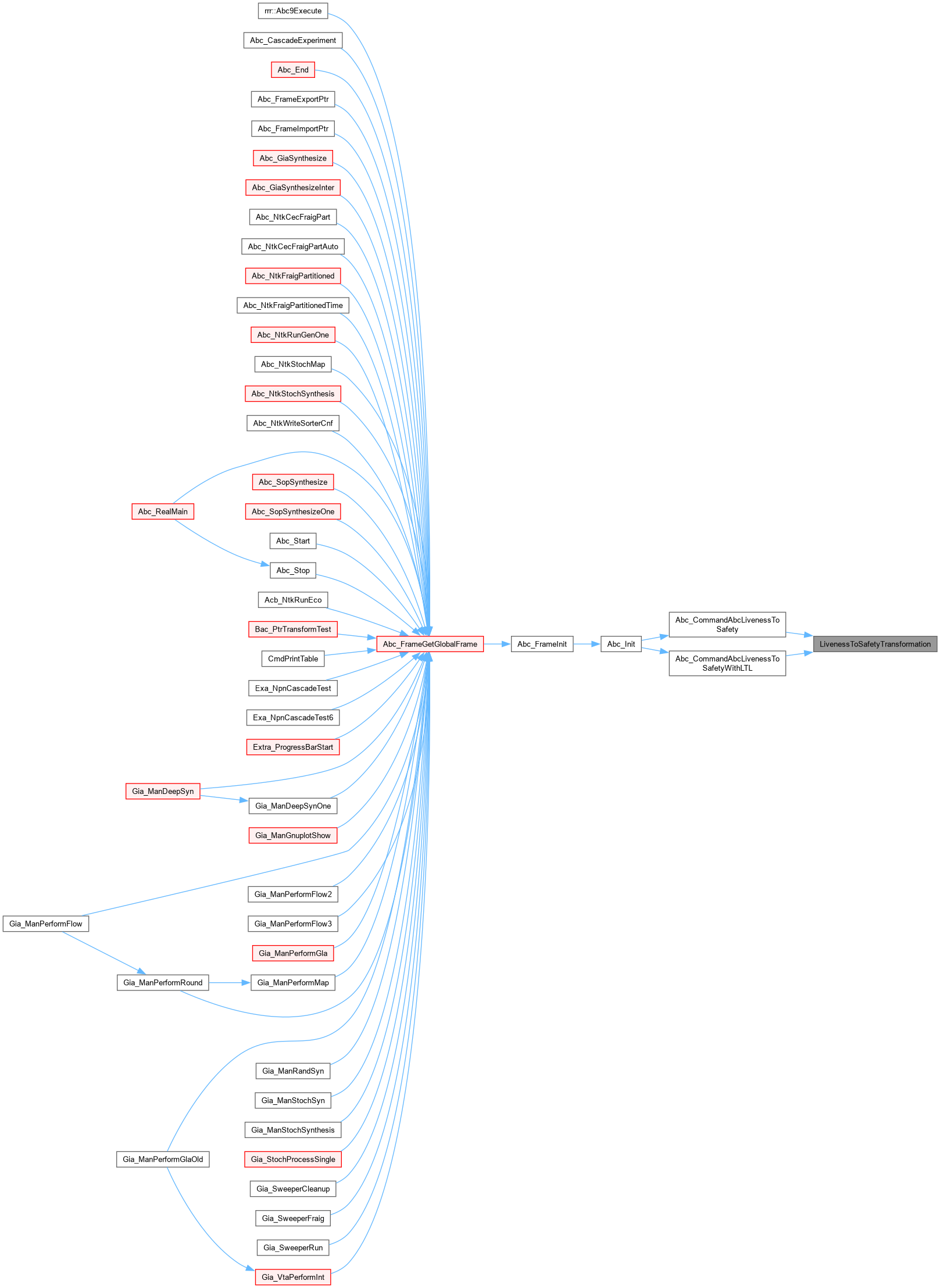

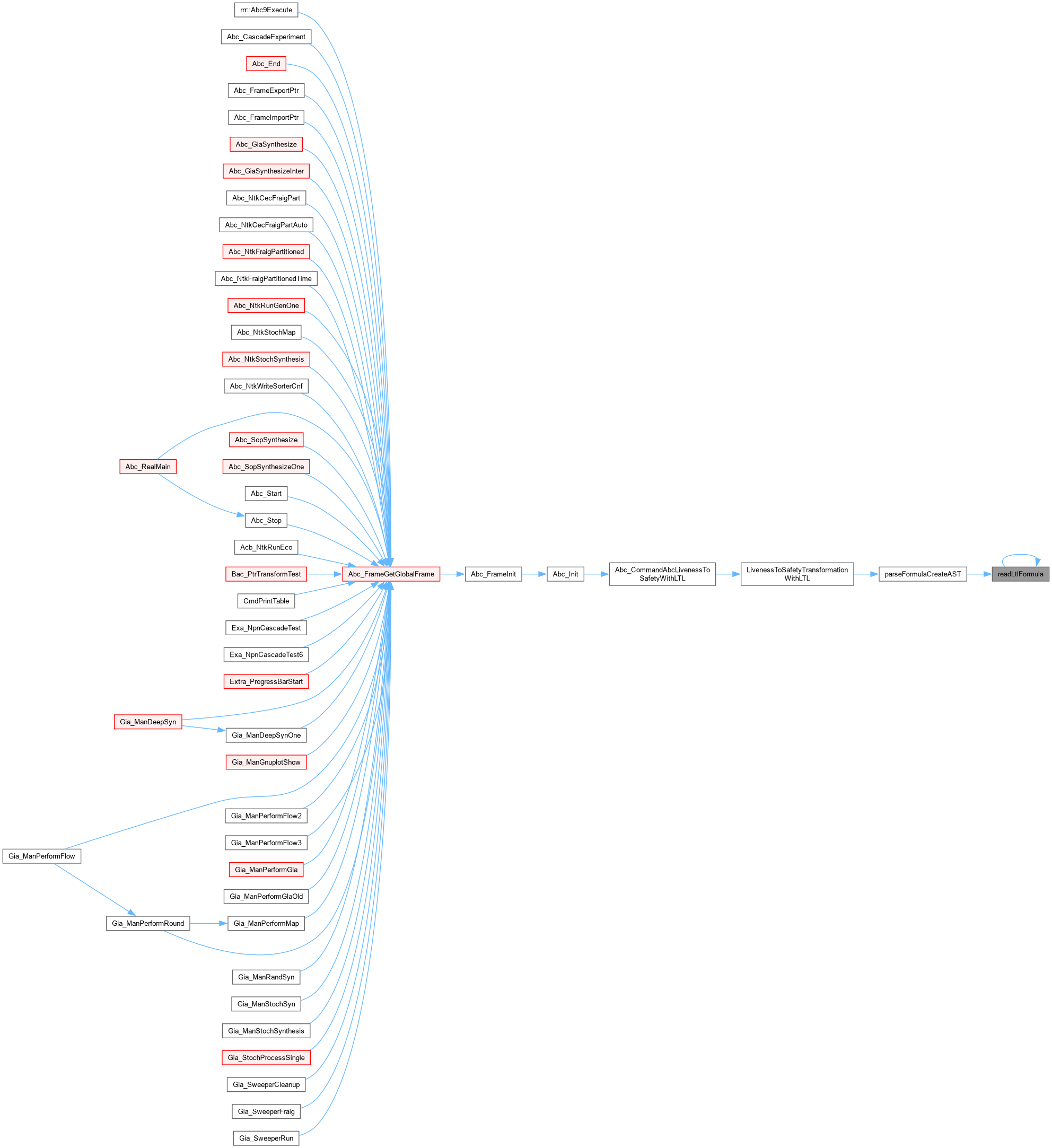

| Aig_Man_t * LivenessToSafetyTransformation | ( | int | mode, |

| Abc_Ntk_t * | pNtk, | ||

| Aig_Man_t * | p, | ||

| Vec_Ptr_t * | vLive, | ||

| Vec_Ptr_t * | vFair, | ||

| Vec_Ptr_t * | vAssertSafety, | ||

| Vec_Ptr_t * | vAssumeSafety ) |

Definition at line 244 of file liveness.c.

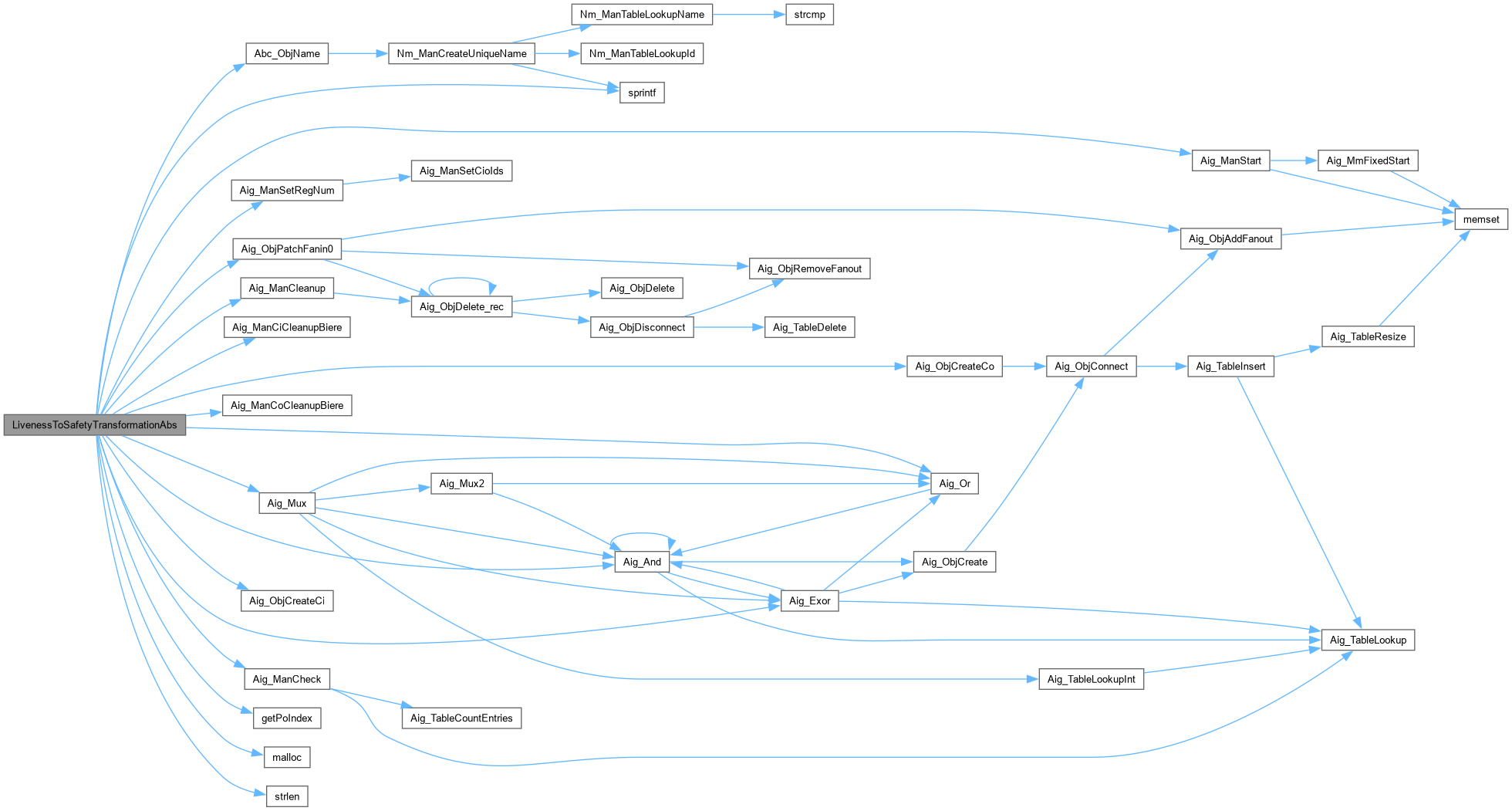

| Aig_Man_t * LivenessToSafetyTransformationAbs | ( | int | mode, |

| Abc_Ntk_t * | pNtk, | ||

| Aig_Man_t * | p, | ||

| Vec_Int_t * | vFlops, | ||

| Vec_Ptr_t * | vLive, | ||

| Vec_Ptr_t * | vFair, | ||

| Vec_Ptr_t * | vAssertSafety, | ||

| Vec_Ptr_t * | vAssumeSafety ) |

Definition at line 542 of file liveness.c.

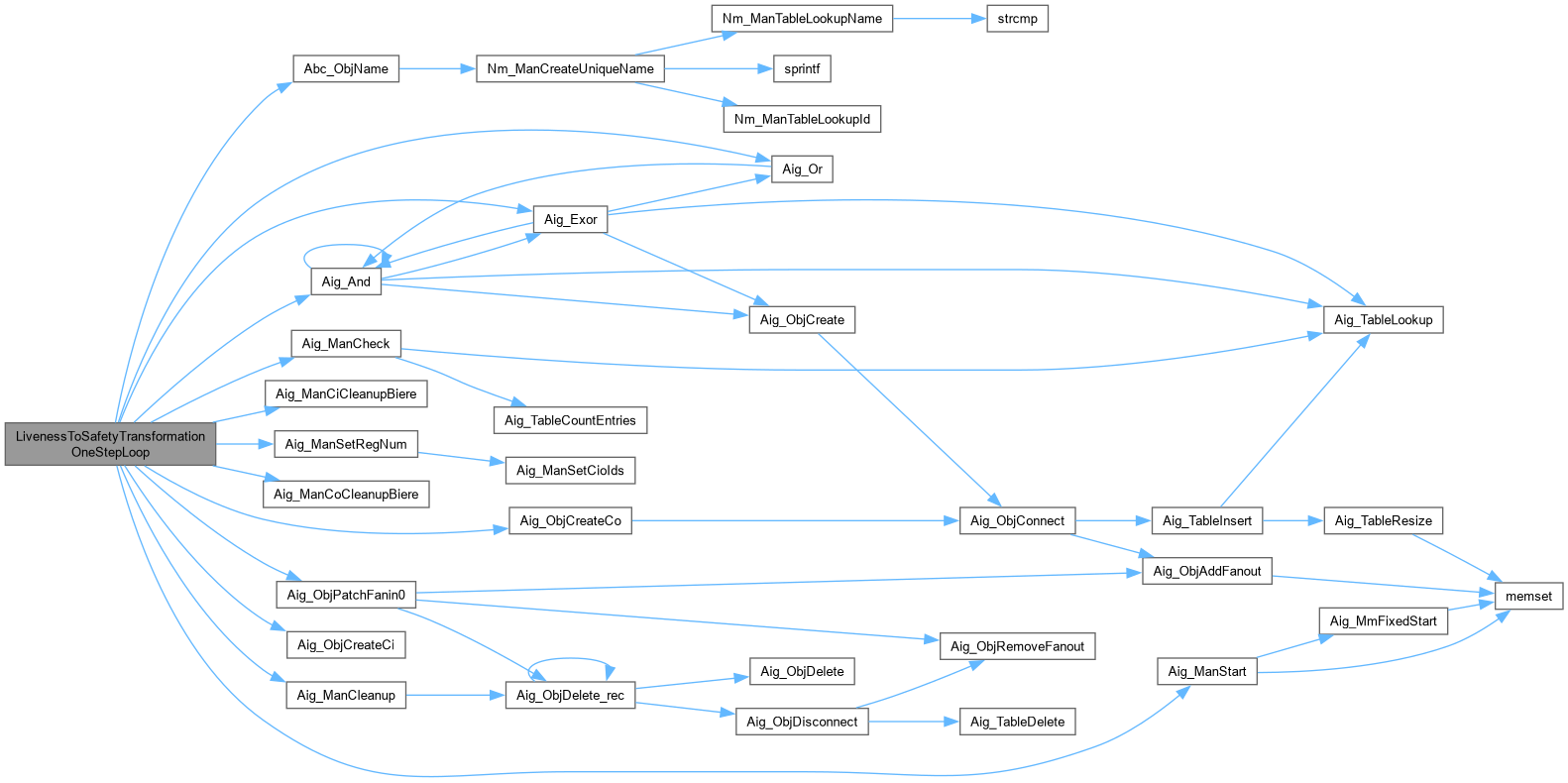

| Aig_Man_t * LivenessToSafetyTransformationOneStepLoop | ( | int | mode, |

| Abc_Ntk_t * | pNtk, | ||

| Aig_Man_t * | p, | ||

| Vec_Ptr_t * | vLive, | ||

| Vec_Ptr_t * | vFair, | ||

| Vec_Ptr_t * | vAssertSafety, | ||

| Vec_Ptr_t * | vAssumeSafety ) |

Definition at line 843 of file liveness.c.

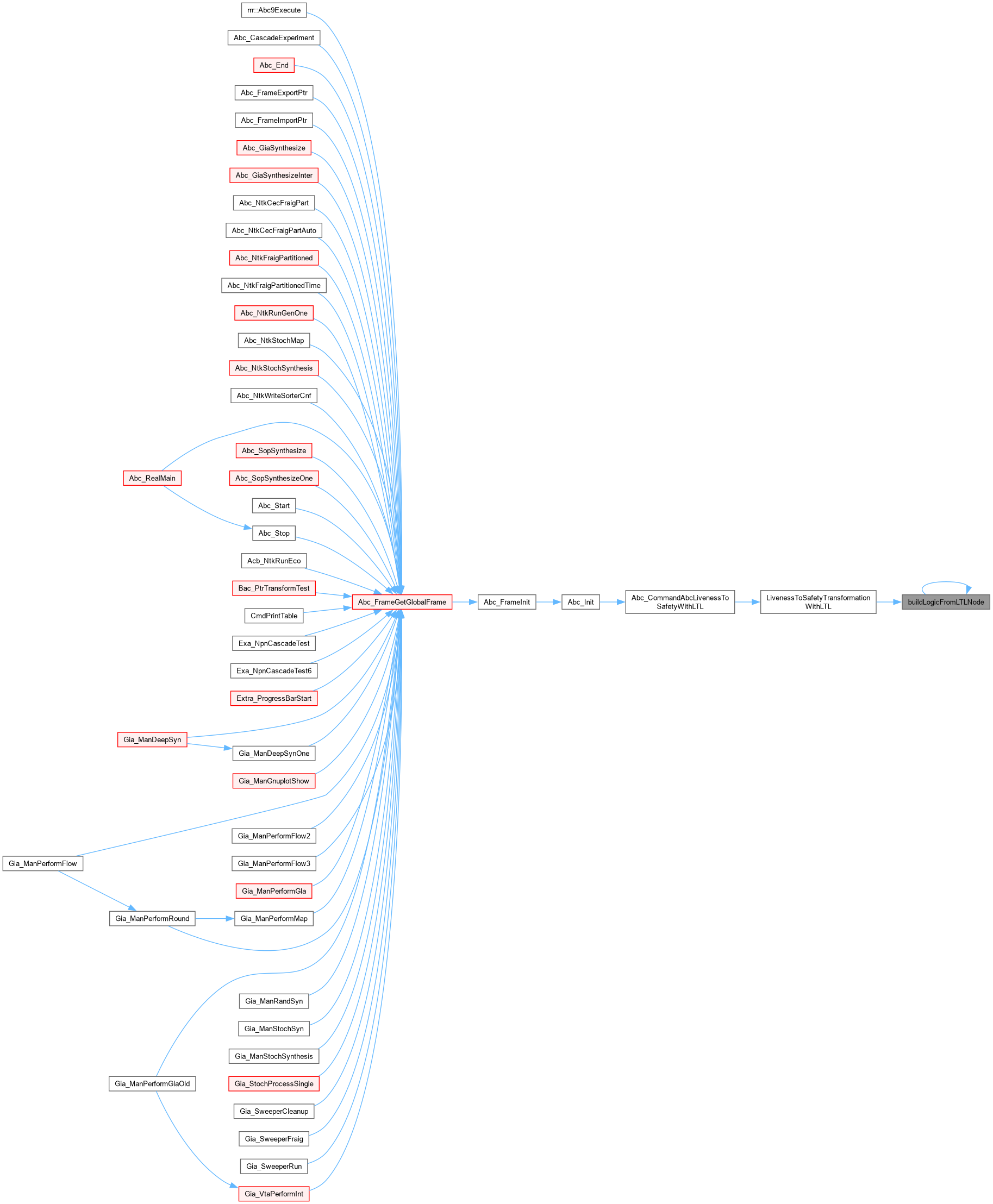

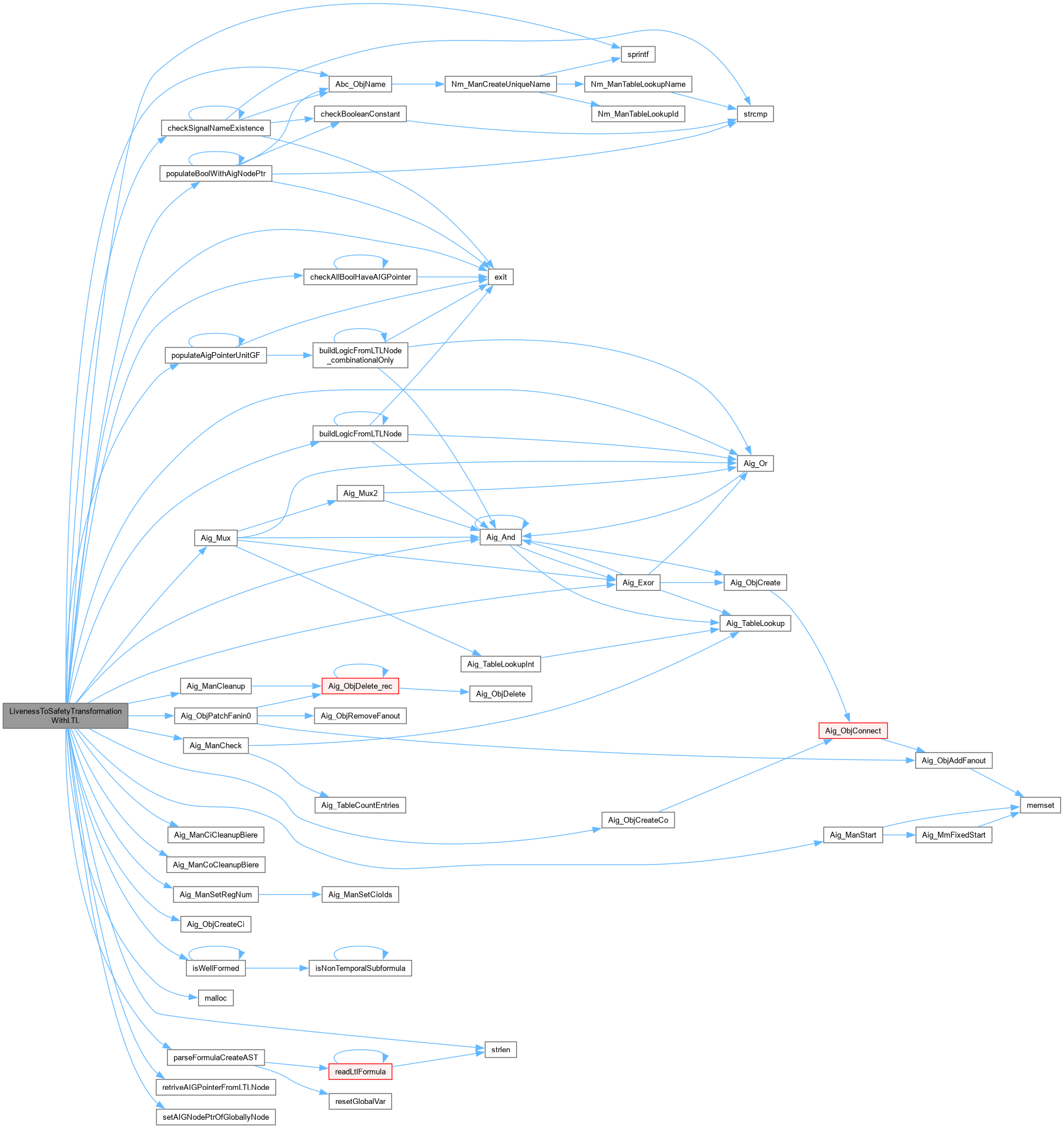

| Aig_Man_t * LivenessToSafetyTransformationWithLTL | ( | int | mode, |

| Abc_Ntk_t * | pNtk, | ||

| Aig_Man_t * | p, | ||

| Vec_Ptr_t * | vLive, | ||

| Vec_Ptr_t * | vFair, | ||

| Vec_Ptr_t * | vAssertSafety, | ||

| Vec_Ptr_t * | vAssumeSafety, | ||

| int * | numLtlProcessed, | ||

| Vec_Ptr_t * | ltlBuffer ) |

Definition at line 1798 of file liveness.c.

|

extern |

Definition at line 366 of file ltl_parser.c.

|

extern |

Definition at line 505 of file ltl_parser.c.

|

extern |

Definition at line 742 of file ltl_parser.c.

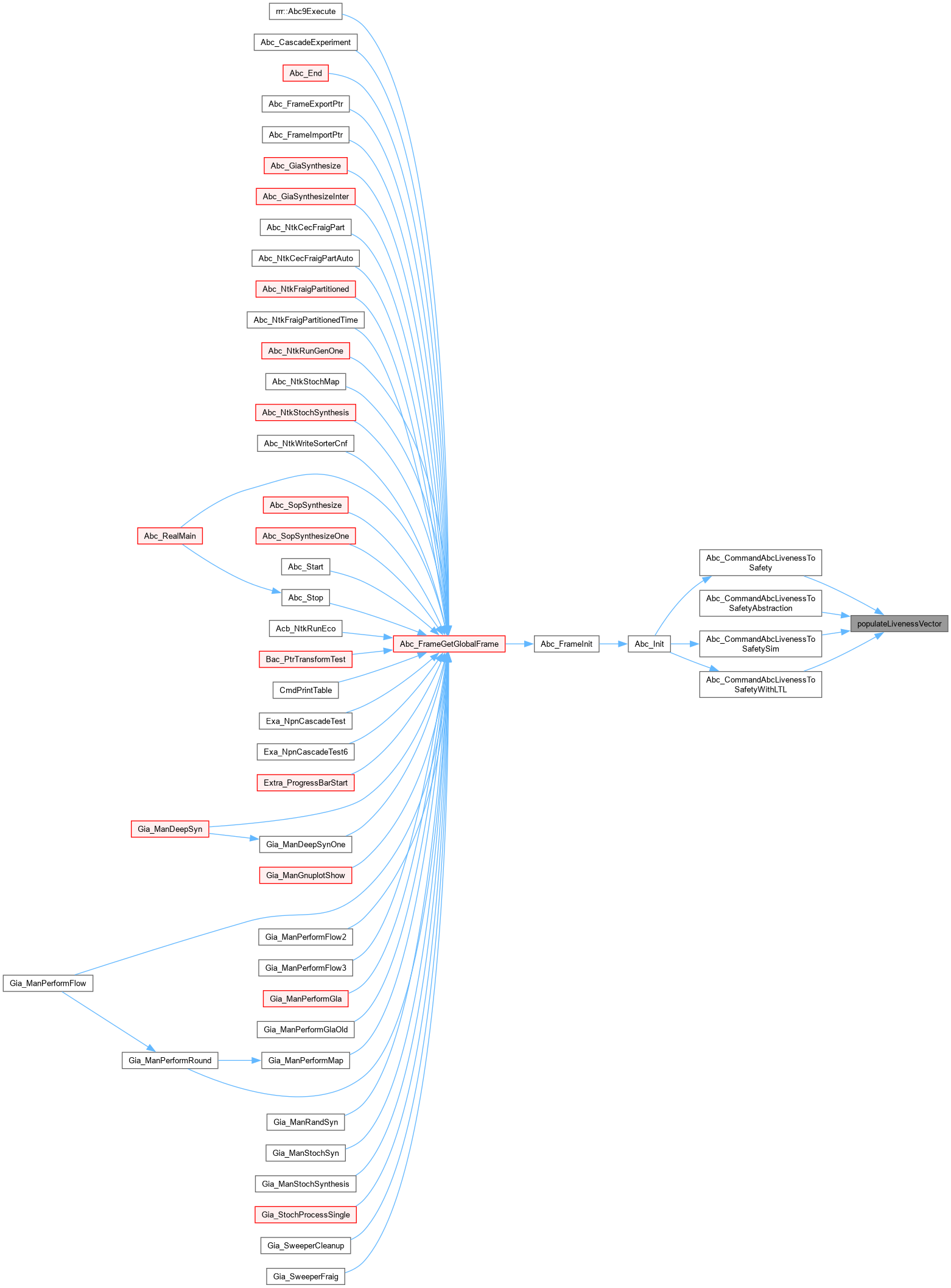

Definition at line 1161 of file liveness.c.

Definition at line 1143 of file liveness.c.

Definition at line 1179 of file liveness.c.

Definition at line 1197 of file liveness.c.

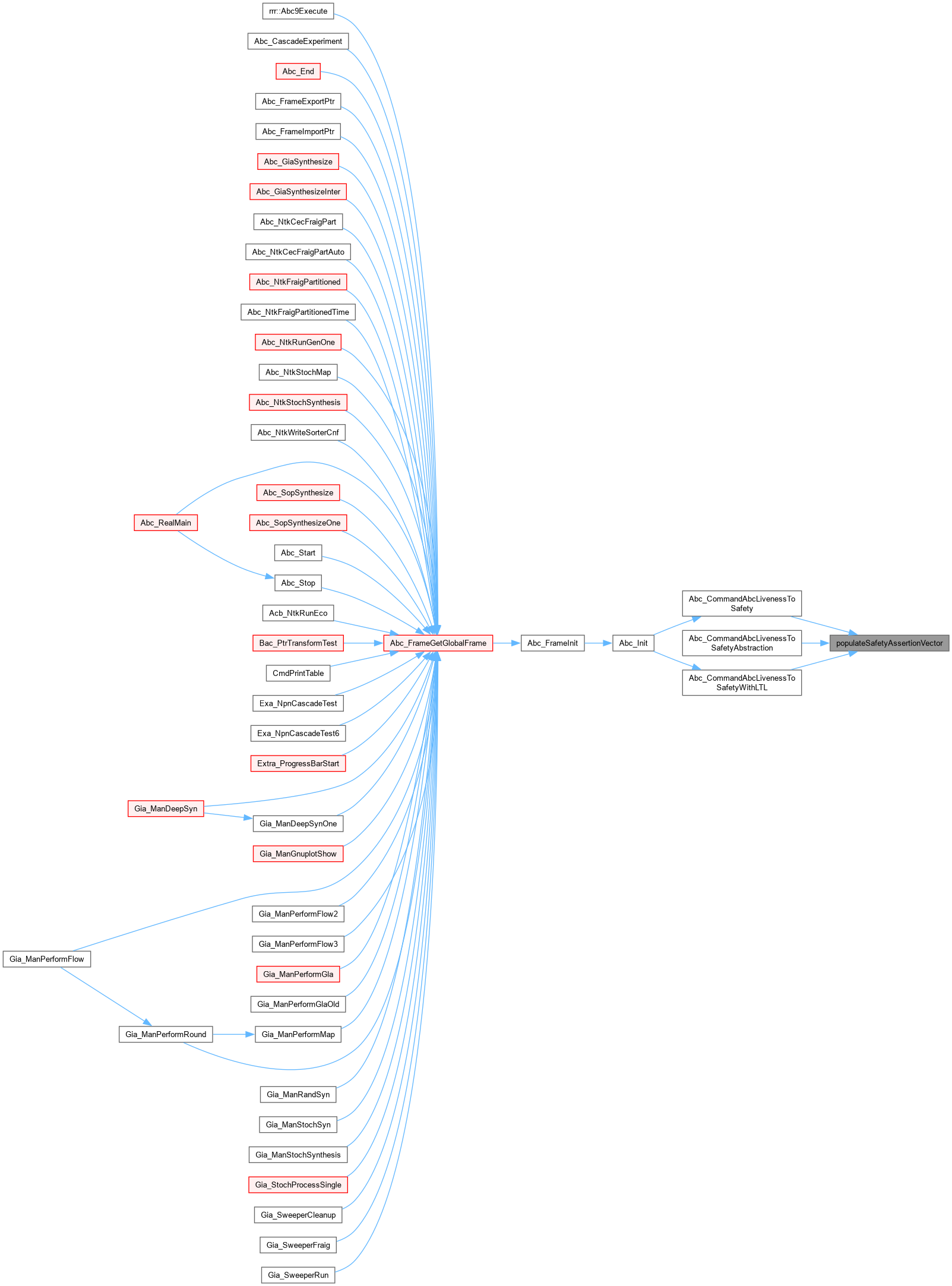

Definition at line 1569 of file liveness.c.

| void printVecPtrOfString | ( | Vec_Ptr_t * | vec | ) |

Definition at line 92 of file liveness.c.

|

extern |

Definition at line 137 of file ltl_parser.c.

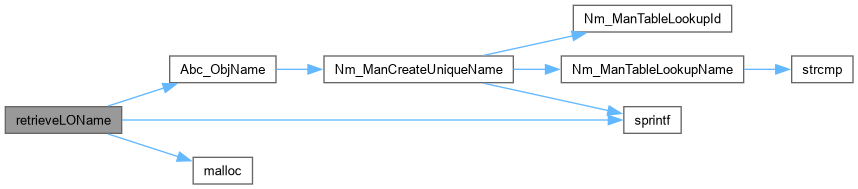

| char * retrieveLOName | ( | Abc_Ntk_t * | pNtkOld, |

| Aig_Man_t * | pAigOld, | ||

| Aig_Man_t * | pAigNew, | ||

| Aig_Obj_t * | pObjPivot, | ||

| Vec_Ptr_t * | vLive, | ||

| Vec_Ptr_t * | vFair ) |

Definition at line 137 of file liveness.c.

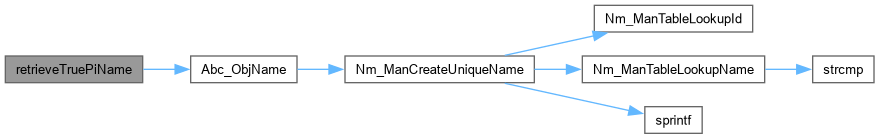

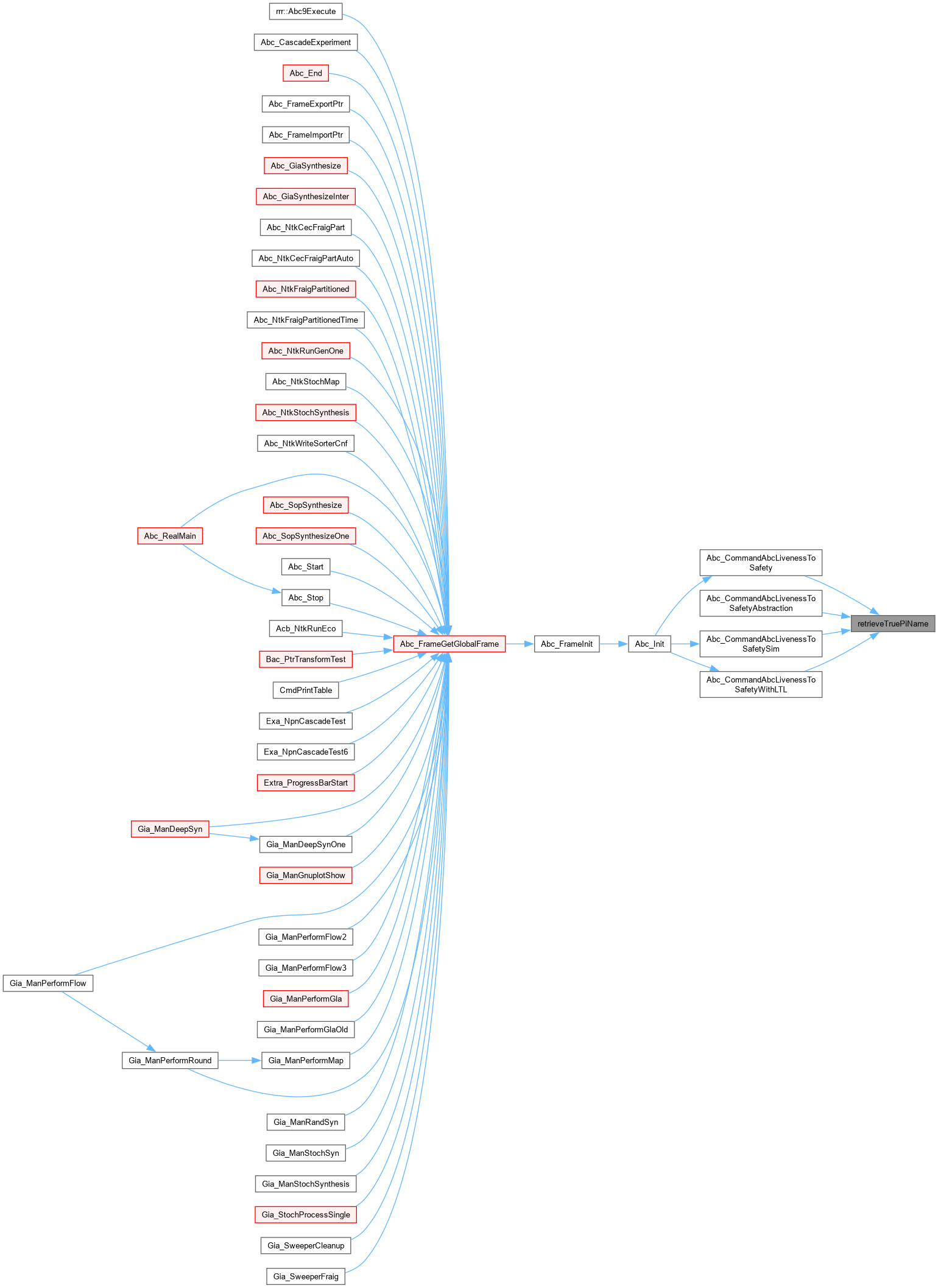

| char * retrieveTruePiName | ( | Abc_Ntk_t * | pNtkOld, |

| Aig_Man_t * | pAigOld, | ||

| Aig_Man_t * | pAigNew, | ||

| Aig_Obj_t * | pObjPivot ) |

Definition at line 115 of file liveness.c.

|

extern |

Definition at line 377 of file ltl_parser.c.

|

extern |

Definition at line 436 of file ltl_parser.c.

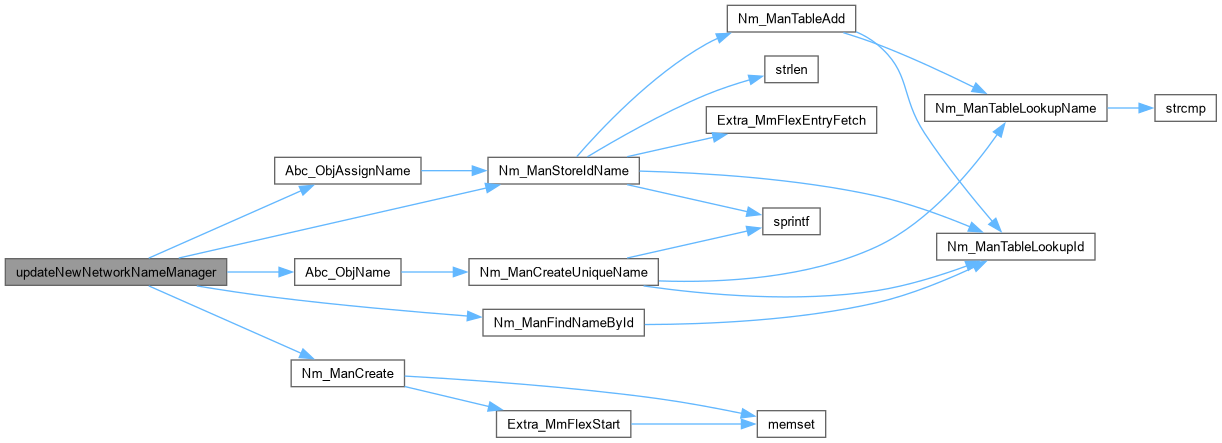

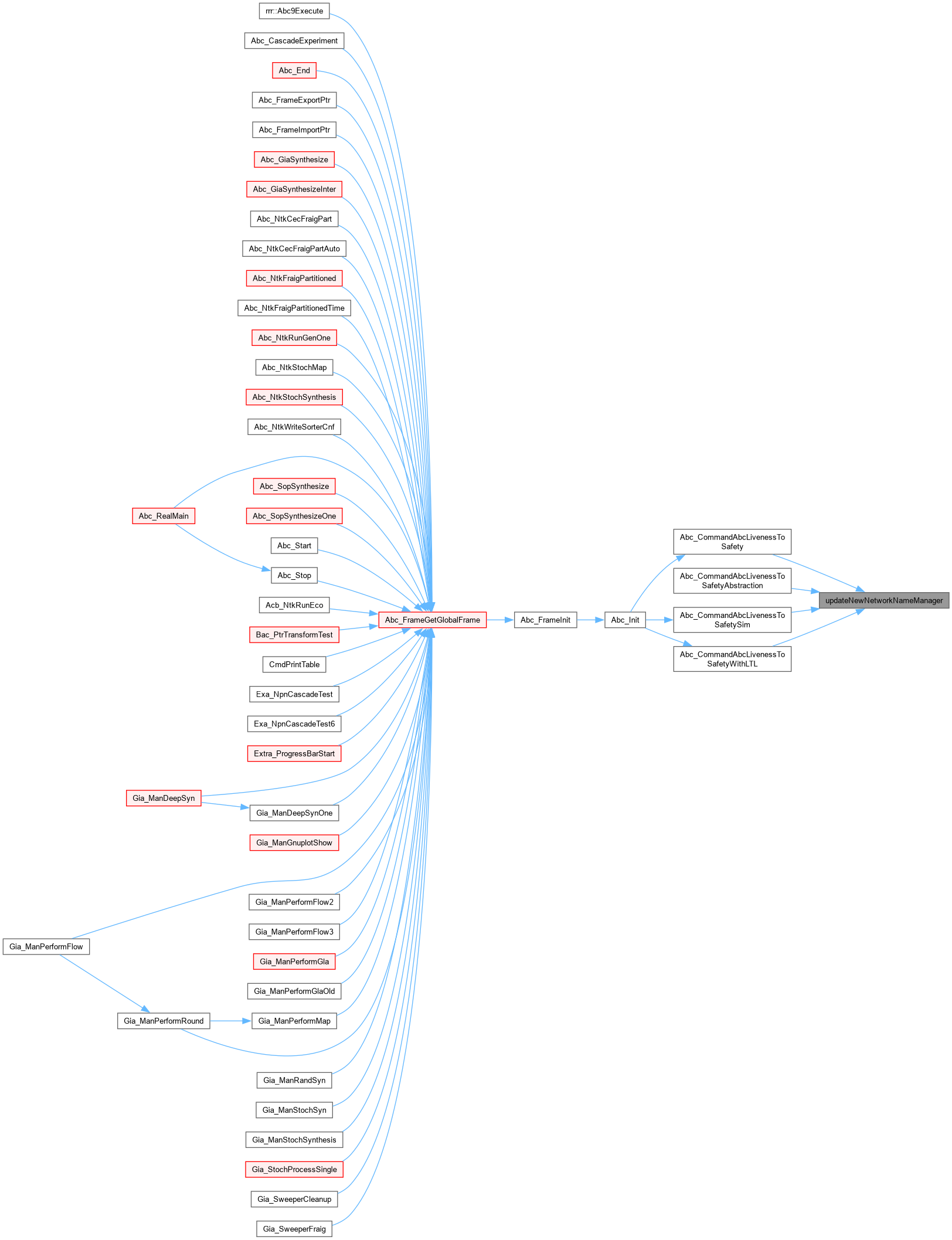

| void updateNewNetworkNameManager | ( | Abc_Ntk_t * | pNtk, |

| Aig_Man_t * | pAig, | ||

| Vec_Ptr_t * | vPiNames, | ||

| Vec_Ptr_t * | vLoNames ) |

Definition at line 1215 of file liveness.c.

| Vec_Ptr_t * vecLoNames |

Definition at line 219 of file liveness.c.

| Vec_Ptr_t* vecLos |

Definition at line 219 of file liveness.c.

| Vec_Ptr_t * vecPiNames |

Definition at line 218 of file liveness.c.

| Vec_Ptr_t* vecPis |

Definition at line 218 of file liveness.c.