#include "base/abc/abc.h"#include "base/main/main.h"#include "map/if/if.h"#include "bool/kit/kit.h"#include "aig/aig/aig.h"#include "map/mio/mio.h"

Go to the source code of this file.

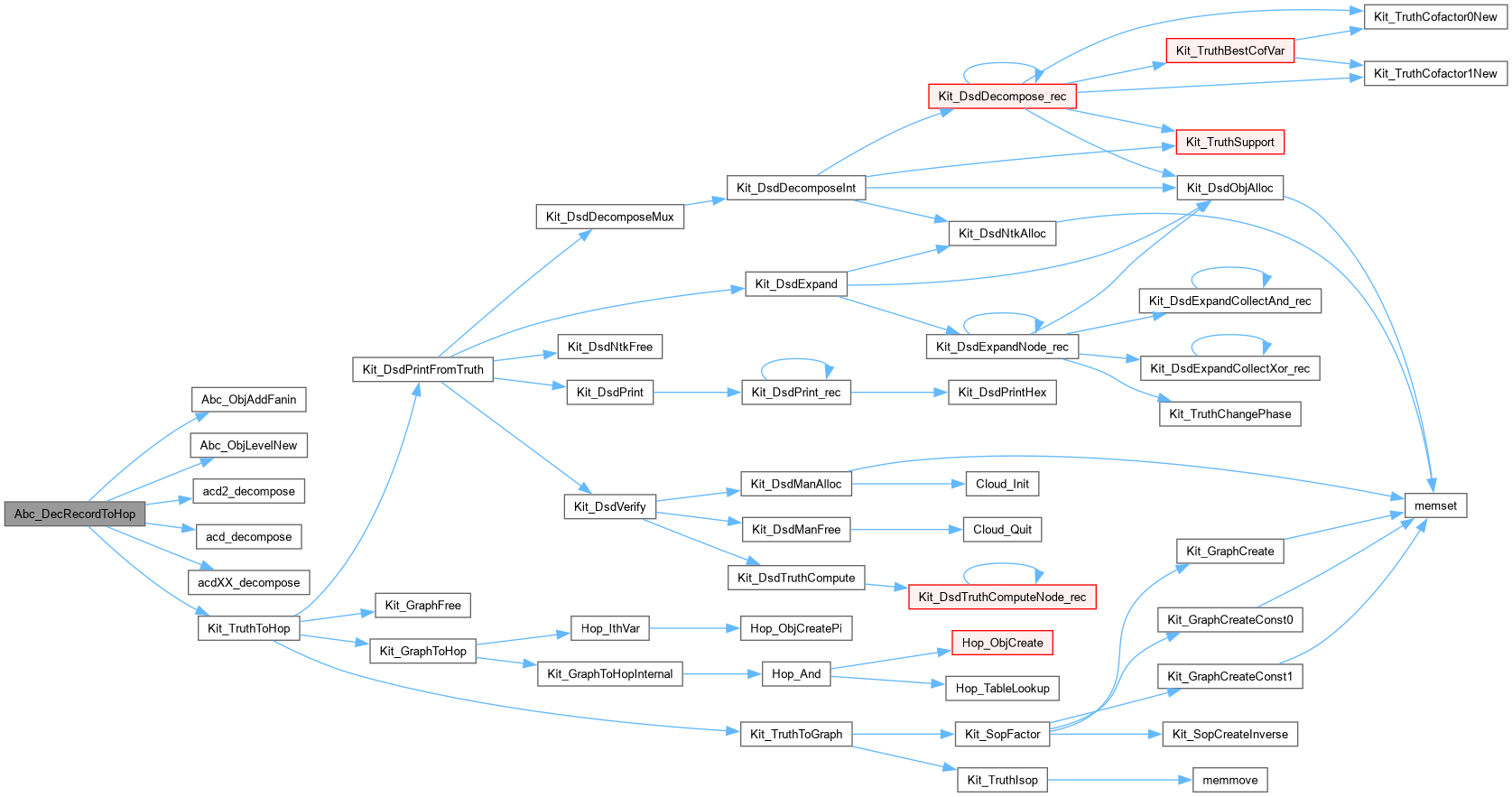

| void Abc_DecRecordToHop | ( | Abc_Ntk_t * | pNtkNew, |

| If_Man_t * | pIfMan, | ||

| If_Cut_t * | pCutBest, | ||

| If_Obj_t * | pIfObj, | ||

| Vec_Int_t * | vCover, | ||

| Abc_Obj_t * | pNodeTop ) |

Function************************************************************* Synopsis [Implements decomposed LUT-structure of the cut.] Description []

SideEffects [] SeeAlso []

Definition at line 436 of file abcIf.c.

Definition at line 418 of file abcIf.c.

Function*************************************************************

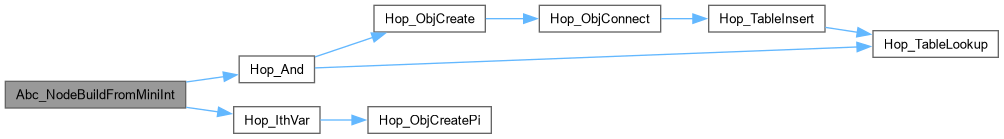

Synopsis [Rebuilds GIA from mini AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 382 of file abcIf.c.

|

extern |

Function*************************************************************

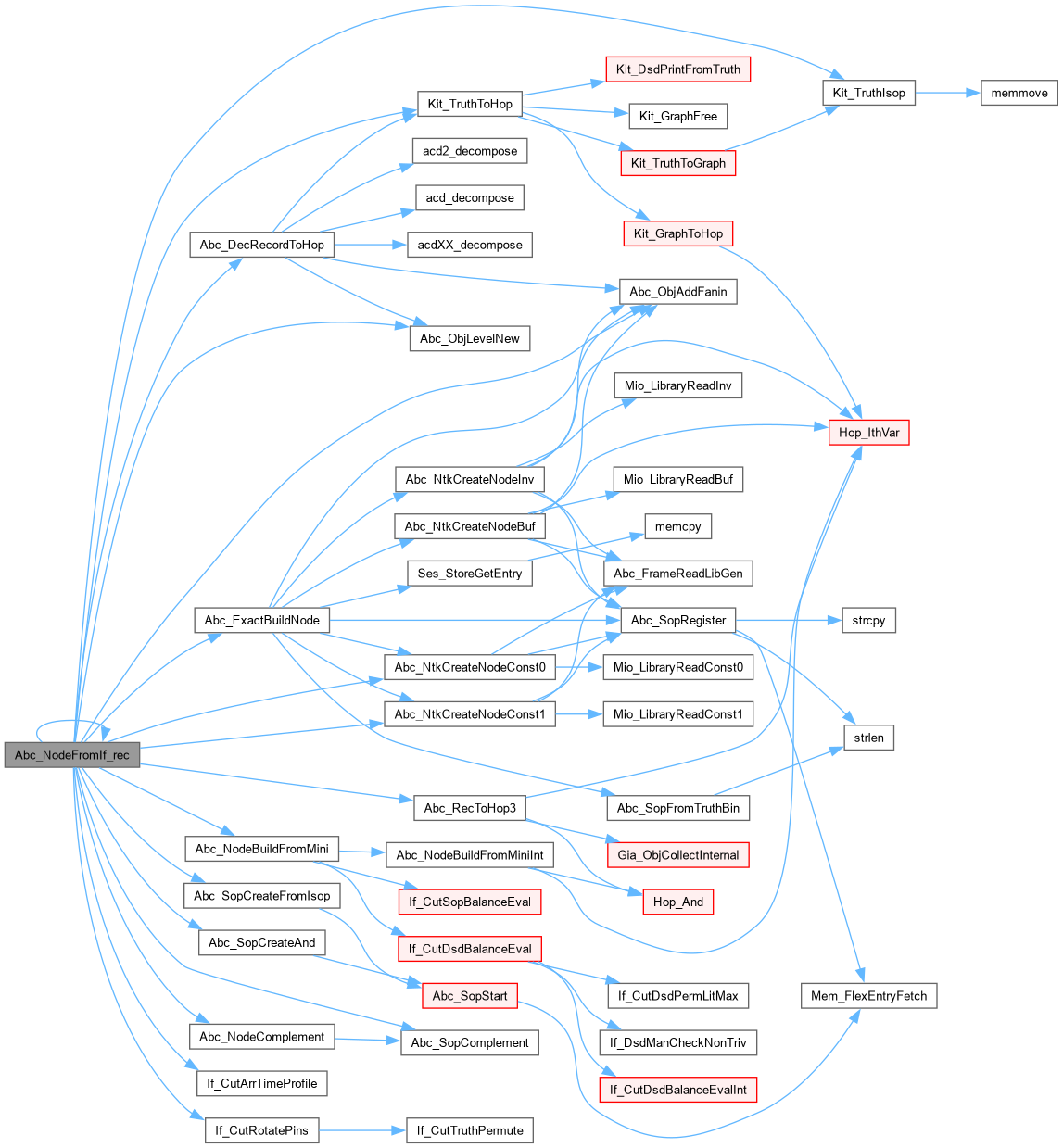

Synopsis [Derive one node after FPGA mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 565 of file abcIf.c.

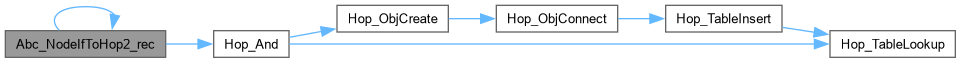

| Hop_Obj_t * Abc_NodeIfToHop2_rec | ( | Hop_Man_t * | pHopMan, |

| If_Man_t * | pIfMan, | ||

| If_Obj_t * | pIfObj, | ||

| Vec_Ptr_t * | vVisited ) |

Function*************************************************************

Synopsis [Recursively derives the truth table for the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 731 of file abcIf.c.

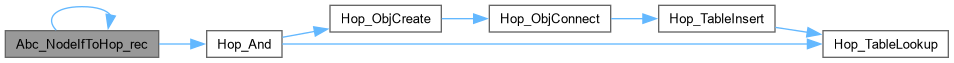

| Hop_Obj_t * Abc_NodeIfToHop_rec | ( | Hop_Man_t * | pHopMan, |

| If_Man_t * | pIfMan, | ||

| If_Obj_t * | pIfObj, | ||

| Vec_Ptr_t * | vVisited ) |

Function*************************************************************

Synopsis [Recursively derives the truth table for the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 698 of file abcIf.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [abcReorder.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Reordering local BDDs of the nodes.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] FUNCTION DEFINITIONS ///

Definition at line 107 of file abcReorder.c.

|

extern |

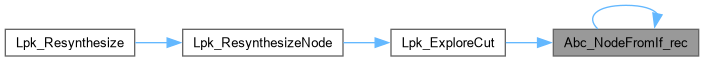

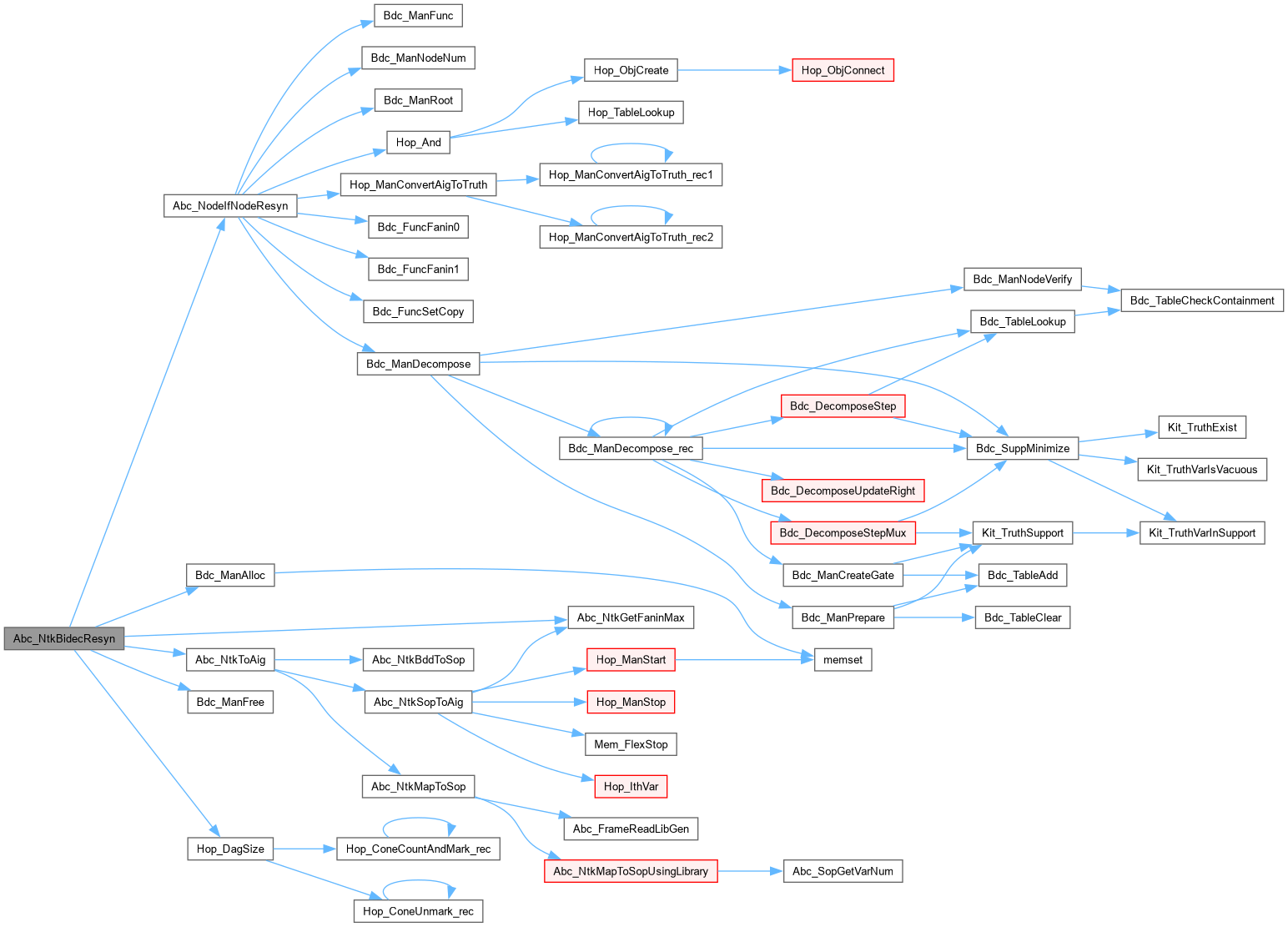

Function*************************************************************

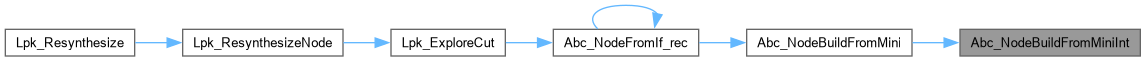

Synopsis [Resynthesizes nodes using bi-decomposition.]

Description []

SideEffects []

SeeAlso []

Definition at line 110 of file abcBidec.c.

Function*************************************************************

Synopsis [Orders AIG nodes so that nodes from larger cones go first.]

Description []

SideEffects []

SeeAlso []

Definition at line 840 of file abcIf.c.

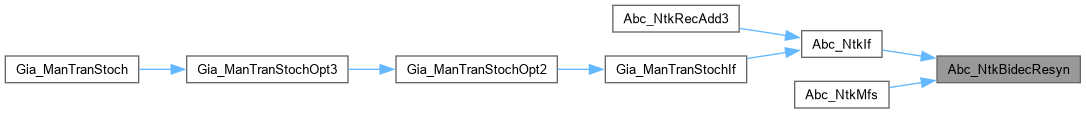

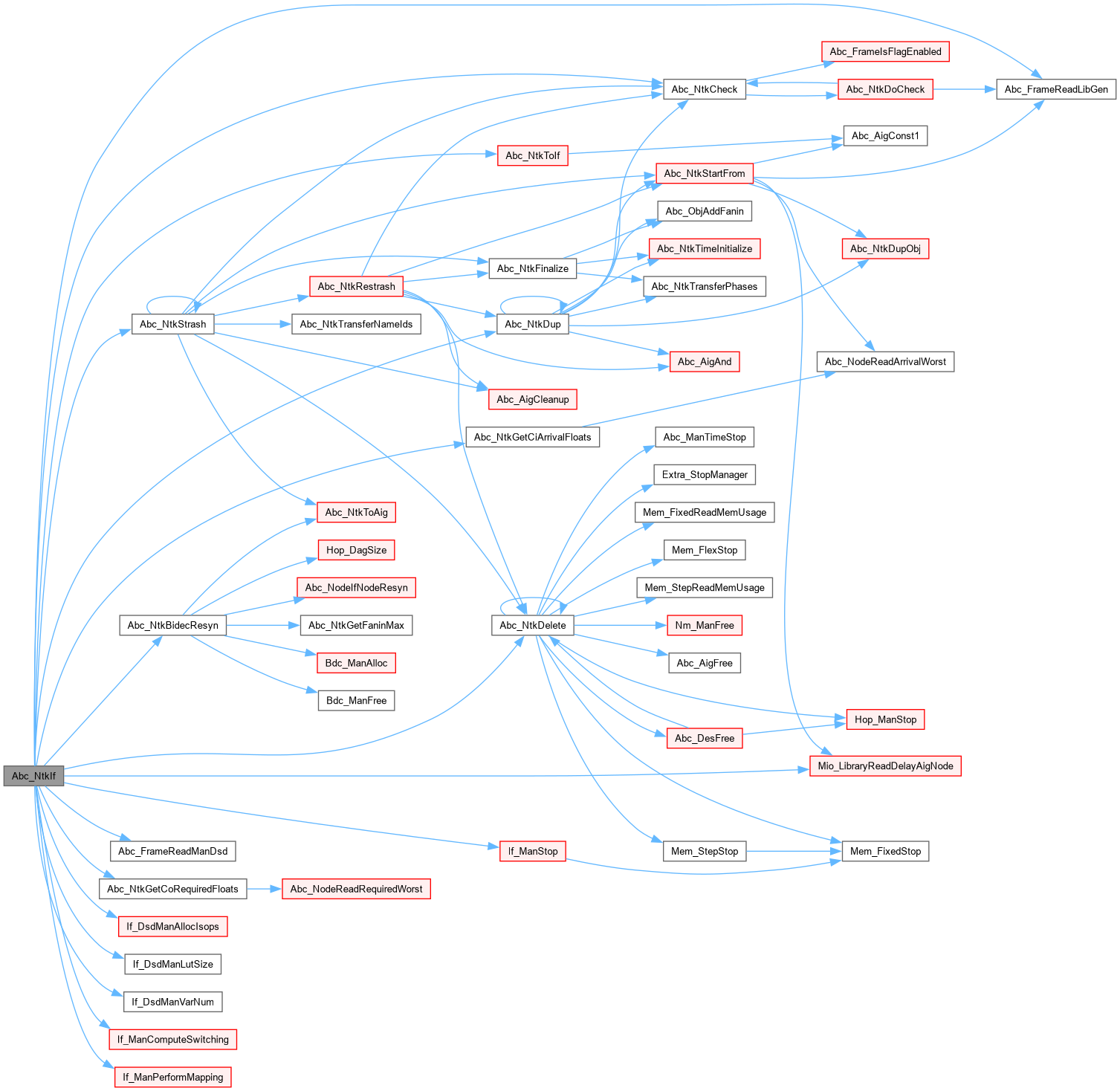

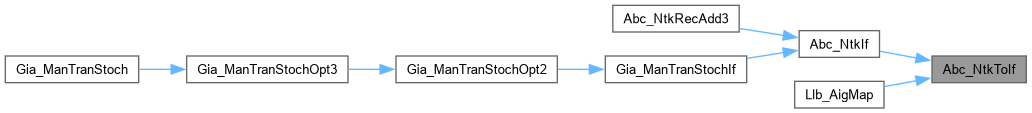

Function*************************************************************

Synopsis [Interface with the FPGA mapping package.]

Description []

SideEffects []

SeeAlso []

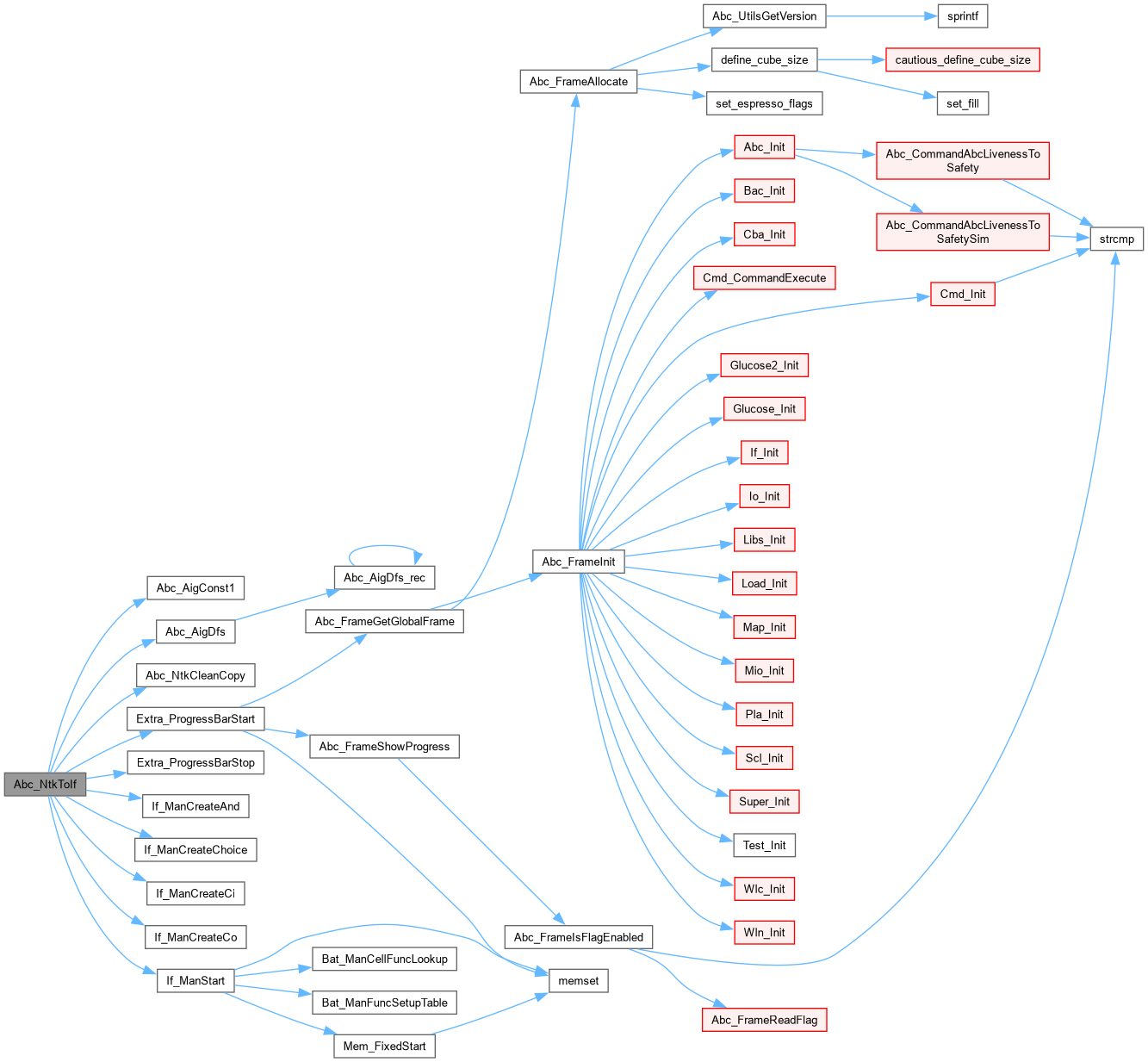

Definition at line 107 of file abcIf.c.

Function*************************************************************

Synopsis [Sets PO drivers.]

Description []

SideEffects []

SeeAlso []

Definition at line 926 of file abcIf.c.

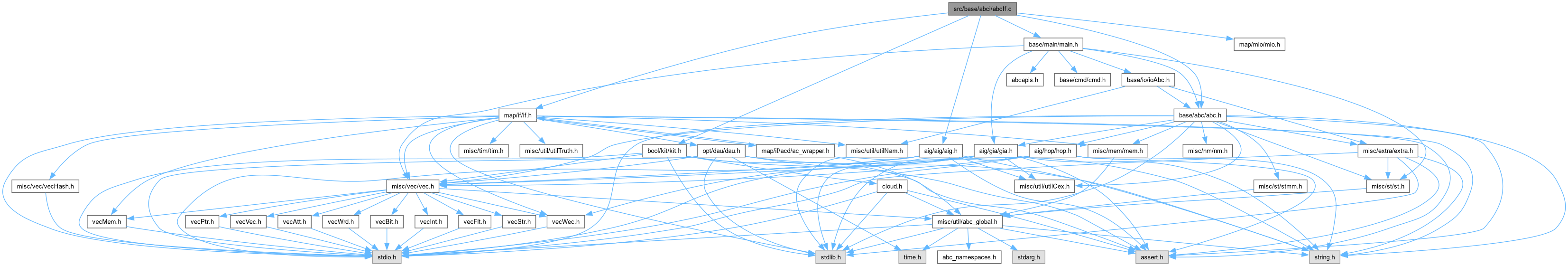

DECLARATIONS ///.

CFile****************************************************************

FileName [abcIf.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Interface with the FPGA mapping package.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - November 21, 2006.]

Revision [

]

Definition at line 209 of file abcIf.c.

Function*************************************************************

Synopsis [Comparison for two nodes with the flow.]

Description []

SideEffects []

SeeAlso []

Definition at line 818 of file abcIf.c.

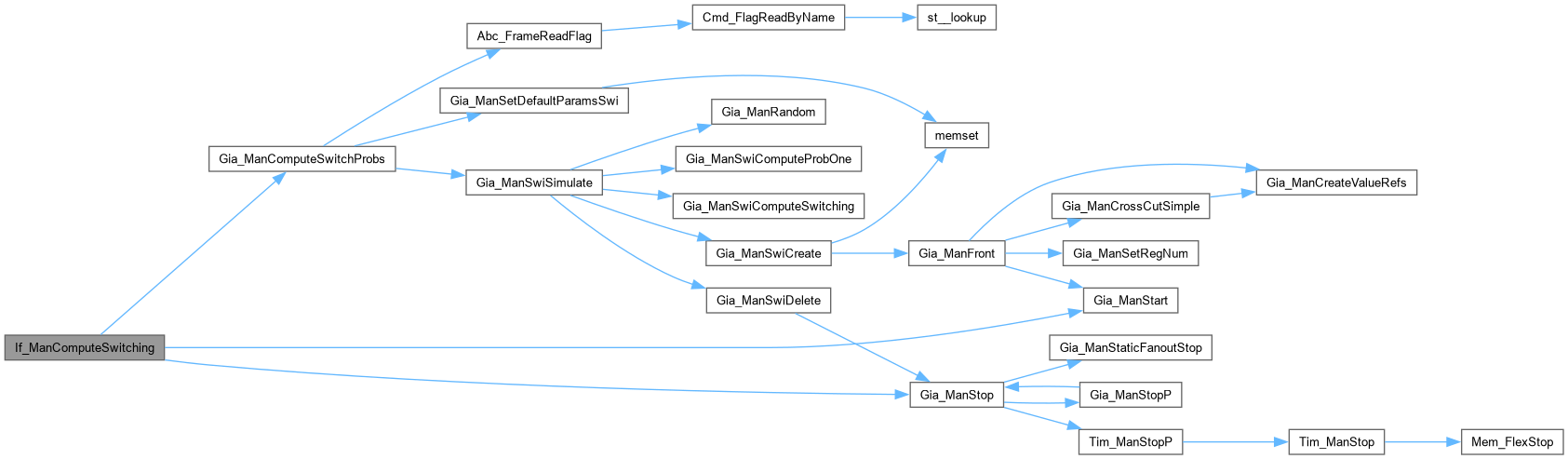

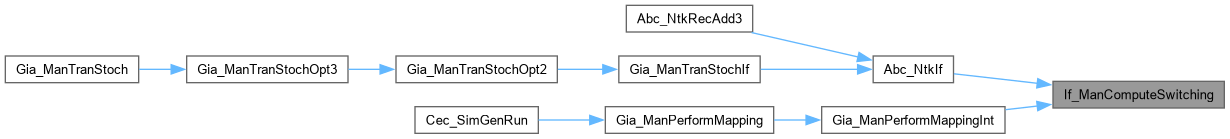

| void If_ManComputeSwitching | ( | If_Man_t * | pIfMan | ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Interface with the FPGA mapping package.]

Description []

SideEffects []

SeeAlso []

Definition at line 59 of file abcIf.c.