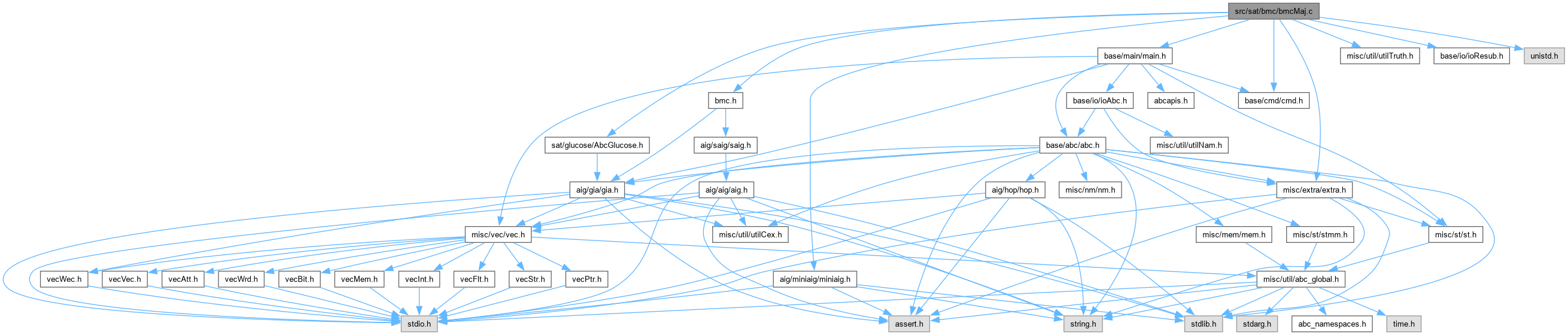

#include "bmc.h"#include "misc/extra/extra.h"#include "misc/util/utilTruth.h"#include "sat/glucose/AbcGlucose.h"#include "aig/miniaig/miniaig.h"#include "base/io/ioResub.h"#include "base/main/main.h"#include "base/cmd/cmd.h"#include <unistd.h>

Go to the source code of this file.

Classes | |

| struct | Maj_Man_t_ |

| struct | Exa_Man_t_ |

| struct | Exa3_Man_t_ |

| struct | Exa4_Man_t_ |

| struct | Exa5_Man_t_ |

| struct | Exa6_Man_t_ |

Macros | |

| #define | MAJ_NOBJS 64 |

| DECLARATIONS ///. | |

Typedefs | |

| typedef struct Maj_Man_t_ | Maj_Man_t |

| typedef struct Exa_Man_t_ | Exa_Man_t |

| typedef struct Exa3_Man_t_ | Exa3_Man_t |

| typedef struct Exa4_Man_t_ | Exa4_Man_t |

| typedef struct Exa5_Man_t_ | Exa5_Man_t |

| typedef struct Exa6_Man_t_ | Exa6_Man_t |

Functions | |

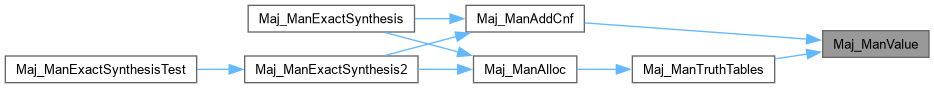

| int | Maj_ManValue (int iMint, int nVars) |

| FUNCTION DEFINITIONS ///. | |

| Vec_Wrd_t * | Maj_ManTruthTables (Maj_Man_t *p) |

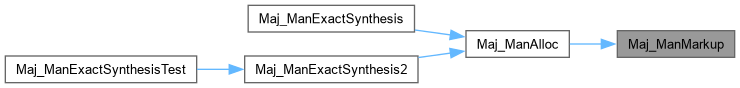

| int | Maj_ManMarkup (Maj_Man_t *p) |

| Maj_Man_t * | Maj_ManAlloc (int nVars, int nNodes, int fUseConst, int fUseLine) |

| void | Maj_ManFree (Maj_Man_t *p) |

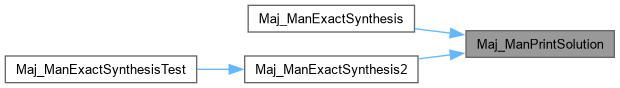

| void | Maj_ManPrintSolution (Maj_Man_t *p) |

| int | Maj_ManAddCnfStart (Maj_Man_t *p) |

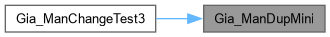

| int | Maj_ManAddCnf (Maj_Man_t *p, int iMint) |

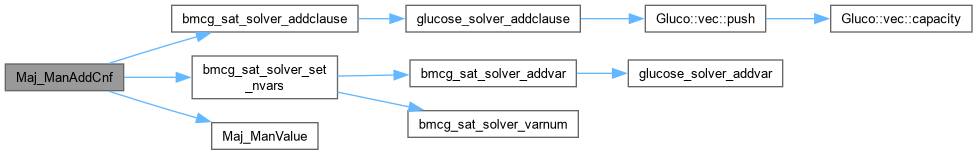

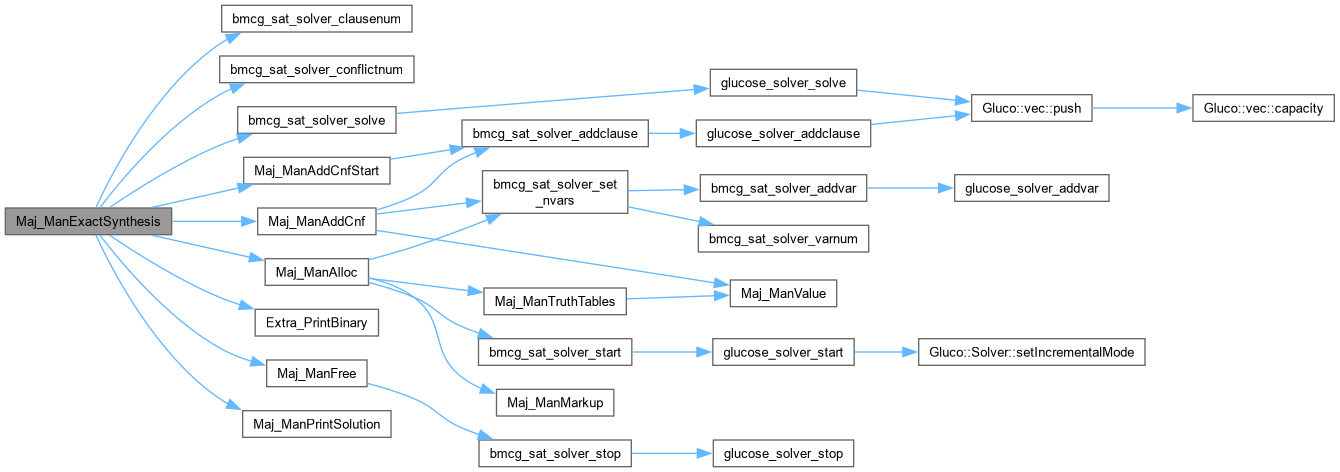

| int | Maj_ManExactSynthesis (int nVars, int nNodes, int fUseConst, int fUseLine, int fVerbose) |

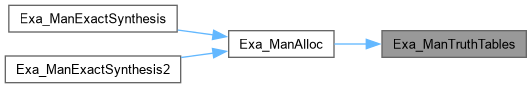

| Vec_Wrd_t * | Exa_ManTruthTables (Exa_Man_t *p) |

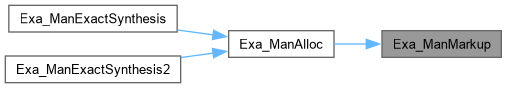

| int | Exa_ManMarkup (Exa_Man_t *p) |

| Exa_Man_t * | Exa_ManAlloc (Bmc_EsPar_t *pPars, word *pTruth) |

| void | Exa_ManFree (Exa_Man_t *p) |

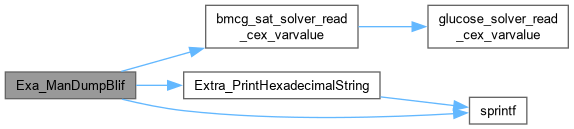

| void | Exa_ManDumpBlif (Exa_Man_t *p, int fCompl) |

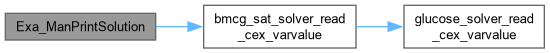

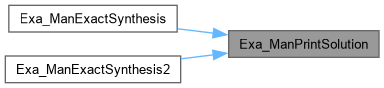

| void | Exa_ManPrintSolution (Exa_Man_t *p, int fCompl) |

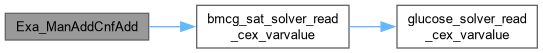

| int | Exa_ManAddCnfAdd (Exa_Man_t *p, int *pnAdded) |

| int | Exa_ManSolverSolve (Exa_Man_t *p) |

| int | Exa_ManAddCnfStart (Exa_Man_t *p, int fOnlyAnd) |

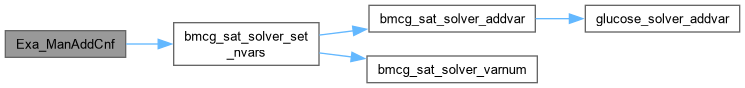

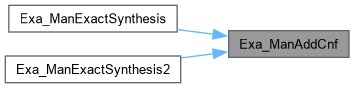

| int | Exa_ManAddCnf (Exa_Man_t *p, int iMint) |

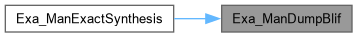

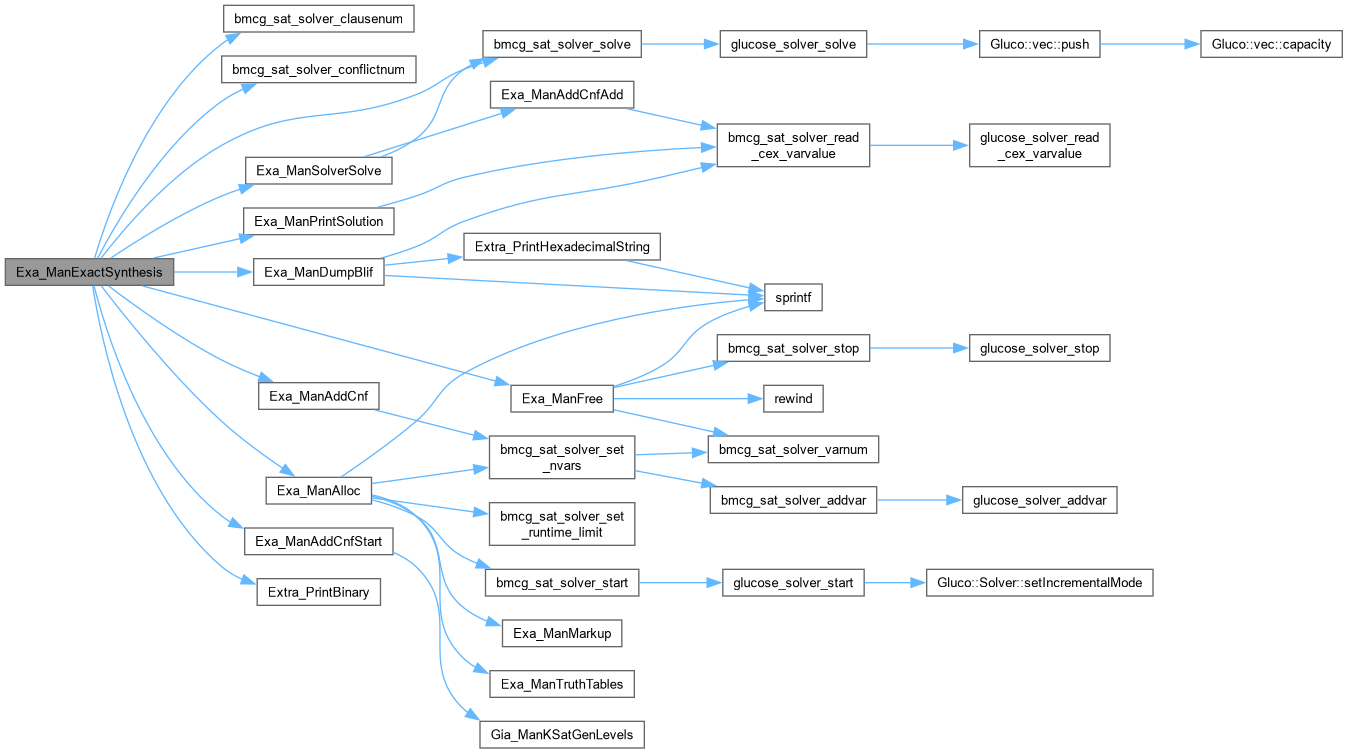

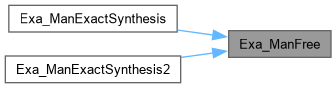

| void | Exa_ManExactSynthesis (Bmc_EsPar_t *pPars) |

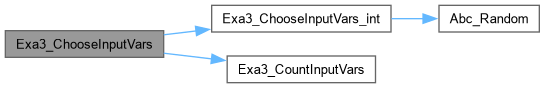

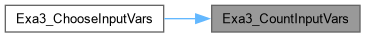

| Vec_Wec_t * | Exa3_ChooseInputVars_int (int nVars, int nLuts, int nLutSize) |

| Vec_Int_t * | Exa3_CountInputVars (int nVars, Vec_Wec_t *p) |

| Vec_Wec_t * | Exa3_ChooseInputVars (int nVars, int nLuts, int nLutSize) |

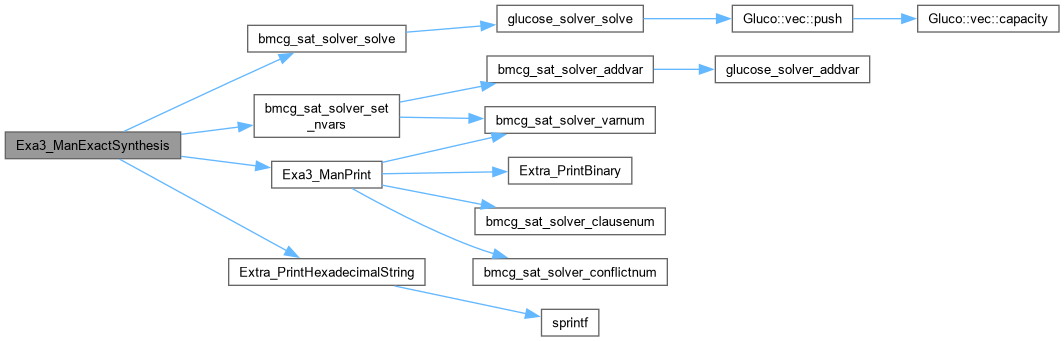

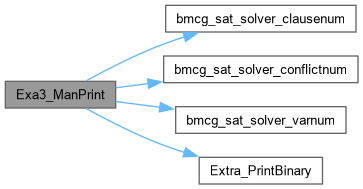

| void | Exa3_ManPrint (Exa3_Man_t *p, int i, int iMint, abctime clk) |

| int | Exa3_ManExactSynthesis (Bmc_EsPar_t *pPars) |

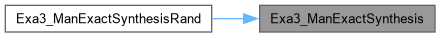

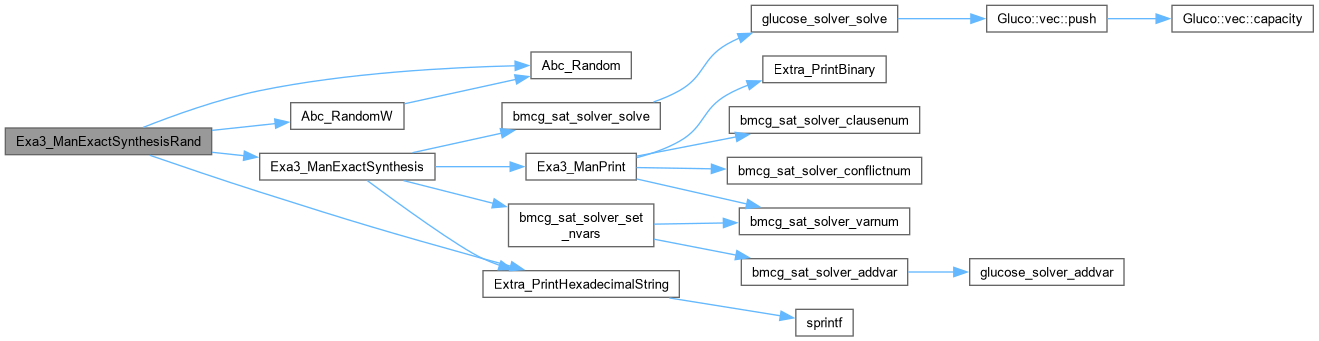

| void | Exa3_ManExactSynthesisRand (Bmc_EsPar_t *pPars) |

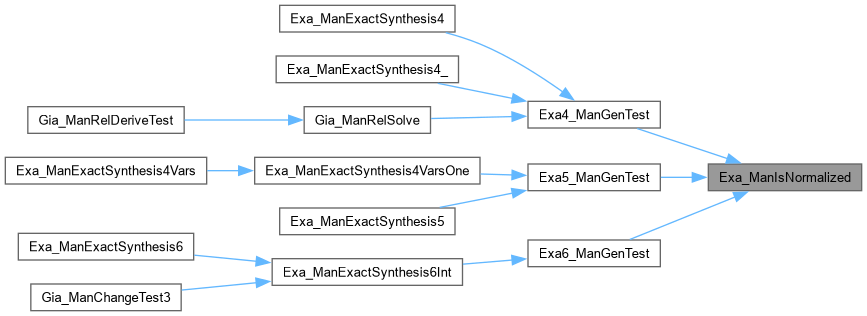

| void | Exa_ManIsNormalized (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut) |

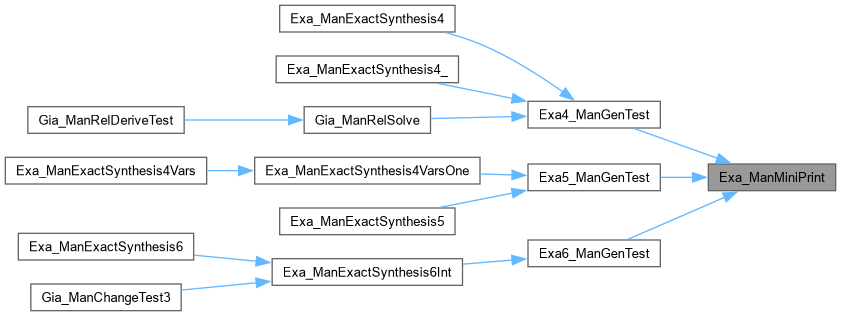

| void | Exa_ManMiniPrint (Mini_Aig_t *p, int nIns) |

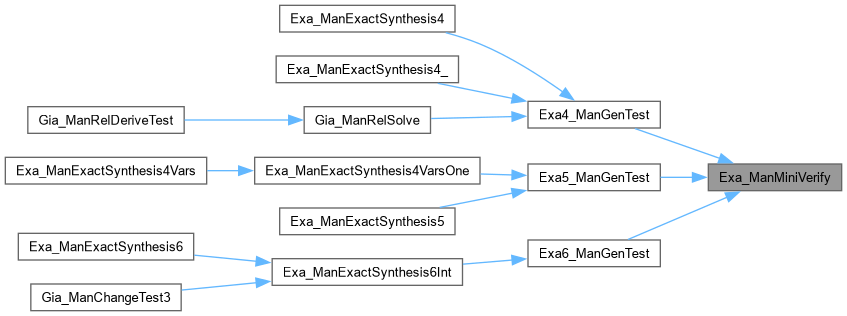

| void | Exa_ManMiniVerify (Mini_Aig_t *p, Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut) |

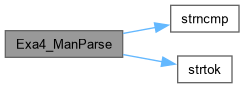

| Vec_Int_t * | Exa4_ManParse (char *pFileName) |

| DECLARATIONS ///. | |

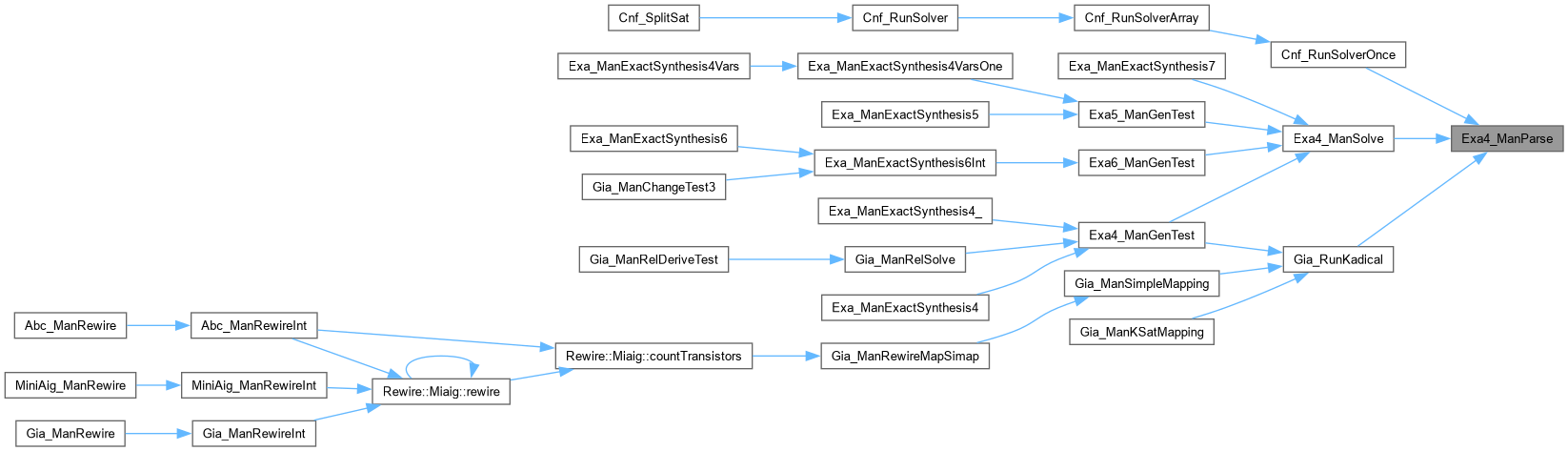

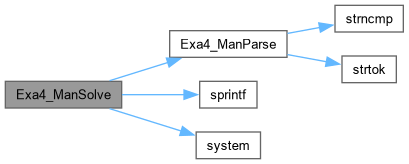

| Vec_Int_t * | Exa4_ManSolve (char *pFileNameIn, char *pFileNameOut, int TimeOut, int fVerbose) |

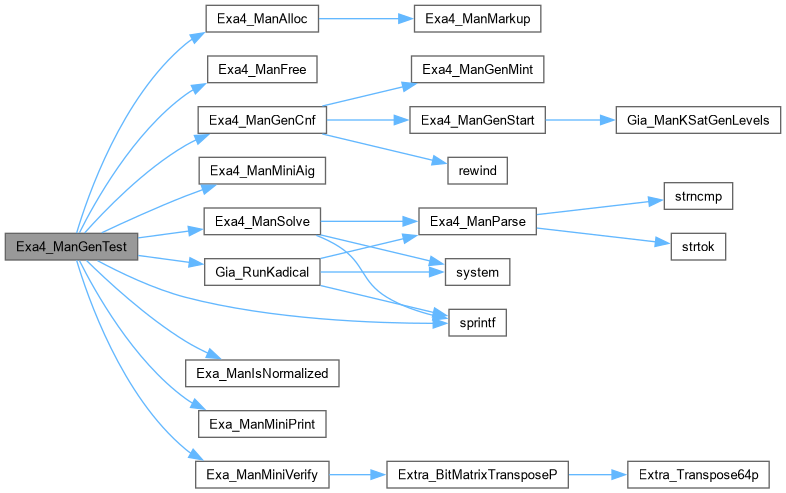

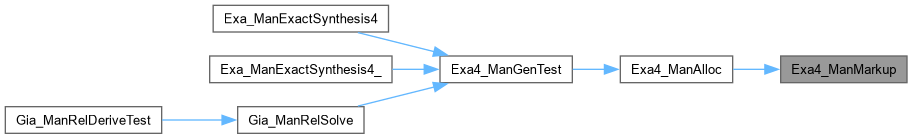

| int | Exa4_ManMarkup (Exa4_Man_t *p) |

| Exa4_Man_t * | Exa4_ManAlloc (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut, int nIns, int nDivs, int nOuts, int nNodes, int fVerbose) |

| void | Exa4_ManFree (Exa4_Man_t *p) |

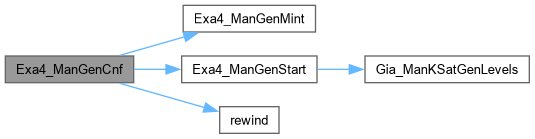

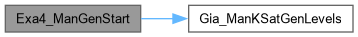

| int | Exa4_ManGenStart (Exa4_Man_t *p, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans, int fCard, char *pGuide) |

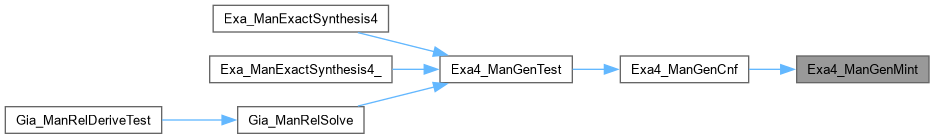

| void | Exa4_ManGenMint (Exa4_Man_t *p, int iMint, int fOnlyAnd, int fFancy) |

| void | Exa4_ManGenCnf (Exa4_Man_t *p, char *pFileName, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans, int fCard, char *pGuide) |

| void | Exa4_ManPrintSolution (Exa4_Man_t *p, Vec_Int_t *vValues, int fFancy) |

| Mini_Aig_t * | Exa4_ManMiniAig (Exa4_Man_t *p, Vec_Int_t *vValues, int fFancy) |

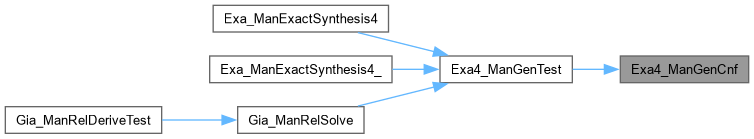

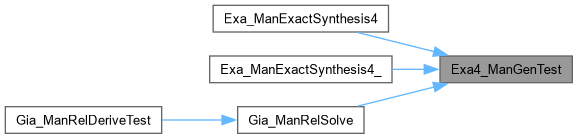

| Mini_Aig_t * | Exa4_ManGenTest (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut, int nIns, int nDivs, int nOuts, int nNodes, int TimeOut, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans, int fVerbose, int fCard, char *pGuide) |

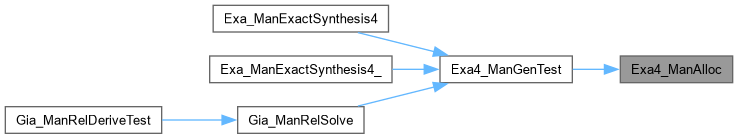

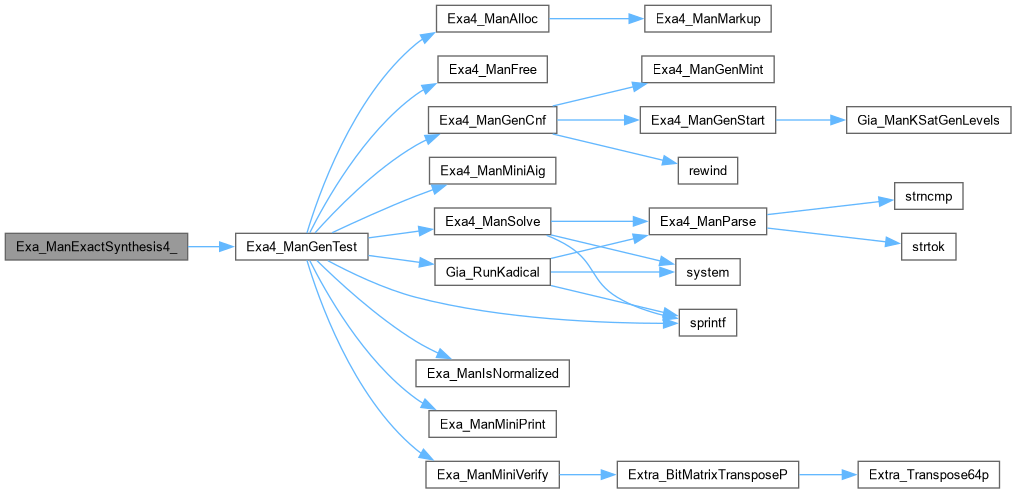

| void | Exa_ManExactSynthesis4_ (Bmc_EsPar_t *pPars) |

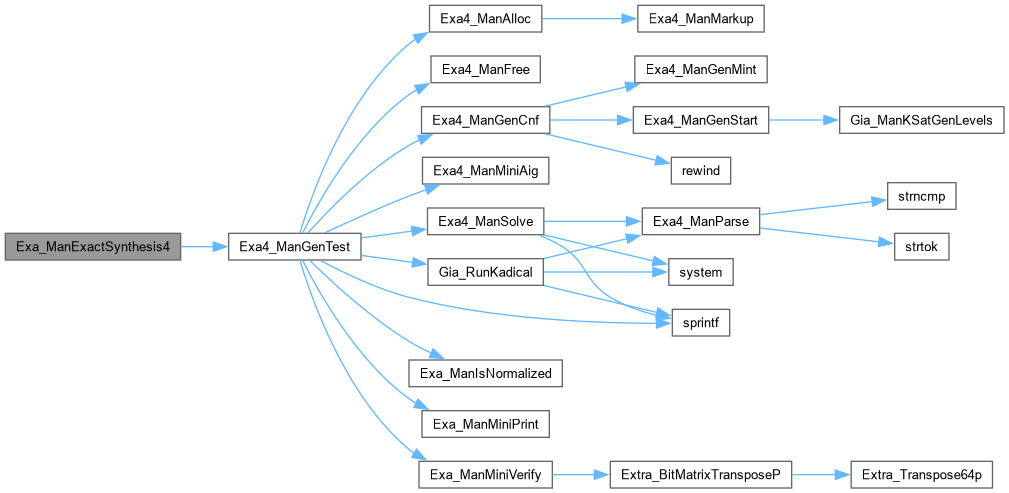

| void | Exa_ManExactSynthesis4 (Bmc_EsPar_t *pPars) |

| int | Exa5_ManMarkup (Exa5_Man_t *p) |

| Exa5_Man_t * | Exa5_ManAlloc (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut, int nIns, int nDivs, int nOuts, int nNodes, int fVerbose) |

| void | Exa5_ManFree (Exa5_Man_t *p) |

| int | Exa5_ManGenStart (Exa5_Man_t *p, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans) |

| void | Exa5_ManGenMint (Exa5_Man_t *p, int iMint, int fOnlyAnd, int fFancy) |

| void | Exa5_ManGenCnf (Exa5_Man_t *p, char *pFileName, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans) |

| void | Exa5_ManPrintSolution (Exa5_Man_t *p, Vec_Int_t *vValues, int fFancy) |

| Mini_Aig_t * | Exa5_ManMiniAig (Exa5_Man_t *p, Vec_Int_t *vValues) |

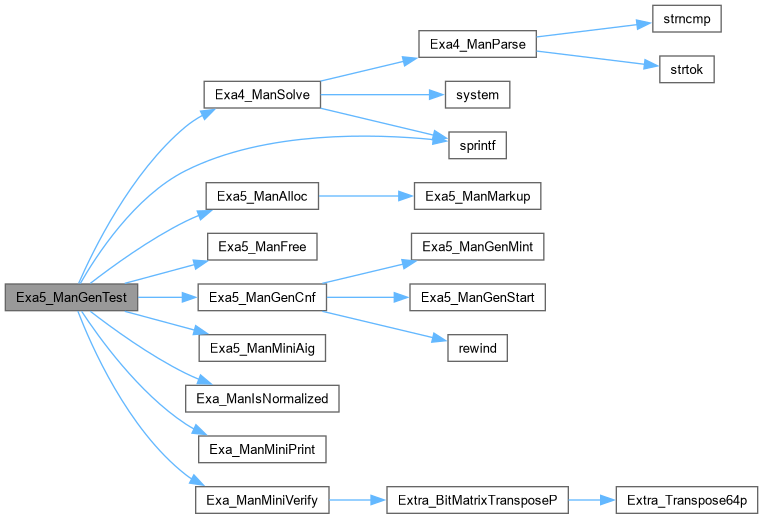

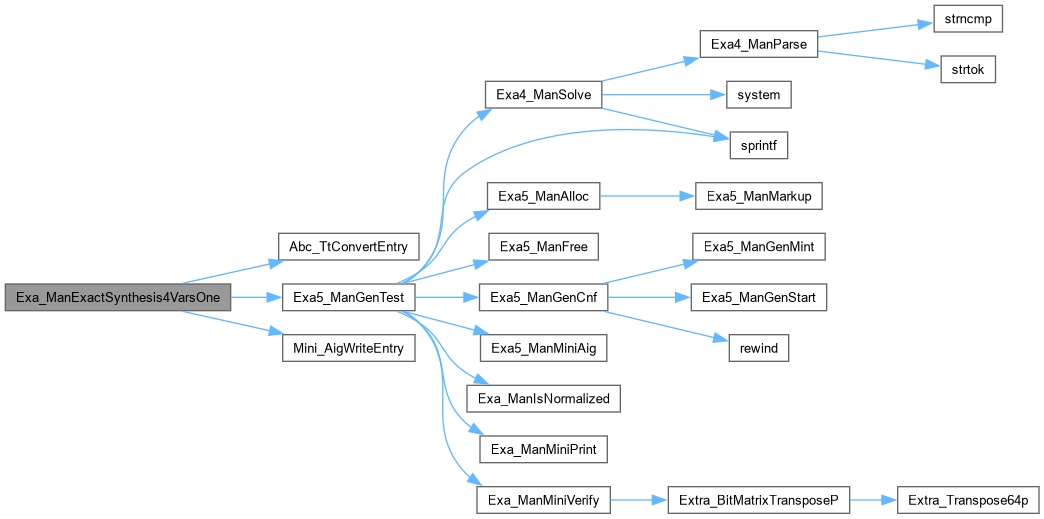

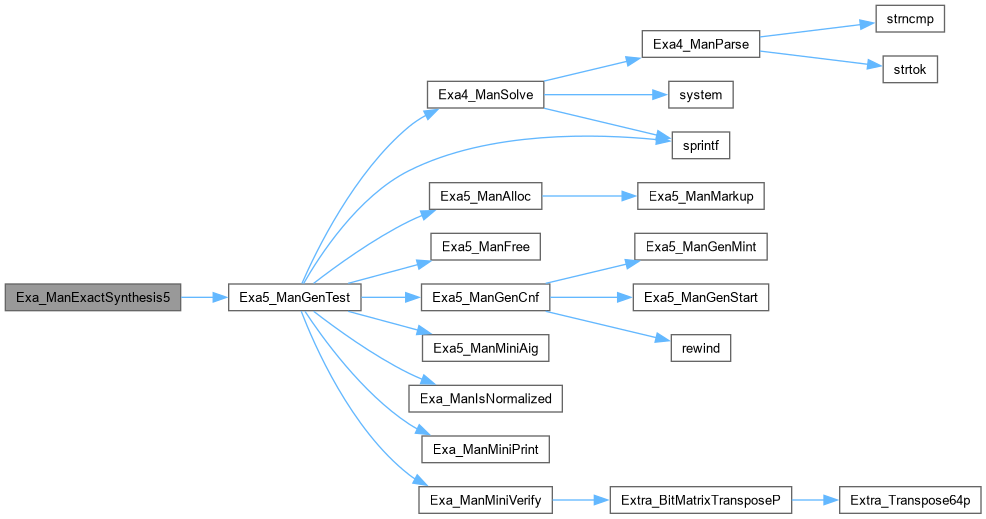

| Mini_Aig_t * | Exa5_ManGenTest (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut, int nIns, int nDivs, int nOuts, int nNodes, int TimeOut, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans, int fVerbose) |

| void | Exa_ManExactSynthesis5 (Bmc_EsPar_t *pPars) |

| void | Mini_AigPrintArray (FILE *pFile, Mini_Aig_t *p) |

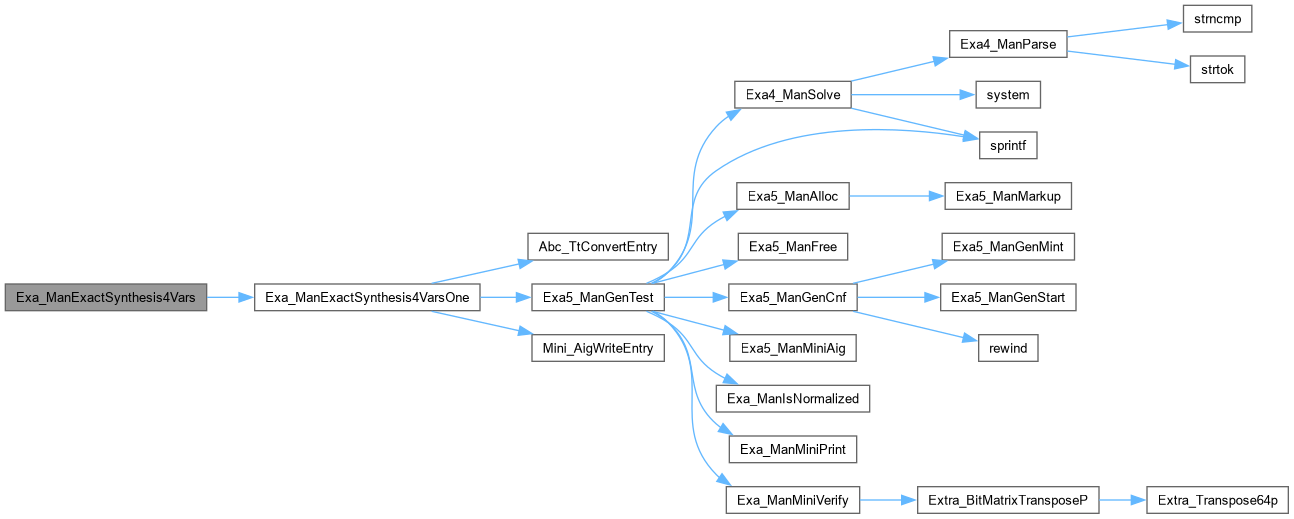

| word | Mini_AigWriteEntry (Mini_Aig_t *p) |

| word | Abc_TtConvertEntry (word Res) |

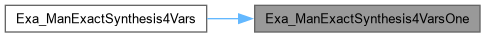

| word | Exa_ManExactSynthesis4VarsOne (int Index, int Truth, int nNodes) |

| void | Exa_ManExactSynthesis4Vars () |

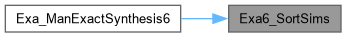

| void | Exa6_SortSims (Vec_Wrd_t *vSimsDiv, Vec_Wrd_t *vSimsOut) |

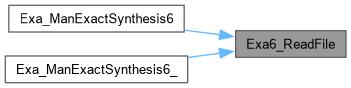

| int | Exa6_ReadFile (char *pFileName, Vec_Wrd_t **pvSimsDiv, Vec_Wrd_t **pvSimsOut, int *pnDivs, int *pnOuts) |

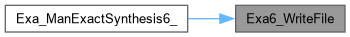

| void | Exa6_WriteFile (char *pFileName, int nVars, word *pTruths, int nTruths) |

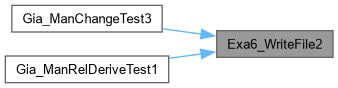

| void | Exa6_WriteFile2 (char *pFileName, int nVars, int nDivs, int nOuts, Vec_Wrd_t *vSimsDiv, Vec_Wrd_t *vSimsOut) |

| void | Exa6_GenCount (word *pTruths, int nVars) |

| void | Exa6_GenProd (word *pTruths, int nVars) |

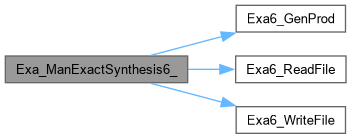

| void | Exa_ManExactSynthesis6_ (Bmc_EsPar_t *pPars, char *pFileName) |

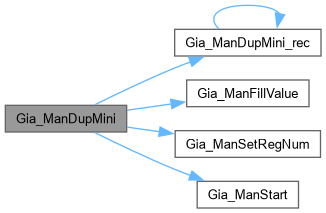

| int | Gia_ManDupMini_rec (Gia_Man_t *pNew, Gia_Man_t *p, Gia_Obj_t *pObj) |

| Gia_Man_t * | Gia_ManDupMini (Gia_Man_t *p, Vec_Int_t *vIns, Vec_Int_t *vDivs, Vec_Int_t *vOuts, Mini_Aig_t *pMini) |

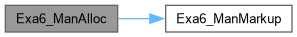

| int | Exa6_ManMarkup (Exa6_Man_t *p) |

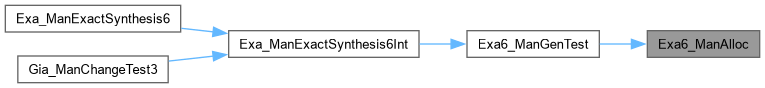

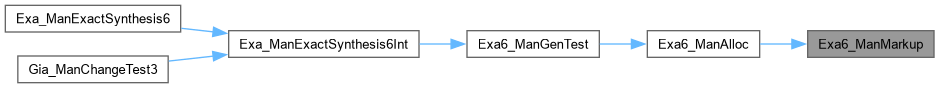

| Exa6_Man_t * | Exa6_ManAlloc (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut, int nIns, int nDivs, int nOuts, int nNodes, int fVerbose) |

| void | Exa6_ManFree (Exa6_Man_t *p) |

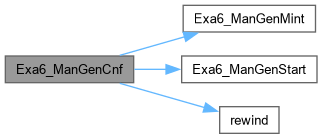

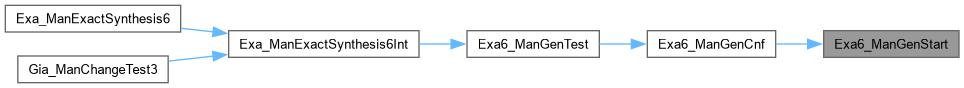

| int | Exa6_ManGenStart (Exa6_Man_t *p, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans) |

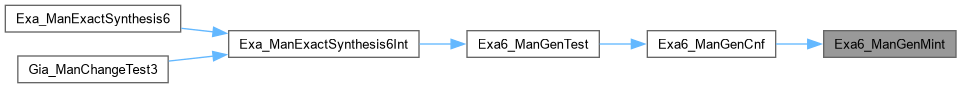

| void | Exa6_ManGenMint (Exa6_Man_t *p, int iMint, int fOnlyAnd, int fFancy) |

| void | Exa6_ManGenCnf (Exa6_Man_t *p, char *pFileName, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans) |

| void | Exa6_ManPrintSolution (Exa6_Man_t *p, Vec_Int_t *vValues, int fFancy) |

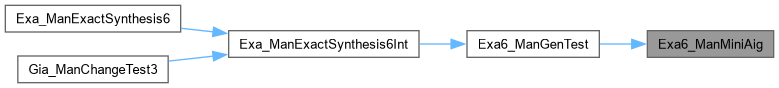

| Mini_Aig_t * | Exa6_ManMiniAig (Exa6_Man_t *p, Vec_Int_t *vValues, int fFancy) |

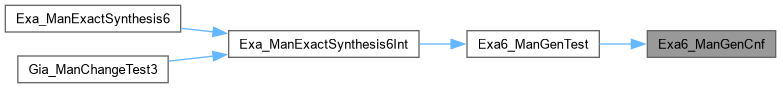

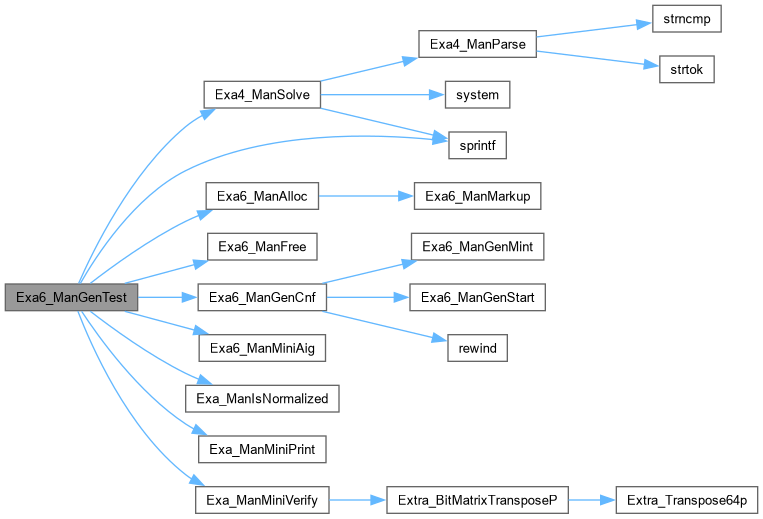

| Mini_Aig_t * | Exa6_ManGenTest (Vec_Wrd_t *vSimsIn, Vec_Wrd_t *vSimsOut, int nIns, int nDivs, int nOuts, int nNodes, int TimeOut, int fOnlyAnd, int fFancy, int fOrderNodes, int fUniqFans, int fVerbose) |

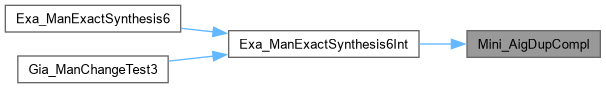

| Mini_Aig_t * | Mini_AigDupCompl (Mini_Aig_t *p, int ComplIns, int ComplOuts) |

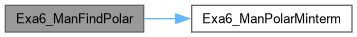

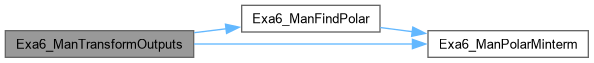

| word | Exa6_ManPolarMinterm (word Mint, int nOuts, int Polar) |

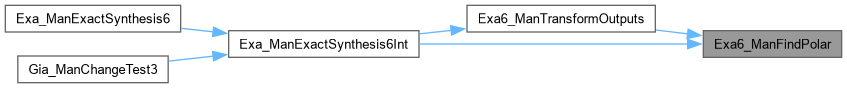

| int | Exa6_ManFindPolar (word First, int nOuts) |

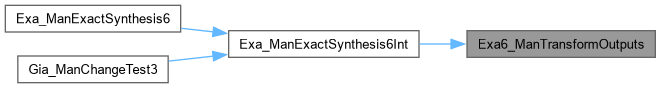

| Vec_Wrd_t * | Exa6_ManTransformOutputs (Vec_Wrd_t *vOuts, int nOuts) |

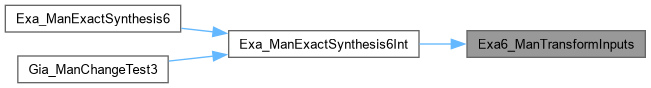

| Vec_Wrd_t * | Exa6_ManTransformInputs (Vec_Wrd_t *vIns) |

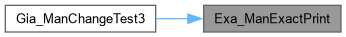

| void | Exa_ManExactPrint (Vec_Wrd_t *vSimsDiv, Vec_Wrd_t *vSimsOut, int nDivs, int nOuts) |

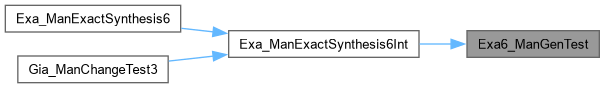

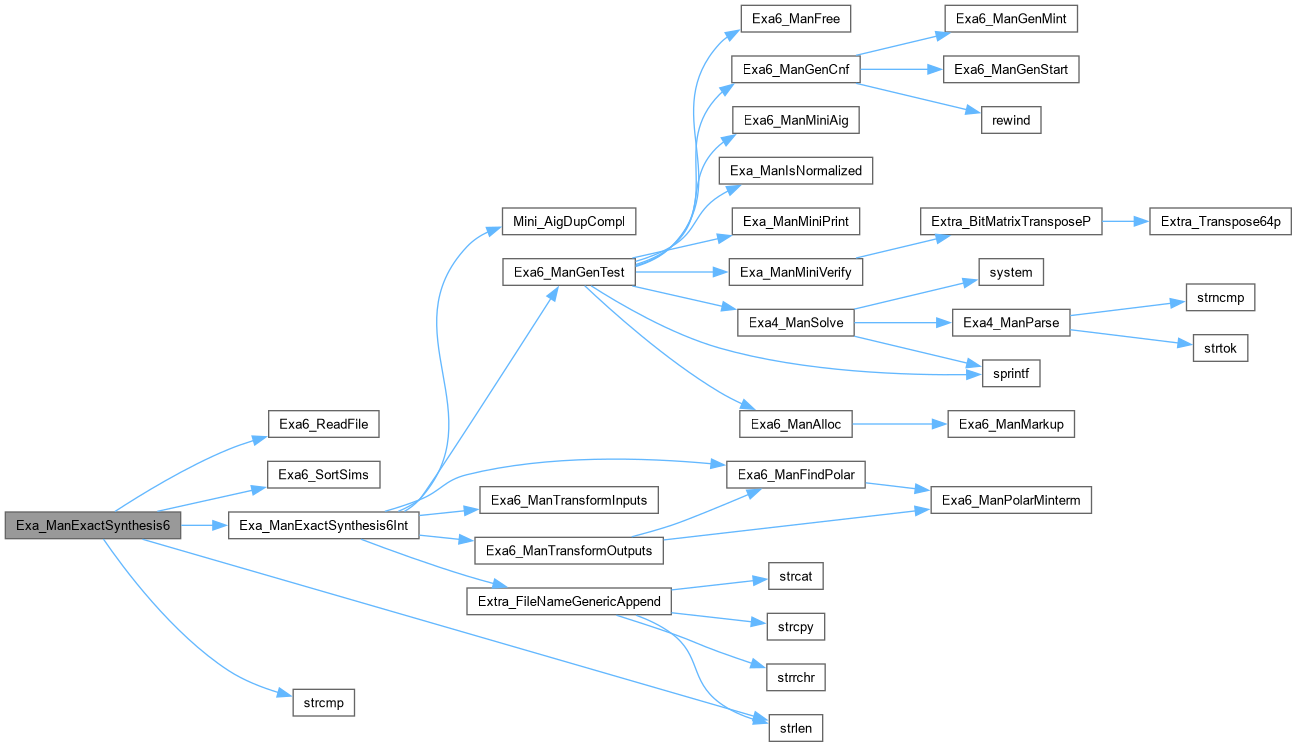

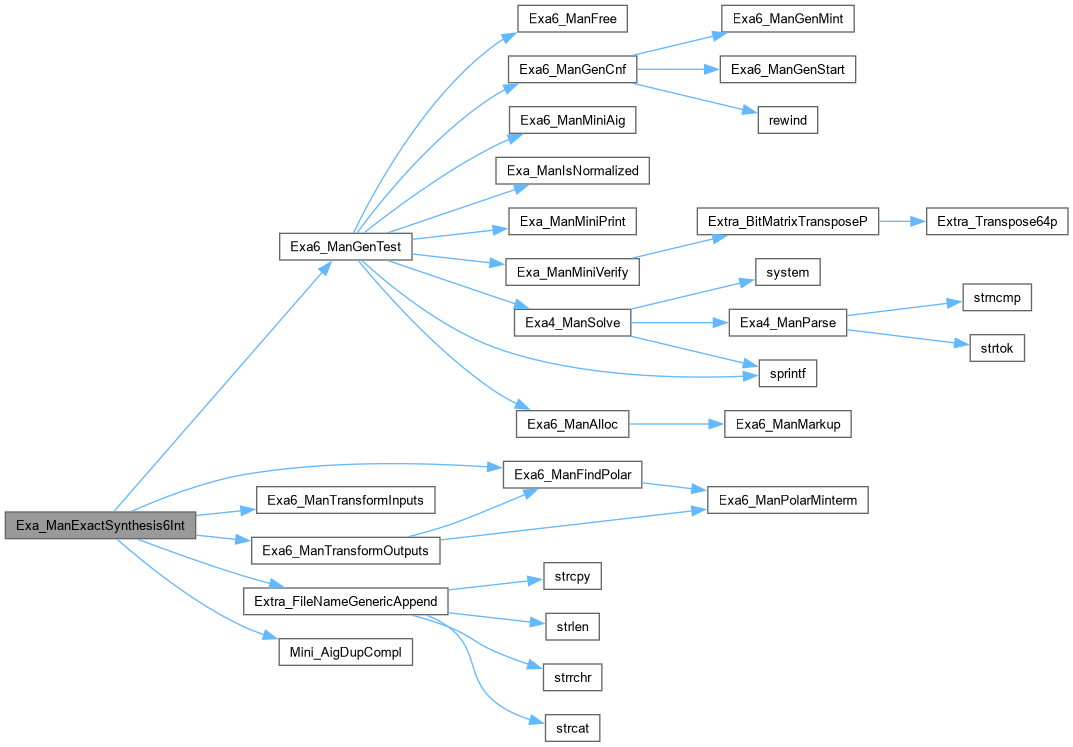

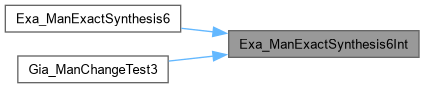

| Mini_Aig_t * | Exa_ManExactSynthesis6Int (Vec_Wrd_t *vSimsDiv, Vec_Wrd_t *vSimsOut, int nVars, int nDivs, int nOuts, int nNodes, int fOnlyAnd, int fVerbose, char *pFileName) |

| void | Exa_ManExactSynthesis6 (Bmc_EsPar_t *pPars, char *pFileName) |

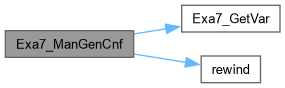

| int | Exa7_GetVar (int n, int i, int j, int m) |

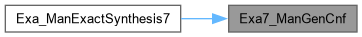

| int | Exa7_ManGenCnf (char *pFileName, word *pTruth, int nVars, int nNodes, int GateSize) |

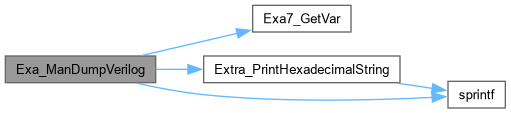

| void | Exa_ManDumpVerilog (Vec_Int_t *vValues, int nVars, int nNodes, int GateSize, word *pTruth) |

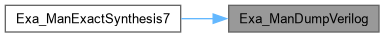

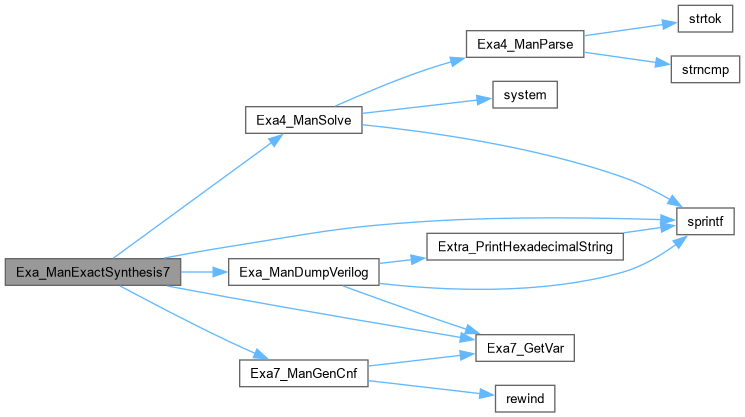

| void | Exa_ManExactSynthesis7 (Bmc_EsPar_t *pPars, int GateSize) |

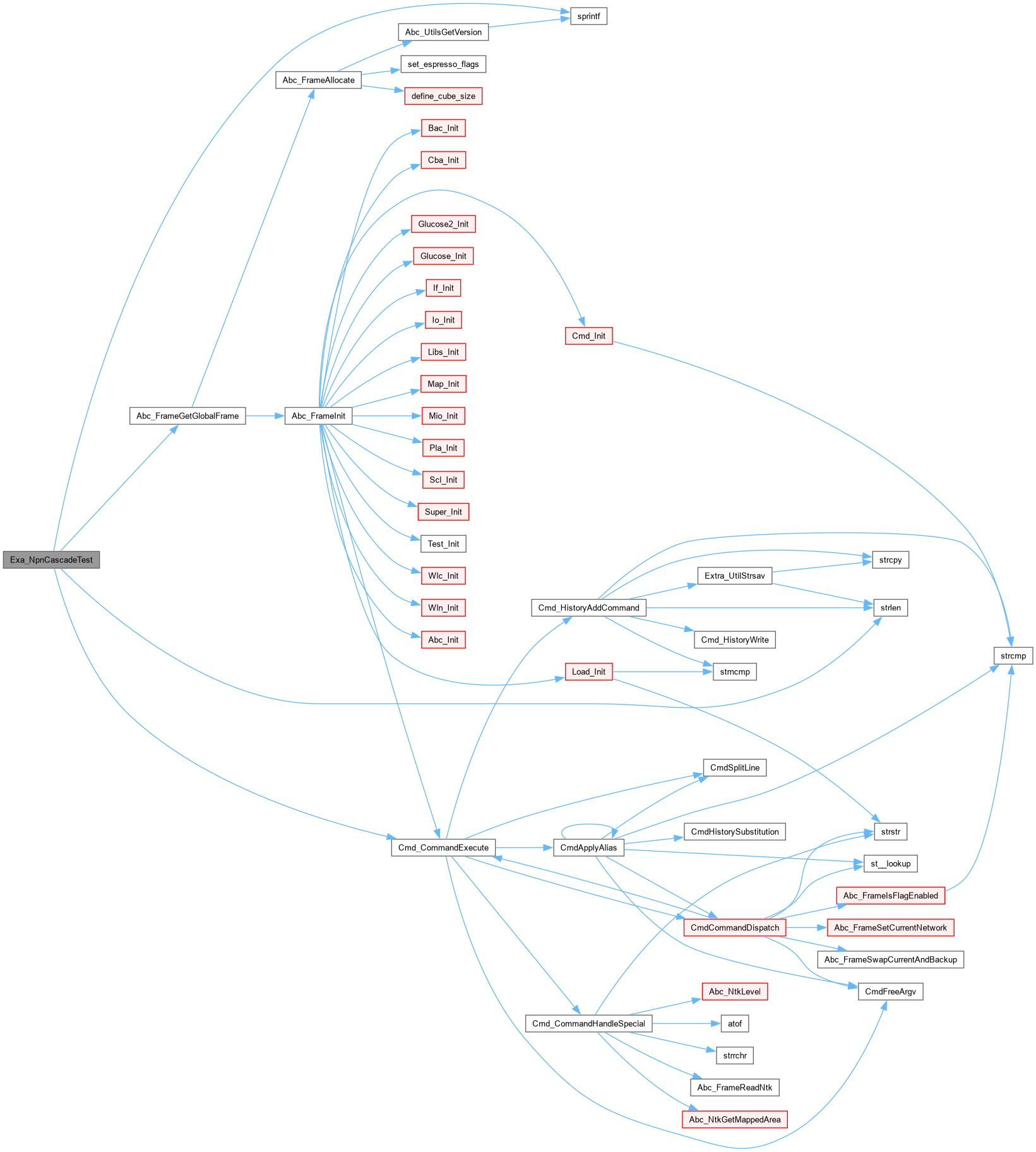

| void | Exa_NpnCascadeTest () |

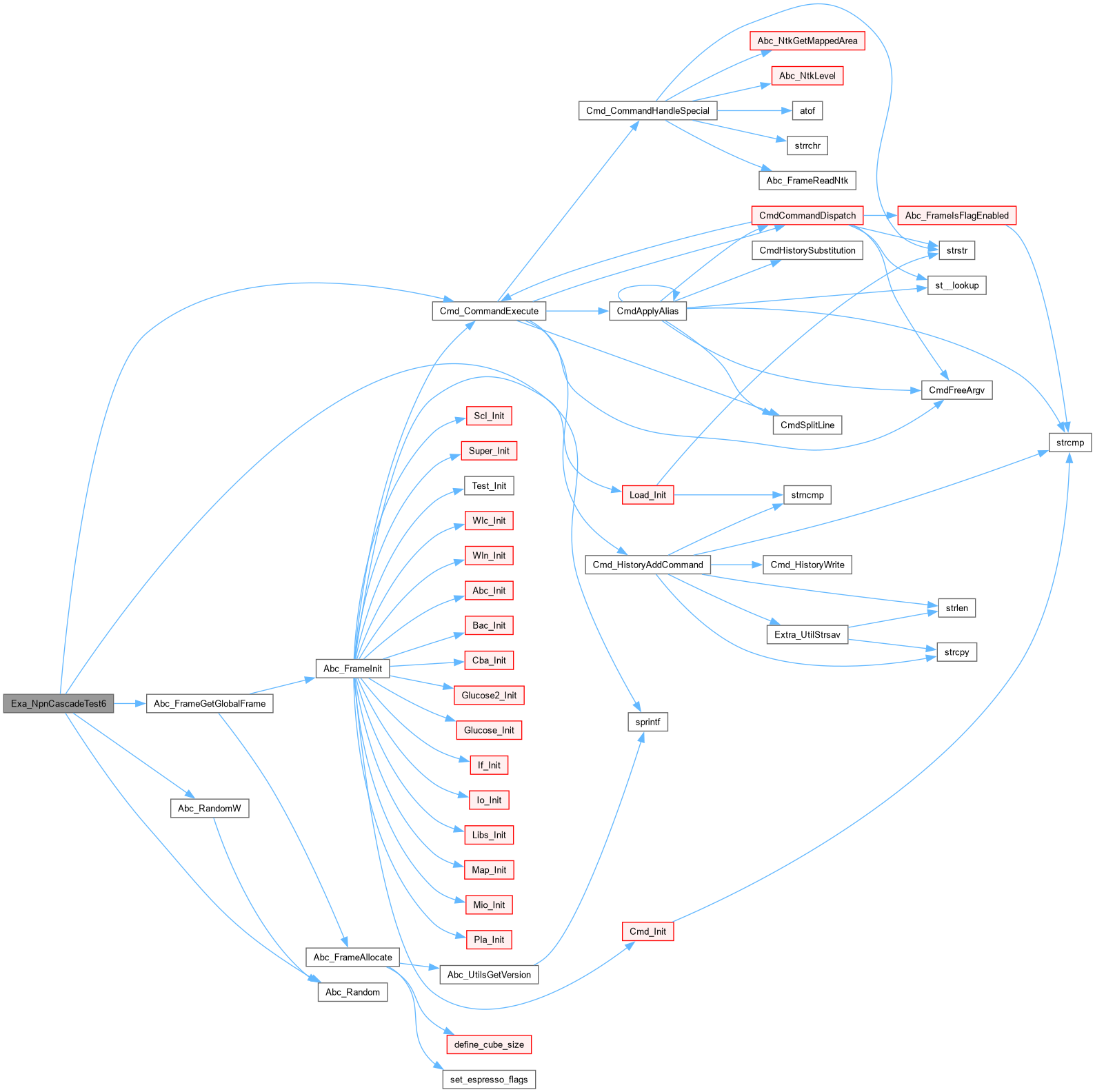

| void | Exa_NpnCascadeTest6 () |

| #define MAJ_NOBJS 64 |

DECLARATIONS ///.

CFile****************************************************************

FileName [bmcMaj.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [SAT-based bounded model checking.]

Synopsis [Exact synthesis with majority gates.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - October 1, 2017.]

Revision [

]

| typedef struct Exa3_Man_t_ Exa3_Man_t |

| typedef struct Exa4_Man_t_ Exa4_Man_t |

| typedef struct Exa5_Man_t_ Exa5_Man_t |

| typedef struct Exa6_Man_t_ Exa6_Man_t |

| typedef struct Exa_Man_t_ Exa_Man_t |

| typedef struct Maj_Man_t_ Maj_Man_t |

Definition at line 3027 of file bmcMaj.c.

| Vec_Wec_t * Exa3_ChooseInputVars | ( | int | nVars, |

| int | nLuts, | ||

| int | nLutSize ) |

Definition at line 1077 of file bmcMaj.c.

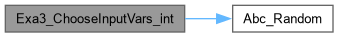

| Vec_Wec_t * Exa3_ChooseInputVars_int | ( | int | nVars, |

| int | nLuts, | ||

| int | nLutSize ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 1055 of file bmcMaj.c.

Definition at line 1068 of file bmcMaj.c.

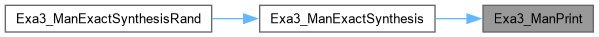

| int Exa3_ManExactSynthesis | ( | Bmc_EsPar_t * | pPars | ) |

Definition at line 1598 of file bmcMaj.c.

| void Exa3_ManExactSynthesisRand | ( | Bmc_EsPar_t * | pPars | ) |

Definition at line 1655 of file bmcMaj.c.

| void Exa3_ManPrint | ( | Exa3_Man_t * | p, |

| int | i, | ||

| int | iMint, | ||

| abctime | clk ) |

Definition at line 1589 of file bmcMaj.c.

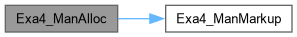

| Exa4_Man_t * Exa4_ManAlloc | ( | Vec_Wrd_t * | vSimsIn, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nIns, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | fVerbose ) |

Definition at line 1976 of file bmcMaj.c.

| void Exa4_ManFree | ( | Exa4_Man_t * | p | ) |

| void Exa4_ManGenCnf | ( | Exa4_Man_t * | p, |

| char * | pFileName, | ||

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans, | ||

| int | fCard, | ||

| char * | pGuide ) |

Definition at line 2221 of file bmcMaj.c.

| void Exa4_ManGenMint | ( | Exa4_Man_t * | p, |

| int | iMint, | ||

| int | fOnlyAnd, | ||

| int | fFancy ) |

Definition at line 2142 of file bmcMaj.c.

| int Exa4_ManGenStart | ( | Exa4_Man_t * | p, |

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans, | ||

| int | fCard, | ||

| char * | pGuide ) |

Definition at line 2041 of file bmcMaj.c.

| Mini_Aig_t * Exa4_ManGenTest | ( | Vec_Wrd_t * | vSimsIn, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nIns, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | TimeOut, | ||

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans, | ||

| int | fVerbose, | ||

| int | fCard, | ||

| char * | pGuide ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 2395 of file bmcMaj.c.

| int Exa4_ManMarkup | ( | Exa4_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 1917 of file bmcMaj.c.

| Mini_Aig_t * Exa4_ManMiniAig | ( | Exa4_Man_t * | p, |

| Vec_Int_t * | vValues, | ||

| int | fFancy ) |

Definition at line 2320 of file bmcMaj.c.

| Vec_Int_t * Exa4_ManParse | ( | char * | pFileName | ) |

DECLARATIONS ///.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 1812 of file bmcMaj.c.

| void Exa4_ManPrintSolution | ( | Exa4_Man_t * | p, |

| Vec_Int_t * | vValues, | ||

| int | fFancy ) |

Definition at line 2271 of file bmcMaj.c.

| Vec_Int_t * Exa4_ManSolve | ( | char * | pFileNameIn, |

| char * | pFileNameOut, | ||

| int | TimeOut, | ||

| int | fVerbose ) |

Definition at line 1850 of file bmcMaj.c.

| Exa5_Man_t * Exa5_ManAlloc | ( | Vec_Wrd_t * | vSimsIn, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nIns, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | fVerbose ) |

Definition at line 2568 of file bmcMaj.c.

| void Exa5_ManFree | ( | Exa5_Man_t * | p | ) |

| void Exa5_ManGenCnf | ( | Exa5_Man_t * | p, |

| char * | pFileName, | ||

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans ) |

Definition at line 2767 of file bmcMaj.c.

| void Exa5_ManGenMint | ( | Exa5_Man_t * | p, |

| int | iMint, | ||

| int | fOnlyAnd, | ||

| int | fFancy ) |

Definition at line 2729 of file bmcMaj.c.

| int Exa5_ManGenStart | ( | Exa5_Man_t * | p, |

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans ) |

Definition at line 2654 of file bmcMaj.c.

| Mini_Aig_t * Exa5_ManGenTest | ( | Vec_Wrd_t * | vSimsIn, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nIns, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | TimeOut, | ||

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 2926 of file bmcMaj.c.

| int Exa5_ManMarkup | ( | Exa5_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 2505 of file bmcMaj.c.

| Mini_Aig_t * Exa5_ManMiniAig | ( | Exa5_Man_t * | p, |

| Vec_Int_t * | vValues ) |

Definition at line 2860 of file bmcMaj.c.

| void Exa5_ManPrintSolution | ( | Exa5_Man_t * | p, |

| Vec_Int_t * | vValues, | ||

| int | fFancy ) |

Definition at line 2815 of file bmcMaj.c.

| void Exa6_GenCount | ( | word * | pTruths, |

| int | nVars ) |

Definition at line 3279 of file bmcMaj.c.

| void Exa6_GenProd | ( | word * | pTruths, |

| int | nVars ) |

Definition at line 3293 of file bmcMaj.c.

| Exa6_Man_t * Exa6_ManAlloc | ( | Vec_Wrd_t * | vSimsIn, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nIns, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | fVerbose ) |

Definition at line 3510 of file bmcMaj.c.

| int Exa6_ManFindPolar | ( | word | First, |

| int | nOuts ) |

Definition at line 3911 of file bmcMaj.c.

| void Exa6_ManFree | ( | Exa6_Man_t * | p | ) |

| void Exa6_ManGenCnf | ( | Exa6_Man_t * | p, |

| char * | pFileName, | ||

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans ) |

Definition at line 3724 of file bmcMaj.c.

| void Exa6_ManGenMint | ( | Exa6_Man_t * | p, |

| int | iMint, | ||

| int | fOnlyAnd, | ||

| int | fFancy ) |

Definition at line 3653 of file bmcMaj.c.

| int Exa6_ManGenStart | ( | Exa6_Man_t * | p, |

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans ) |

Definition at line 3577 of file bmcMaj.c.

| Mini_Aig_t * Exa6_ManGenTest | ( | Vec_Wrd_t * | vSimsIn, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nIns, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | TimeOut, | ||

| int | fOnlyAnd, | ||

| int | fFancy, | ||

| int | fOrderNodes, | ||

| int | fUniqFans, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3849 of file bmcMaj.c.

| int Exa6_ManMarkup | ( | Exa6_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3449 of file bmcMaj.c.

| Mini_Aig_t * Exa6_ManMiniAig | ( | Exa6_Man_t * | p, |

| Vec_Int_t * | vValues, | ||

| int | fFancy ) |

Definition at line 3801 of file bmcMaj.c.

| void Exa6_ManPrintSolution | ( | Exa6_Man_t * | p, |

| Vec_Int_t * | vValues, | ||

| int | fFancy ) |

Definition at line 3772 of file bmcMaj.c.

Definition at line 3927 of file bmcMaj.c.

Definition at line 3919 of file bmcMaj.c.

| int Exa6_ReadFile | ( | char * | pFileName, |

| Vec_Wrd_t ** | pvSimsDiv, | ||

| Vec_Wrd_t ** | pvSimsOut, | ||

| int * | pnDivs, | ||

| int * | pnOuts ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3164 of file bmcMaj.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3130 of file bmcMaj.c.

| void Exa6_WriteFile | ( | char * | pFileName, |

| int | nVars, | ||

| word * | pTruths, | ||

| int | nTruths ) |

Definition at line 3242 of file bmcMaj.c.

| void Exa6_WriteFile2 | ( | char * | pFileName, |

| int | nVars, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| Vec_Wrd_t * | vSimsDiv, | ||

| Vec_Wrd_t * | vSimsOut ) |

Definition at line 3263 of file bmcMaj.c.

| int Exa7_GetVar | ( | int | n, |

| int | i, | ||

| int | j, | ||

| int | m ) |

| int Exa7_ManGenCnf | ( | char * | pFileName, |

| word * | pTruth, | ||

| int | nVars, | ||

| int | nNodes, | ||

| int | GateSize ) |

Definition at line 4064 of file bmcMaj.c.

| int Exa_ManAddCnf | ( | Exa_Man_t * | p, |

| int | iMint ) |

Definition at line 885 of file bmcMaj.c.

| int Exa_ManAddCnfAdd | ( | Exa_Man_t * | p, |

| int * | pnAdded ) |

Definition at line 710 of file bmcMaj.c.

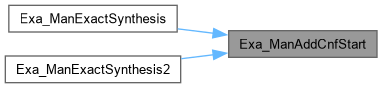

| int Exa_ManAddCnfStart | ( | Exa_Man_t * | p, |

| int | fOnlyAnd ) |

Definition at line 764 of file bmcMaj.c.

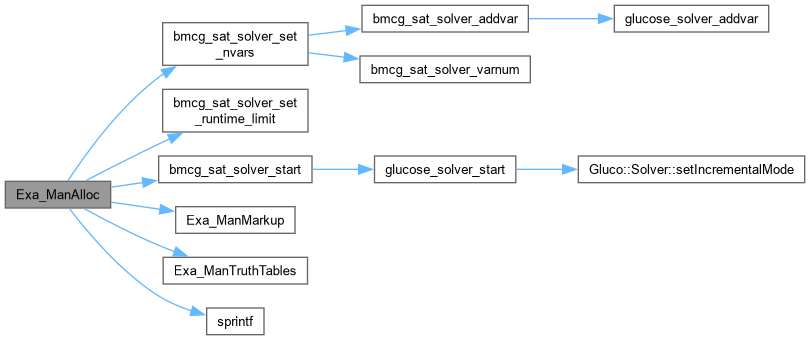

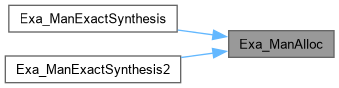

| Exa_Man_t * Exa_ManAlloc | ( | Bmc_EsPar_t * | pPars, |

| word * | pTruth ) |

Definition at line 502 of file bmcMaj.c.

| void Exa_ManDumpBlif | ( | Exa_Man_t * | p, |

| int | fCompl ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 606 of file bmcMaj.c.

Definition at line 4119 of file bmcMaj.c.

Definition at line 3935 of file bmcMaj.c.

| void Exa_ManExactSynthesis | ( | Bmc_EsPar_t * | pPars | ) |

Definition at line 940 of file bmcMaj.c.

| void Exa_ManExactSynthesis4 | ( | Bmc_EsPar_t * | pPars | ) |

Definition at line 2449 of file bmcMaj.c.

| void Exa_ManExactSynthesis4_ | ( | Bmc_EsPar_t * | pPars | ) |

Definition at line 2426 of file bmcMaj.c.

| void Exa_ManExactSynthesis4Vars | ( | ) |

Definition at line 3099 of file bmcMaj.c.

| word Exa_ManExactSynthesis4VarsOne | ( | int | Index, |

| int | Truth, | ||

| int | nNodes ) |

Definition at line 3060 of file bmcMaj.c.

| void Exa_ManExactSynthesis5 | ( | Bmc_EsPar_t * | pPars | ) |

Definition at line 2953 of file bmcMaj.c.

| void Exa_ManExactSynthesis6 | ( | Bmc_EsPar_t * | pPars, |

| char * | pFileName ) |

Definition at line 3977 of file bmcMaj.c.

| void Exa_ManExactSynthesis6_ | ( | Bmc_EsPar_t * | pPars, |

| char * | pFileName ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3321 of file bmcMaj.c.

| Mini_Aig_t * Exa_ManExactSynthesis6Int | ( | Vec_Wrd_t * | vSimsDiv, |

| Vec_Wrd_t * | vSimsOut, | ||

| int | nVars, | ||

| int | nDivs, | ||

| int | nOuts, | ||

| int | nNodes, | ||

| int | fOnlyAnd, | ||

| int | fVerbose, | ||

| char * | pFileName ) |

Definition at line 3945 of file bmcMaj.c.

| void Exa_ManExactSynthesis7 | ( | Bmc_EsPar_t * | pPars, |

| int | GateSize ) |

Definition at line 4148 of file bmcMaj.c.

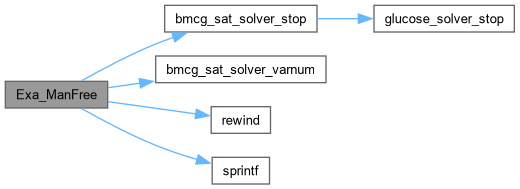

| void Exa_ManFree | ( | Exa_Man_t * | p | ) |

Definition at line 527 of file bmcMaj.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 1702 of file bmcMaj.c.

| int Exa_ManMarkup | ( | Exa_Man_t * | p | ) |

Definition at line 462 of file bmcMaj.c.

| void Exa_ManMiniPrint | ( | Mini_Aig_t * | p, |

| int | nIns ) |

Definition at line 1726 of file bmcMaj.c.

| void Exa_ManMiniVerify | ( | Mini_Aig_t * | p, |

| Vec_Wrd_t * | vSimsIn, | ||

| Vec_Wrd_t * | vSimsOut ) |

Definition at line 1758 of file bmcMaj.c.

| void Exa_ManPrintSolution | ( | Exa_Man_t * | p, |

| int | fCompl ) |

Definition at line 659 of file bmcMaj.c.

| int Exa_ManSolverSolve | ( | Exa_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 454 of file bmcMaj.c.

| void Exa_NpnCascadeTest | ( | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 4191 of file bmcMaj.c.

| void Exa_NpnCascadeTest6 | ( | ) |

Definition at line 4219 of file bmcMaj.c.

| Gia_Man_t * Gia_ManDupMini | ( | Gia_Man_t * | p, |

| Vec_Int_t * | vIns, | ||

| Vec_Int_t * | vDivs, | ||

| Vec_Int_t * | vOuts, | ||

| Mini_Aig_t * | pMini ) |

Definition at line 3368 of file bmcMaj.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3359 of file bmcMaj.c.

| int Maj_ManAddCnf | ( | Maj_Man_t * | p, |

| int | iMint ) |

Definition at line 325 of file bmcMaj.c.

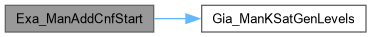

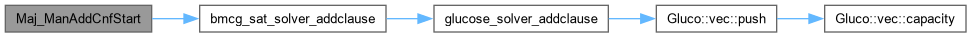

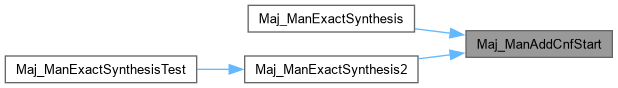

| int Maj_ManAddCnfStart | ( | Maj_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 278 of file bmcMaj.c.

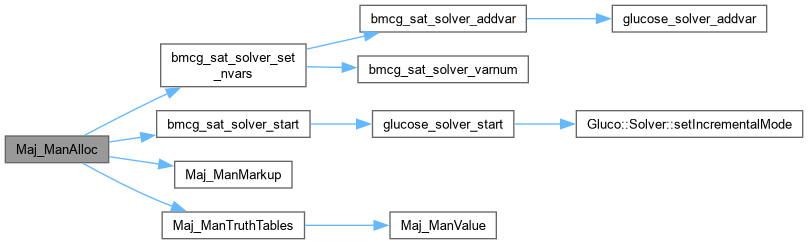

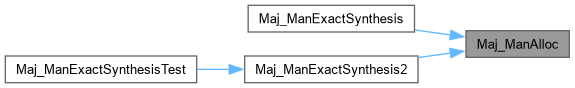

| Maj_Man_t * Maj_ManAlloc | ( | int | nVars, |

| int | nNodes, | ||

| int | fUseConst, | ||

| int | fUseLine ) |

Definition at line 147 of file bmcMaj.c.

| int Maj_ManExactSynthesis | ( | int | nVars, |

| int | nNodes, | ||

| int | fUseConst, | ||

| int | fUseLine, | ||

| int | fVerbose ) |

Definition at line 377 of file bmcMaj.c.

| void Maj_ManFree | ( | Maj_Man_t * | p | ) |

| int Maj_ManMarkup | ( | Maj_Man_t * | p | ) |

Definition at line 100 of file bmcMaj.c.

| void Maj_ManPrintSolution | ( | Maj_Man_t * | p | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 244 of file bmcMaj.c.

| int Maj_ManValue | ( | int | iMint, |

| int | nVars ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 80 of file bmcMaj.c.

| Mini_Aig_t * Mini_AigDupCompl | ( | Mini_Aig_t * | p, |

| int | ComplIns, | ||

| int | ComplOuts ) |

Definition at line 3875 of file bmcMaj.c.

| void Mini_AigPrintArray | ( | FILE * | pFile, |

| Mini_Aig_t * | p ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 2988 of file bmcMaj.c.

| word Mini_AigWriteEntry | ( | Mini_Aig_t * | p | ) |

Definition at line 3000 of file bmcMaj.c.