Go to the source code of this file.

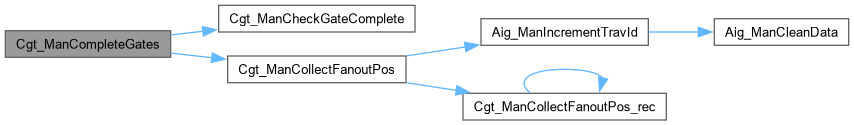

| int Cgt_ManCheckGateComplete | ( | Aig_Man_t * | pAig, |

| Vec_Vec_t * | vGatesAll, | ||

| Aig_Obj_t * | pGate, | ||

| Vec_Ptr_t * | vFanout ) |

Function*************************************************************

Synopsis [Checks if all PO fanouts can be gated by this node.]

Description []

SideEffects []

SeeAlso []

Definition at line 97 of file cgtDecide.c.

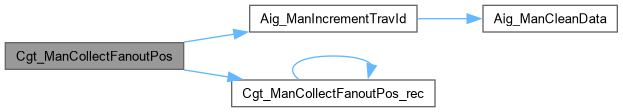

Function*************************************************************

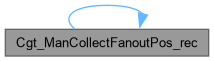

Synopsis [Collects POs in the transitive fanout.]

Description []

SideEffects []

SeeAlso []

Definition at line 79 of file cgtDecide.c.

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Collects POs in the transitive fanout.]

Description []

SideEffects []

SeeAlso []

Definition at line 52 of file cgtDecide.c.

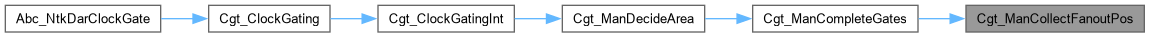

| Vec_Ptr_t * Cgt_ManCompleteGates | ( | Aig_Man_t * | pAig, |

| Vec_Vec_t * | vGatesAll, | ||

| int | nOdcMax, | ||

| int | fVerbose ) |

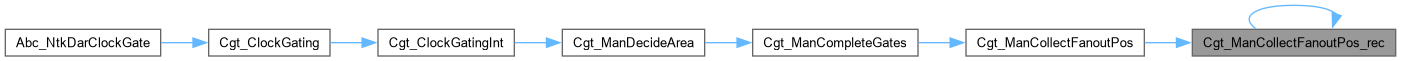

Function*************************************************************

Synopsis [Computes the set of complete clock gates.]

Description []

SideEffects []

SeeAlso []

Definition at line 124 of file cgtDecide.c.

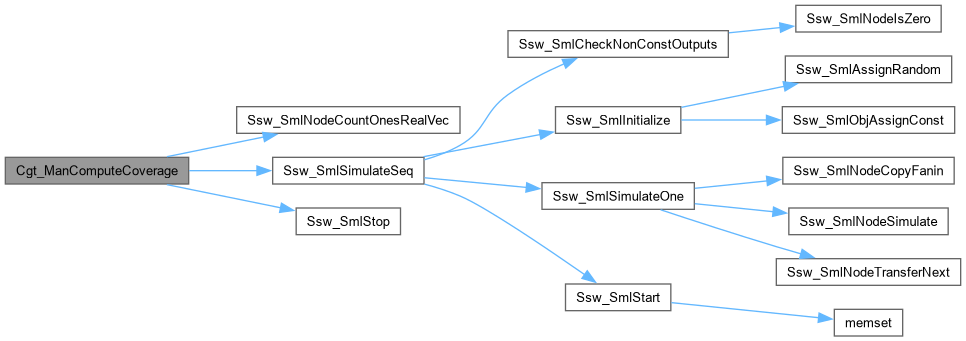

Function*************************************************************

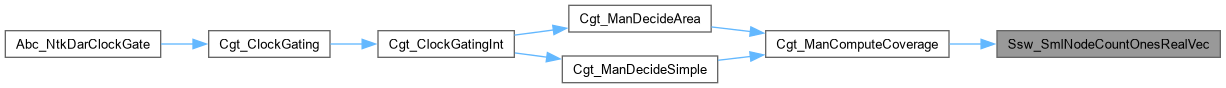

Synopsis [Calculates coverage.]

Description []

SideEffects []

SeeAlso []

Definition at line 158 of file cgtDecide.c.

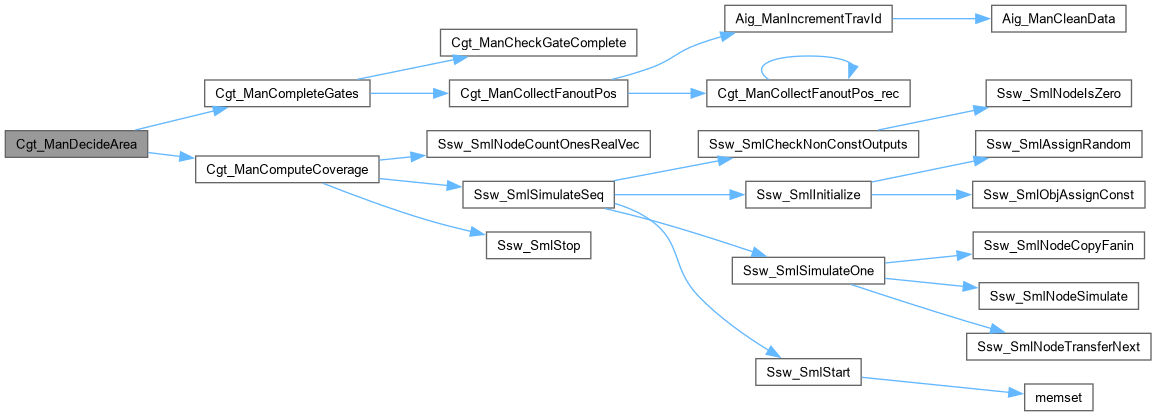

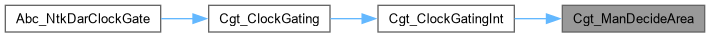

| Vec_Vec_t * Cgt_ManDecideArea | ( | Aig_Man_t * | pAig, |

| Vec_Vec_t * | vGatesAll, | ||

| int | nOdcMax, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Computes the set of complete clock gates.]

Description []

SideEffects []

SeeAlso []

Definition at line 255 of file cgtDecide.c.

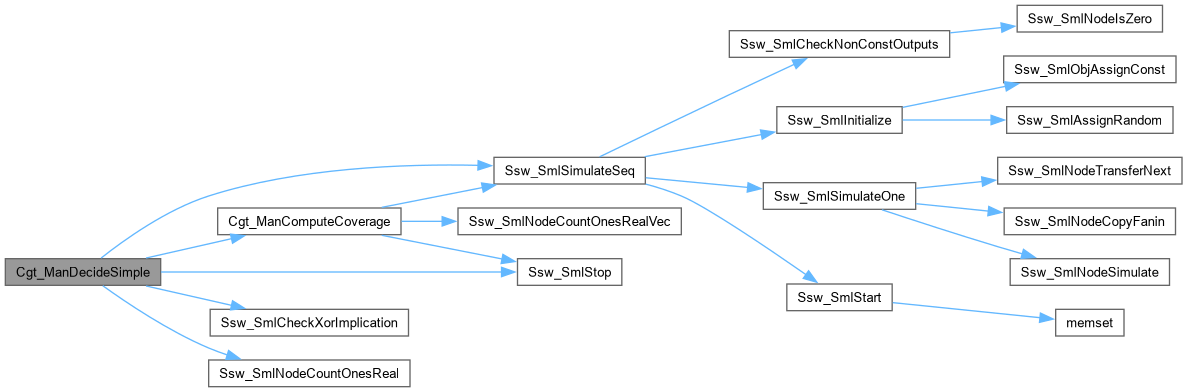

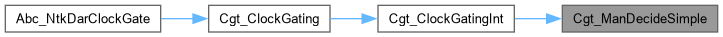

| Vec_Vec_t * Cgt_ManDecideSimple | ( | Aig_Man_t * | pAig, |

| Vec_Vec_t * | vGatesAll, | ||

| int | nOdcMax, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Chooses what clock-gate to use for this register.]

Description [Currently uses the naive approach: For each register, choose the clock gate, which covers most of the transitions.]

SideEffects []

SeeAlso []

Definition at line 184 of file cgtDecide.c.

|

extern |

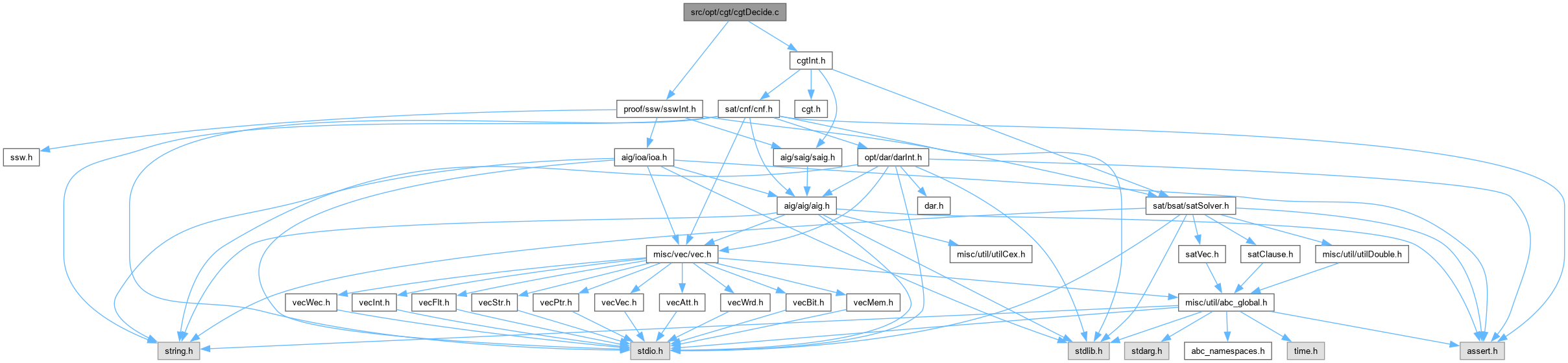

DECLARATIONS ///.

CFile****************************************************************

FileName [cgtMan.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Clock gating package.]

Synopsis [Decide what gate to use for what flop.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

Function*************************************************************

Synopsis [Checks implication.]

Description []

SideEffects []

SeeAlso []

Definition at line 202 of file sswSim.c.

Function*************************************************************

Synopsis [Counts the number of 1s in the implication.]

Description []

SideEffects []

SeeAlso []

Definition at line 270 of file sswSim.c.

|

extern |

Function*************************************************************

Synopsis [Counts the number of 1s in the implication.]

Description []

SideEffects []

SeeAlso []

Definition at line 237 of file sswSim.c.

Function*************************************************************

Synopsis [Counts the number of one's in the pattern of the object.]

Description []

SideEffects []

SeeAlso []

Definition at line 333 of file sswSim.c.

Function*************************************************************

Synopsis [Counts the number of one's in the pattern of the objects.]

Description []

SideEffects []

SeeAlso []

Definition at line 362 of file sswSim.c.