Go to the source code of this file.

Classes | |

| struct | Ssw_Pars_t_ |

| struct | Ssw_RarPars_t_ |

Typedefs | |

| typedef typedefABC_NAMESPACE_HEADER_START struct Ssw_Pars_t_ | Ssw_Pars_t |

| INCLUDES ///. | |

| typedef struct Ssw_RarPars_t_ | Ssw_RarPars_t |

| typedef struct Ssw_Sml_t_ | Ssw_Sml_t |

| typedef typedefABC_NAMESPACE_HEADER_START struct Ssw_Pars_t_ Ssw_Pars_t |

INCLUDES ///.

CFile****************************************************************

FileName [ssw.h]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Inductive prover with constraints.]

Synopsis [External declarations.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 1, 2008.]

Revision [

] PARAMETERS /// BASIC TYPES ///

| typedef struct Ssw_RarPars_t_ Ssw_RarPars_t |

| typedef struct Ssw_Sml_t_ Ssw_Sml_t |

|

extern |

MACRO DEFINITIONS ///.

FUNCTION DECLARATIONS ///

Function*************************************************************

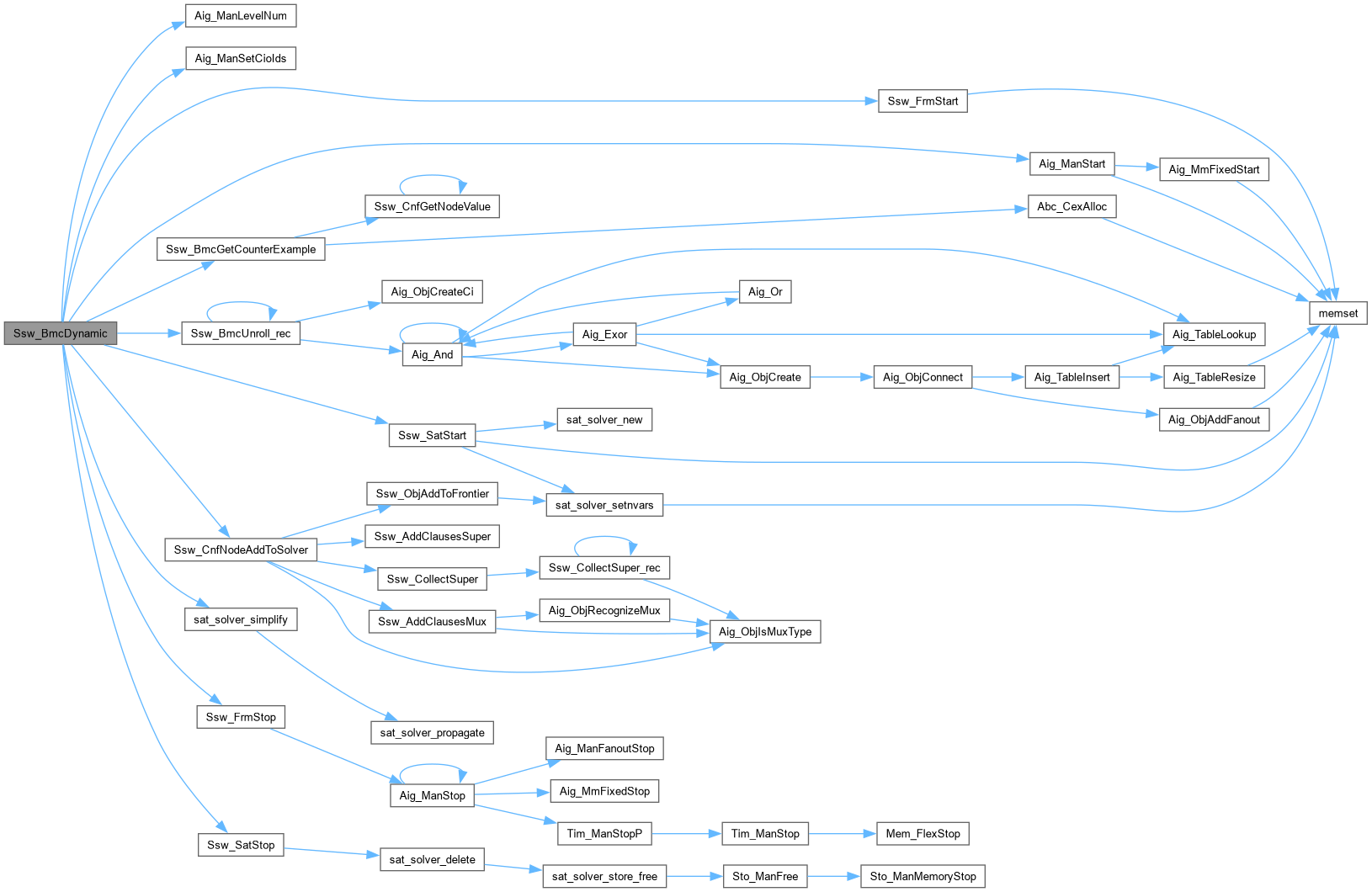

Synopsis [Performs BMC for the given AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 126 of file sswBmc.c.

|

extern |

Function*************************************************************

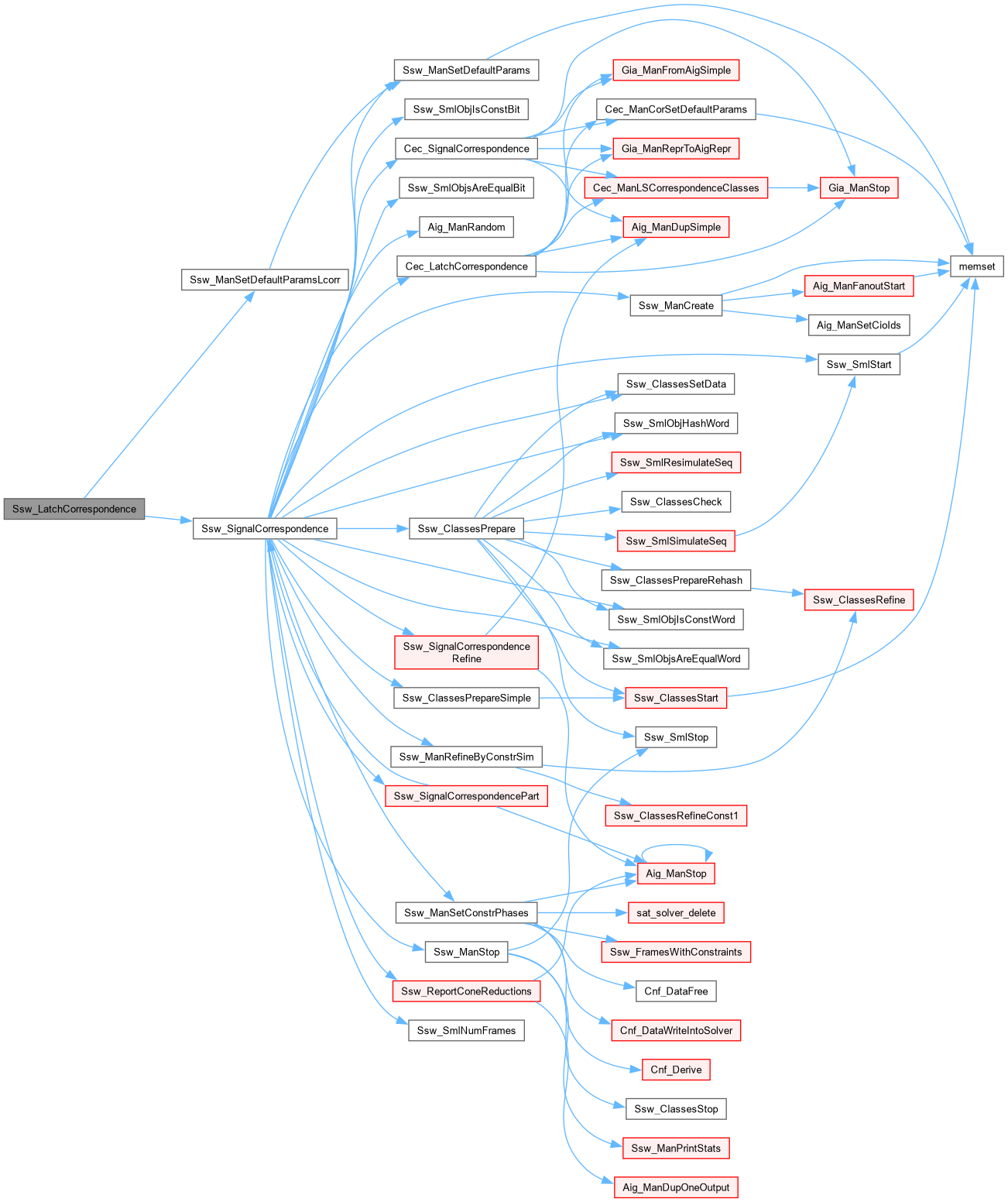

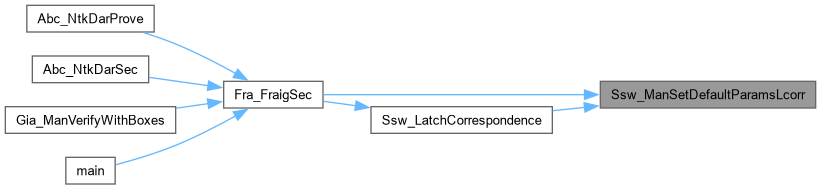

Synopsis [Performs computation of latch correspondence.]

Description []

SideEffects []

SeeAlso []

Definition at line 545 of file sswCore.c.

Function*************************************************************

Synopsis [Finds one satisfiable assignment of the timeframes.]

Description []

SideEffects []

SeeAlso []

Definition at line 100 of file sswConstr.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [sswCore.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Inductive prover with constraints.]

Synopsis [The core procedures.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 1, 2008.]

Revision [

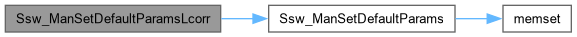

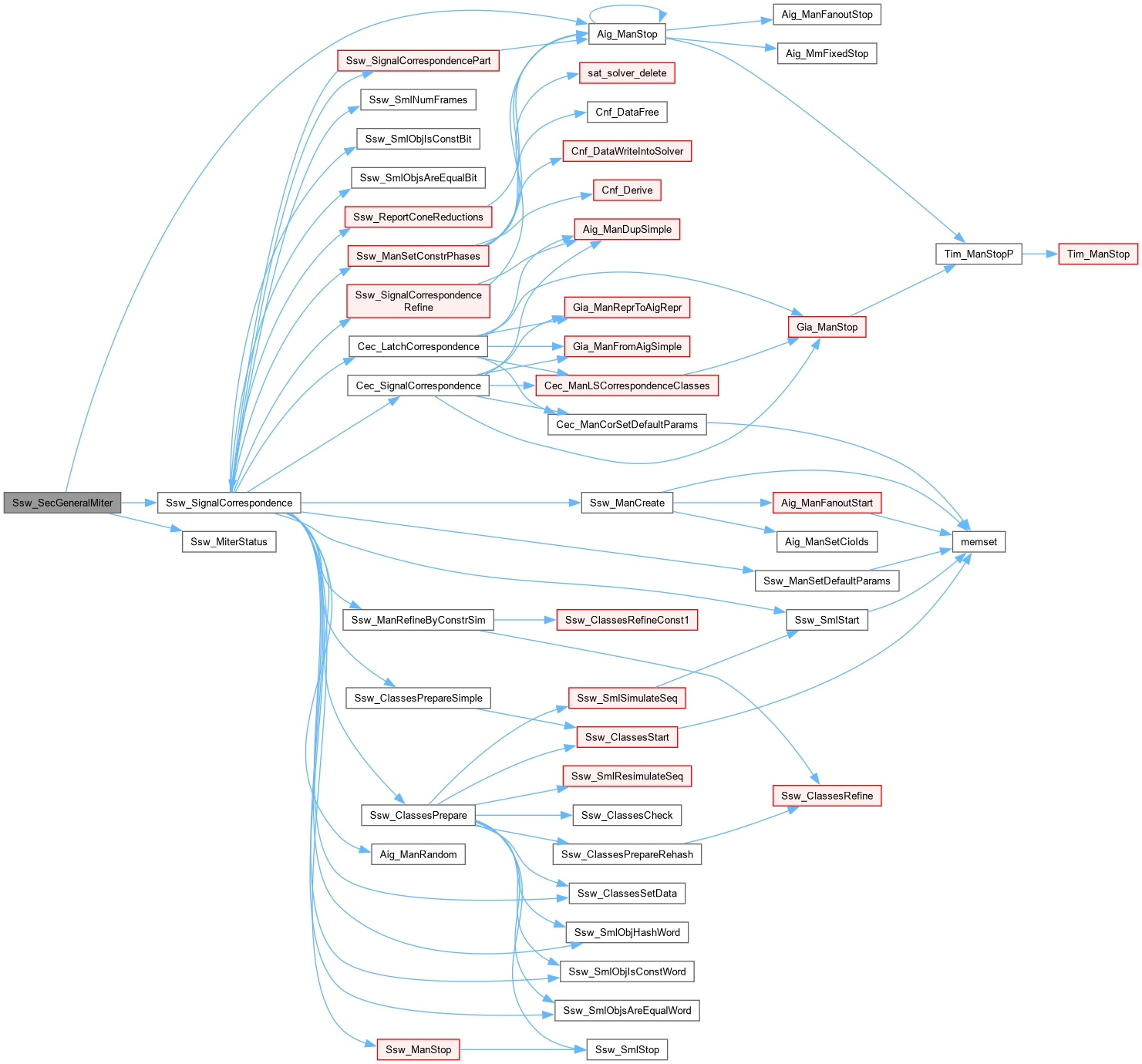

] FUNCTION DEFINITIONS /// Function*************************************************************

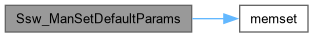

Synopsis [This procedure sets default parameters.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file sswCore.c.

|

extern |

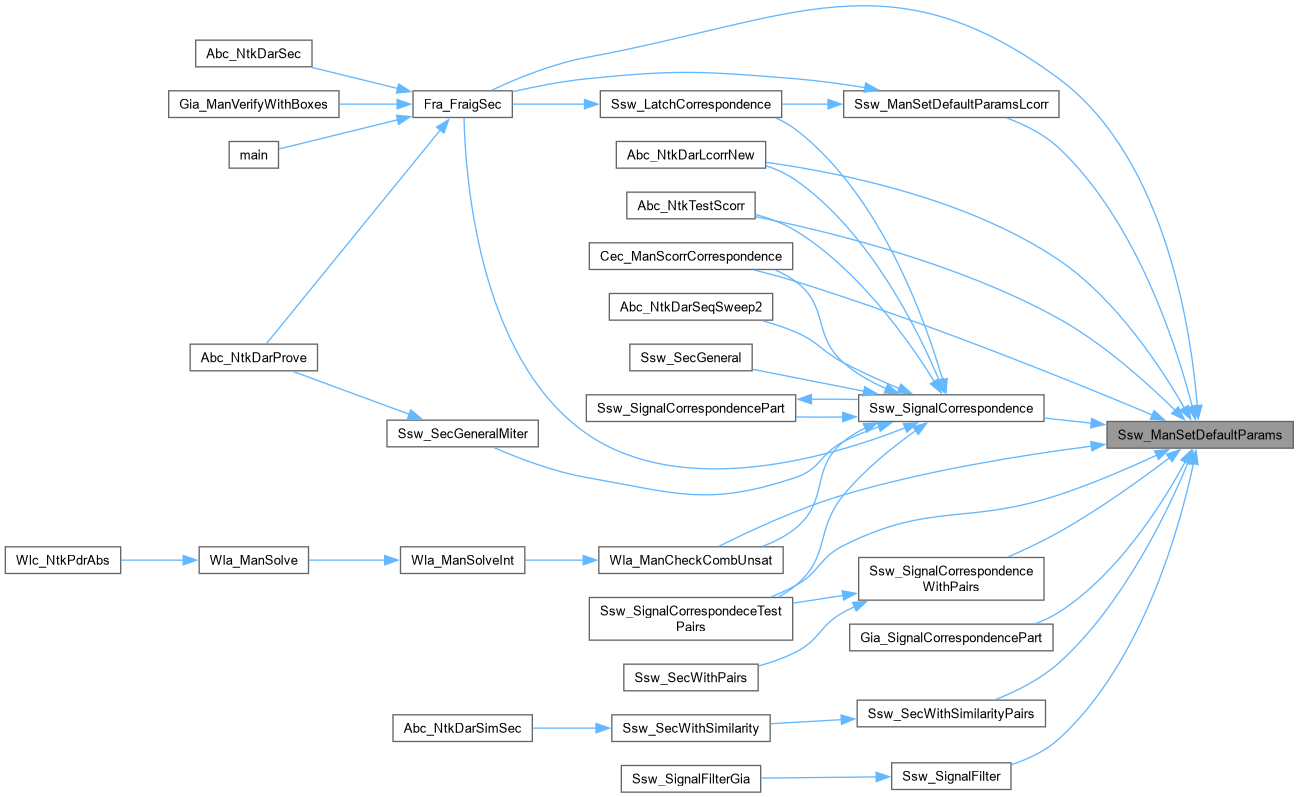

Function*************************************************************

Synopsis [This procedure sets default parameters.]

Description []

SideEffects []

SeeAlso []

Definition at line 93 of file sswCore.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [sswPairs.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Inductive prover with constraints.]

Synopsis [Calls to the SAT solver.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 1, 2008.]

Revision [

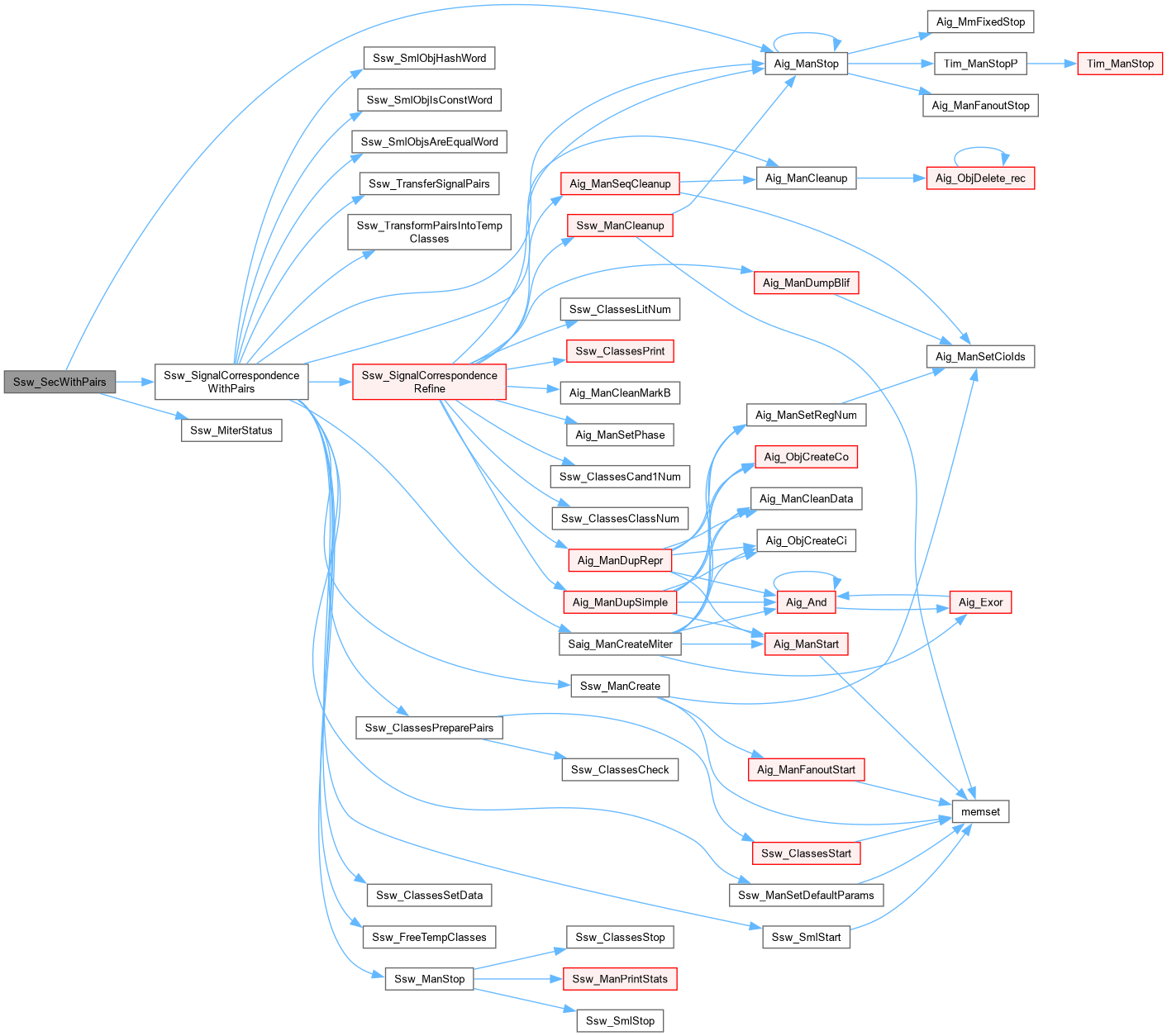

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Reports the status of the miter.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file sswPairs.c.

|

extern |

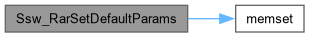

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

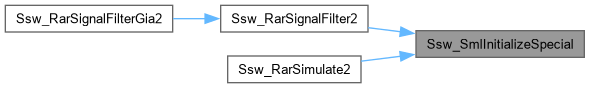

Definition at line 102 of file sswRarity.c.

|

extern |

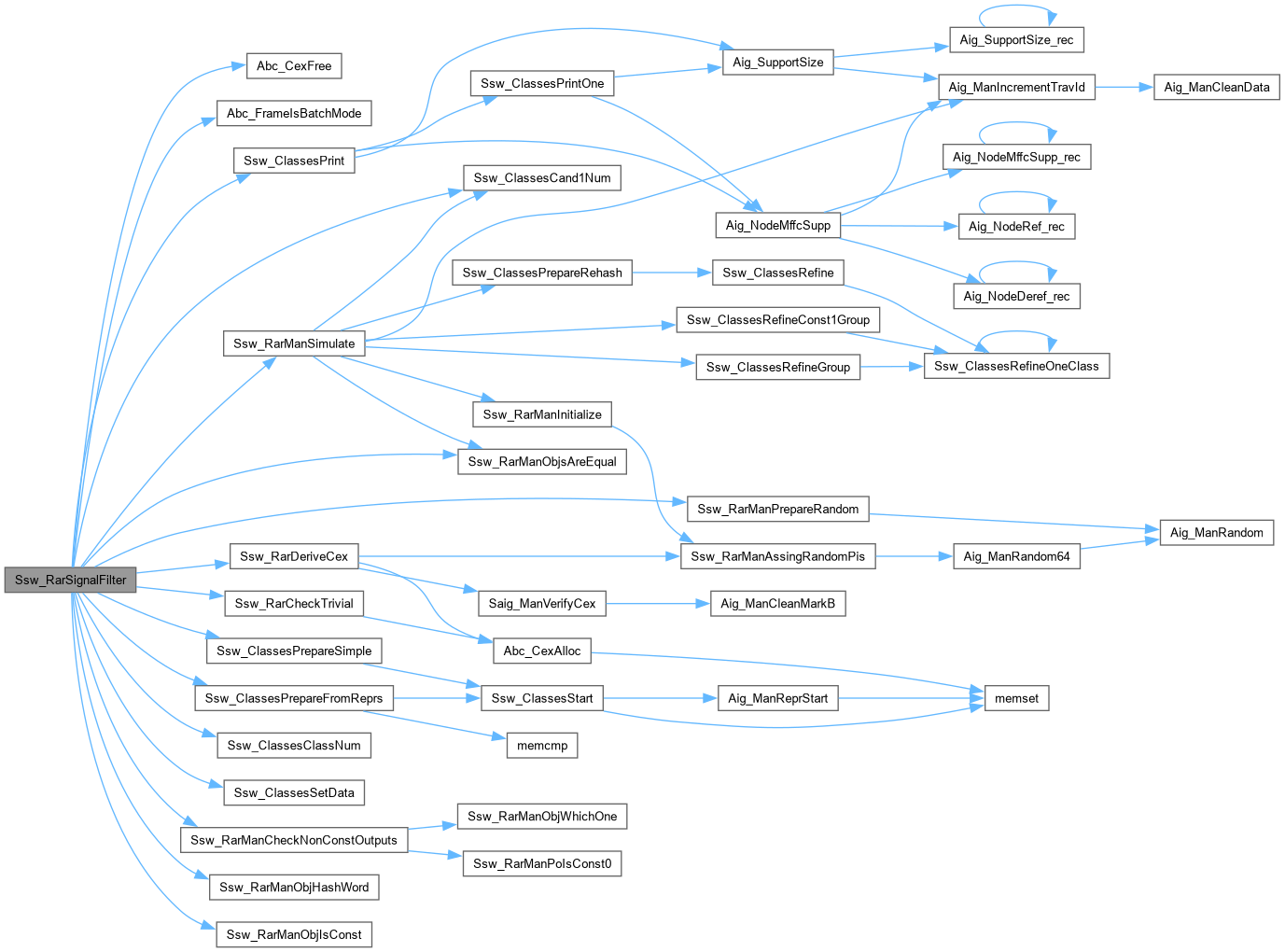

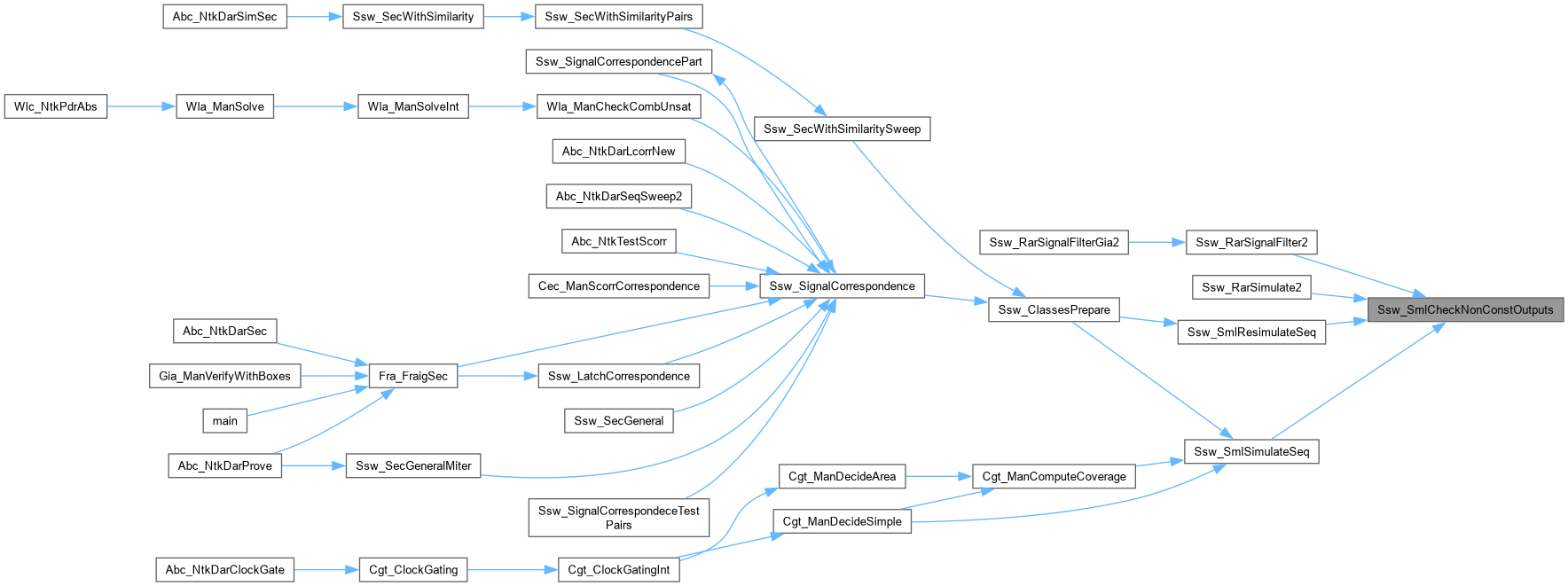

Function*************************************************************

Synopsis [Filter equivalence classes of nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 1221 of file sswRarity.c.

|

extern |

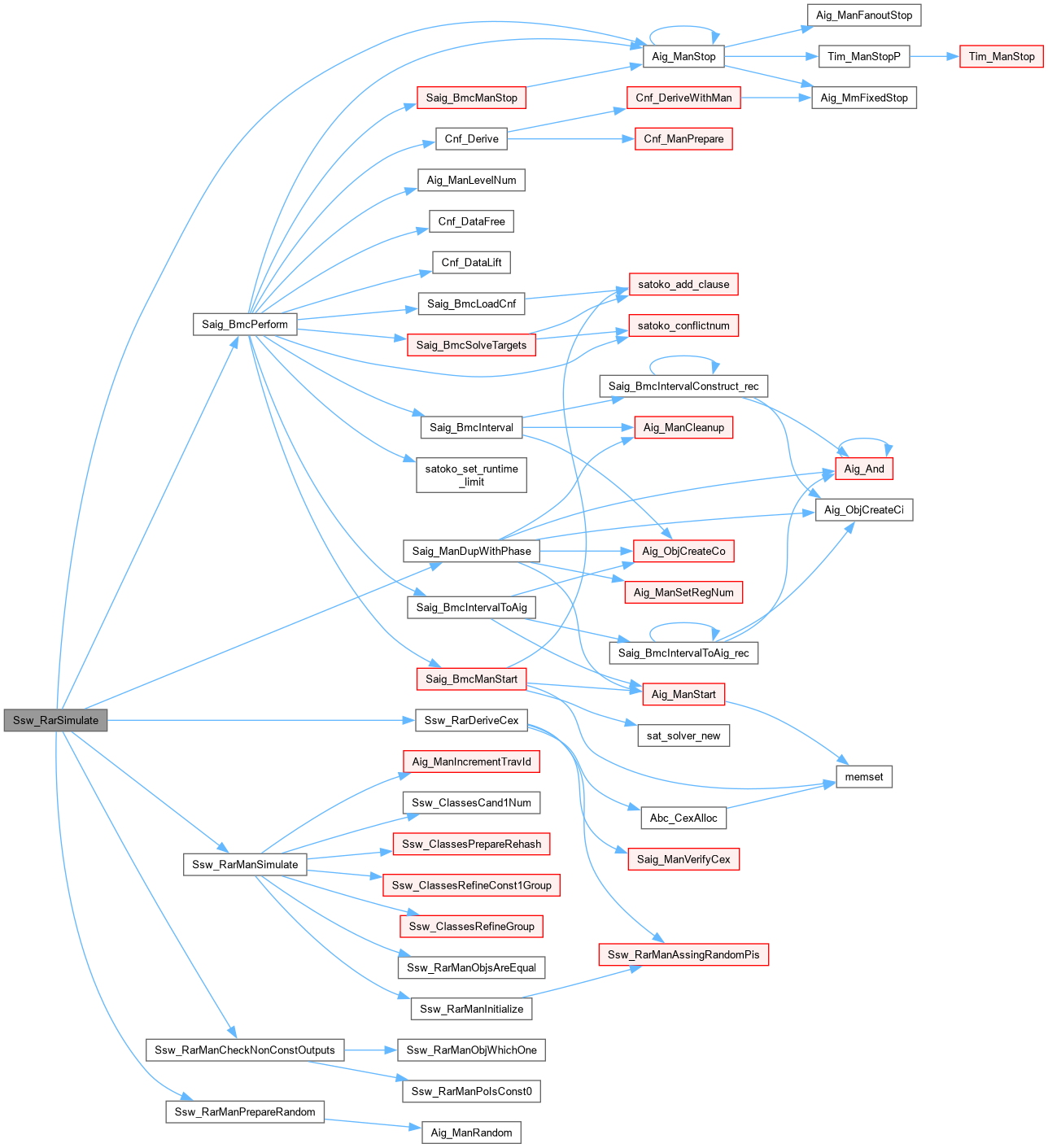

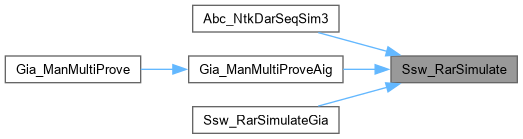

Function*************************************************************

Synopsis [Perform sequential simulation.]

Description []

SideEffects []

SeeAlso []

Definition at line 973 of file sswRarity.c.

|

extern |

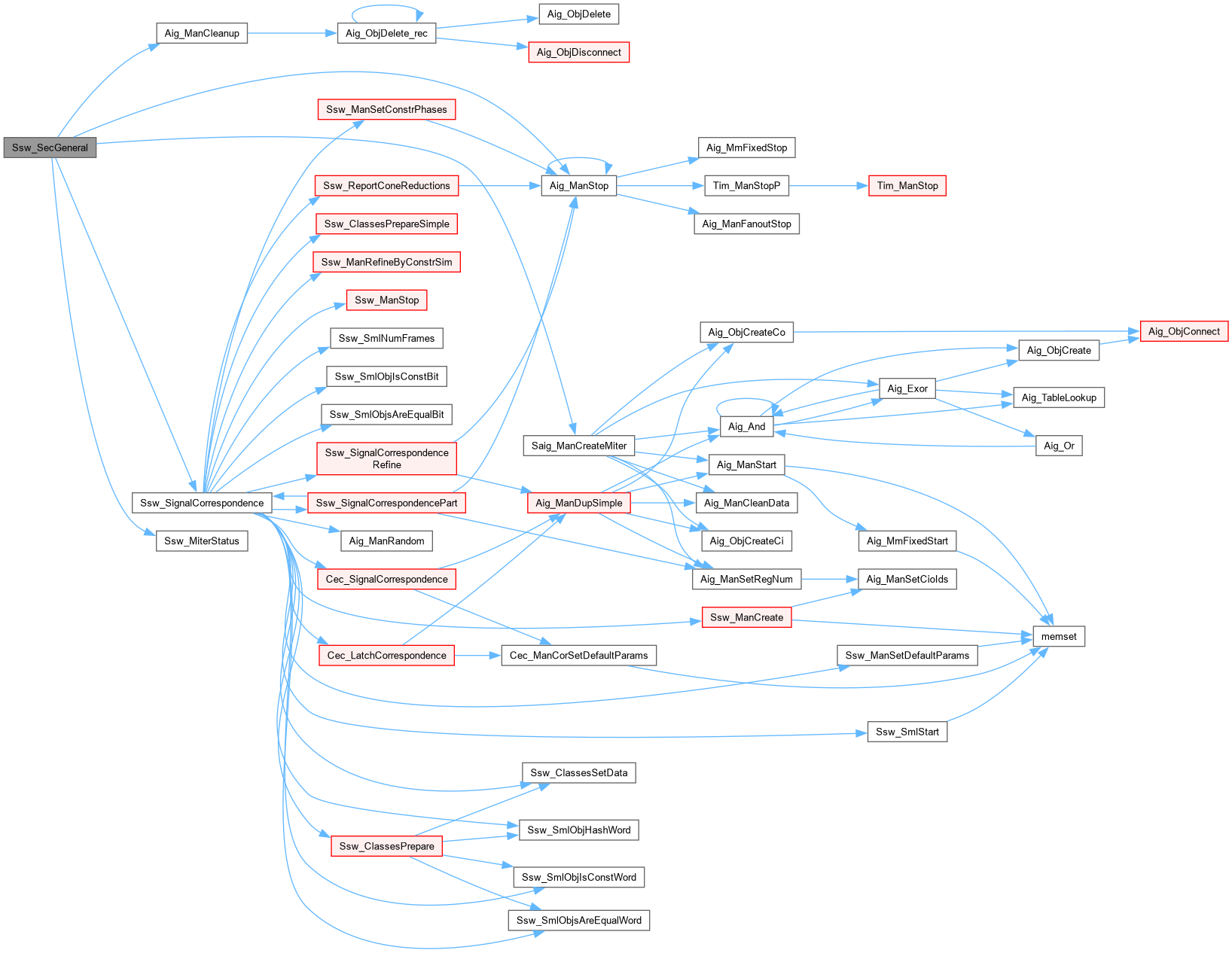

Function*************************************************************

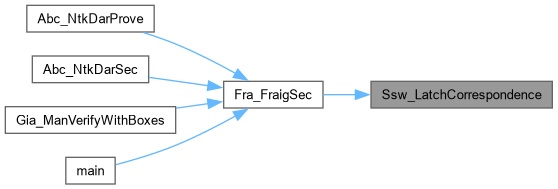

Synopsis [Runs inductive SEC for the miter of two AIGs.]

Description []

SideEffects []

SeeAlso []

Definition at line 415 of file sswPairs.c.

|

extern |

Function*************************************************************

Synopsis [Runs inductive SEC for the miter of two AIGs.]

Description []

SideEffects []

SeeAlso []

Definition at line 452 of file sswPairs.c.

|

extern |

Function*************************************************************

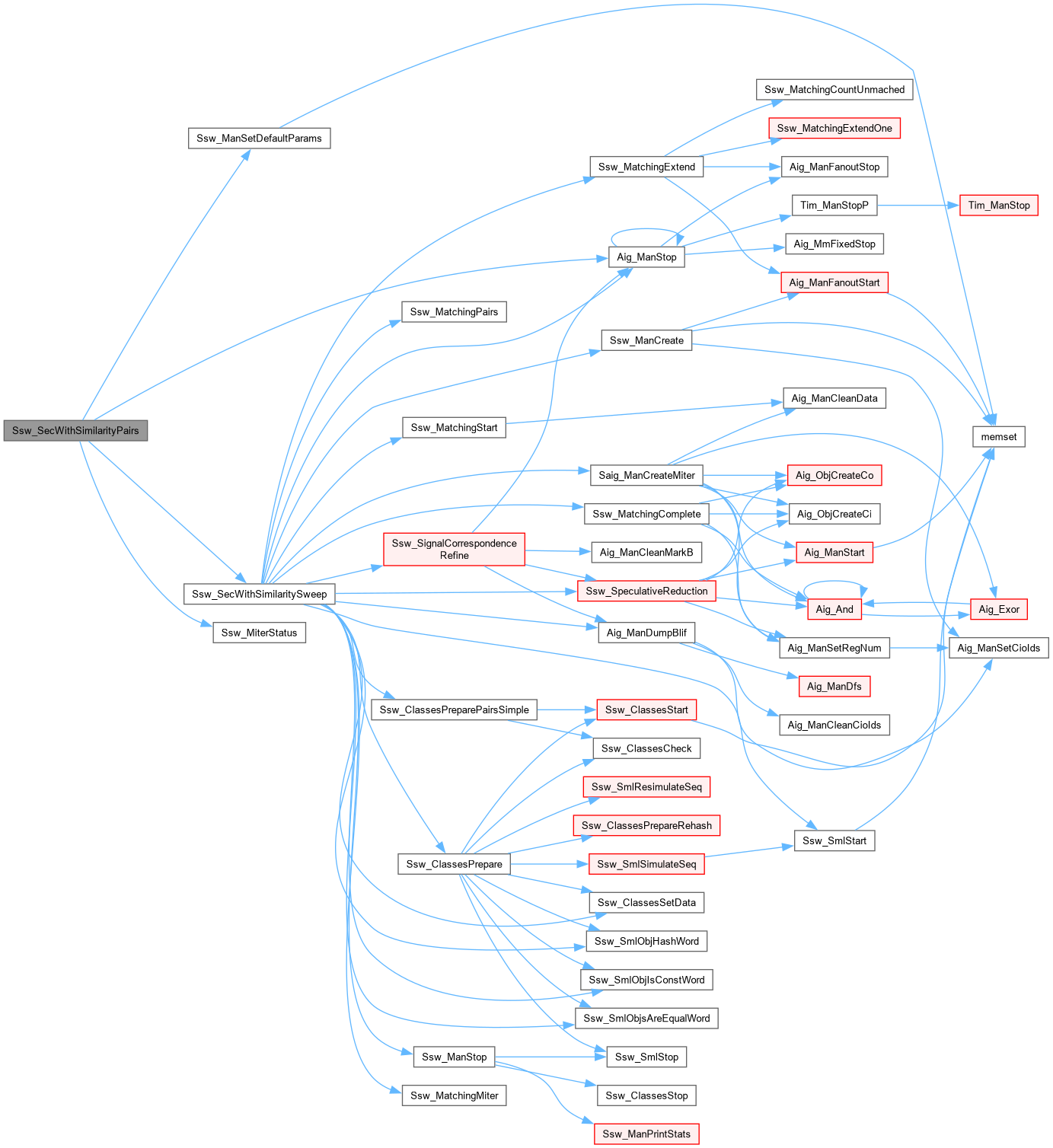

Synopsis [Runs inductive SEC for the miter of two AIGs with node pairs defined.]

Description []

SideEffects []

SeeAlso []

Definition at line 380 of file sswPairs.c.

|

extern |

Function*************************************************************

Synopsis [Solves SEC with structural similarity.]

Description []

SideEffects []

SeeAlso []

Definition at line 542 of file sswIslands.c.

|

extern |

Function*************************************************************

Synopsis [Solves SEC with structural similarity.]

Description [The first two arguments are pointers to the AIG managers. The third argument is the array of pairs of IDs of structurally equivalent nodes from the first and second managers, respectively.]

SideEffects [The managers will be updated by adding "islands of difference".]

SeeAlso []

Definition at line 478 of file sswIslands.c.

|

extern |

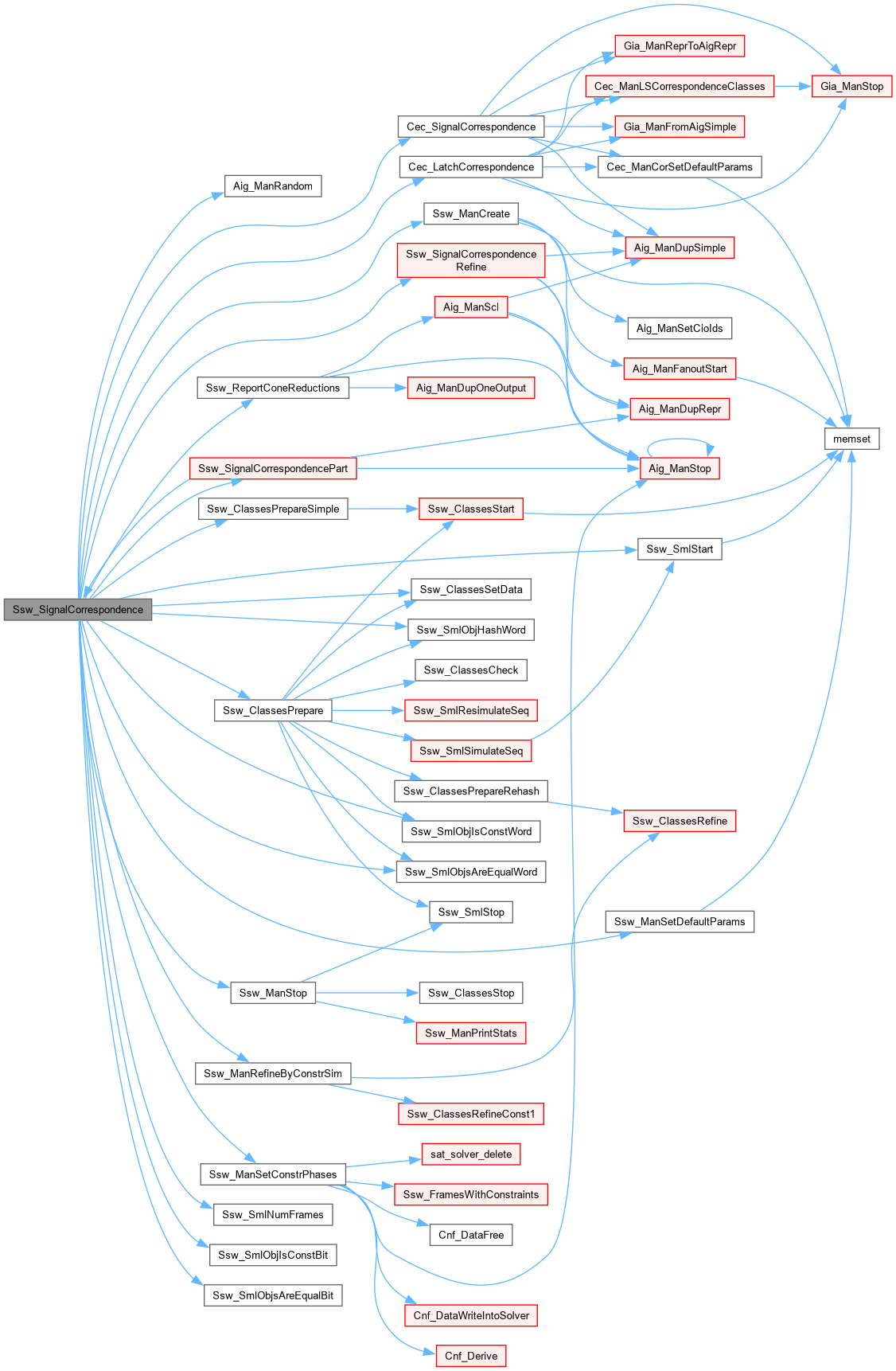

Function*************************************************************

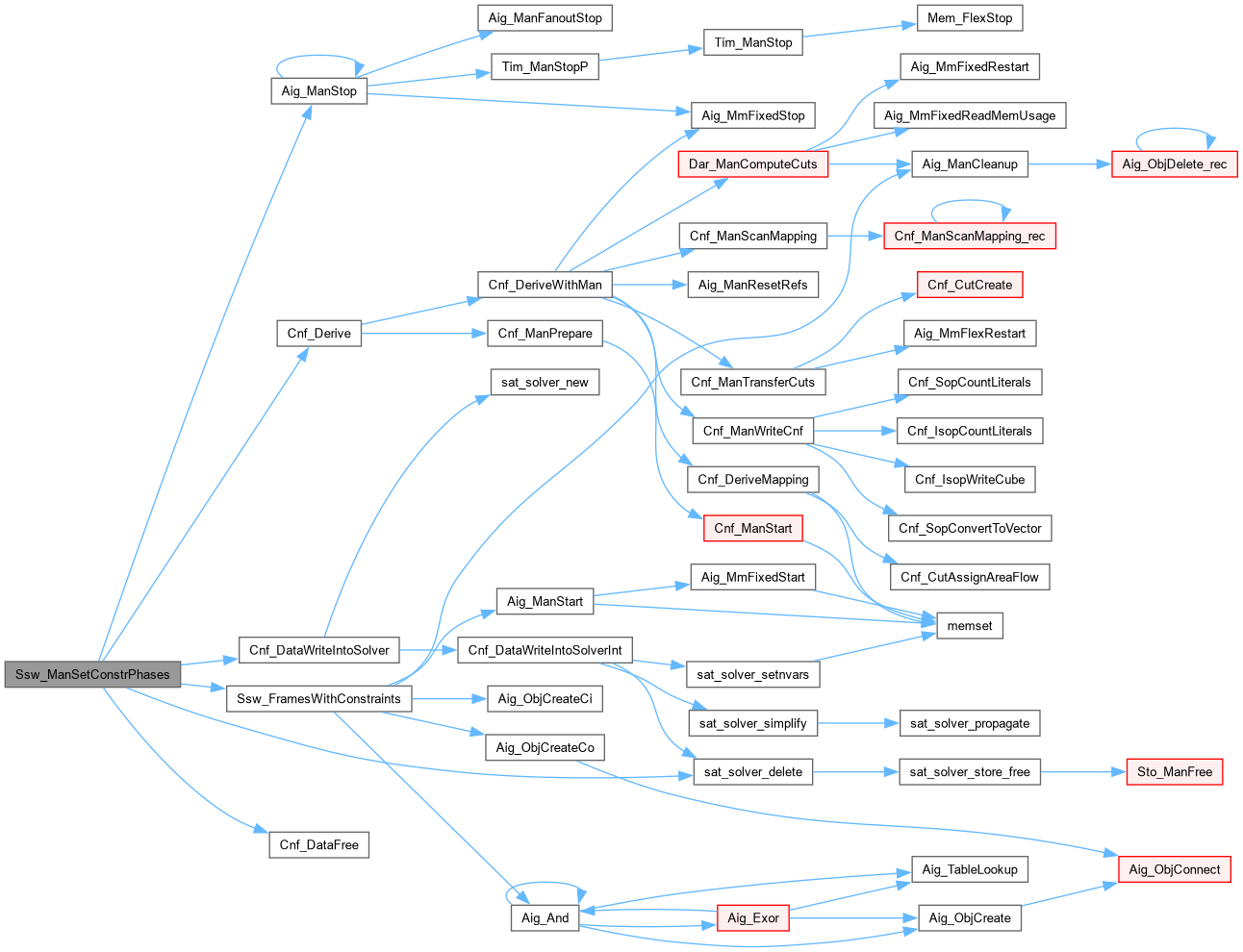

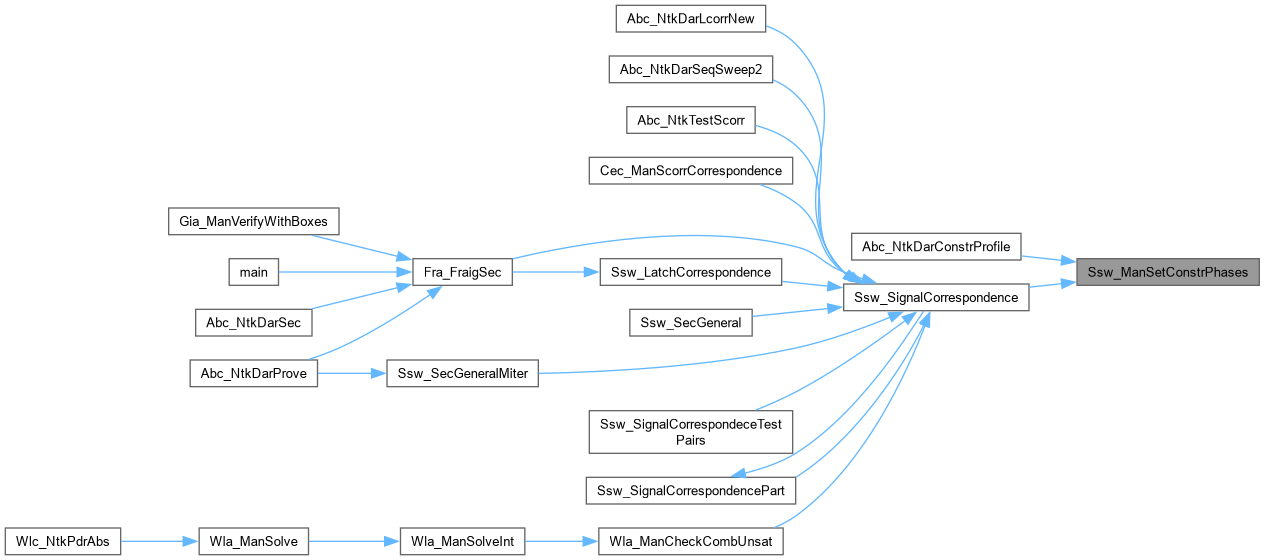

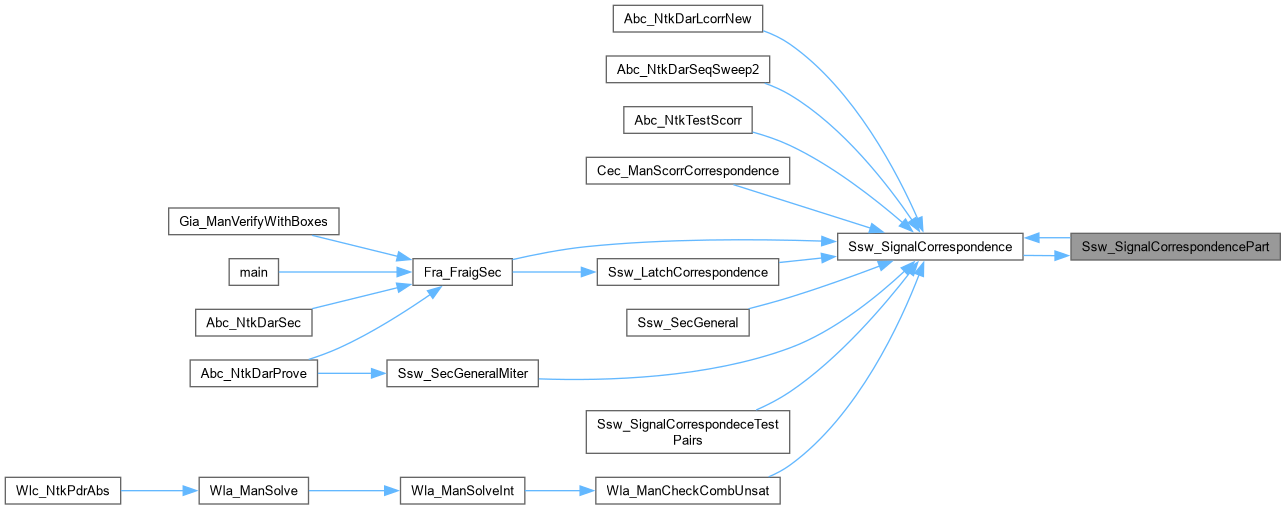

Synopsis [Performs computation of signal correspondence with constraints.]

Description []

SideEffects []

SeeAlso []

Definition at line 436 of file sswCore.c.

|

extern |

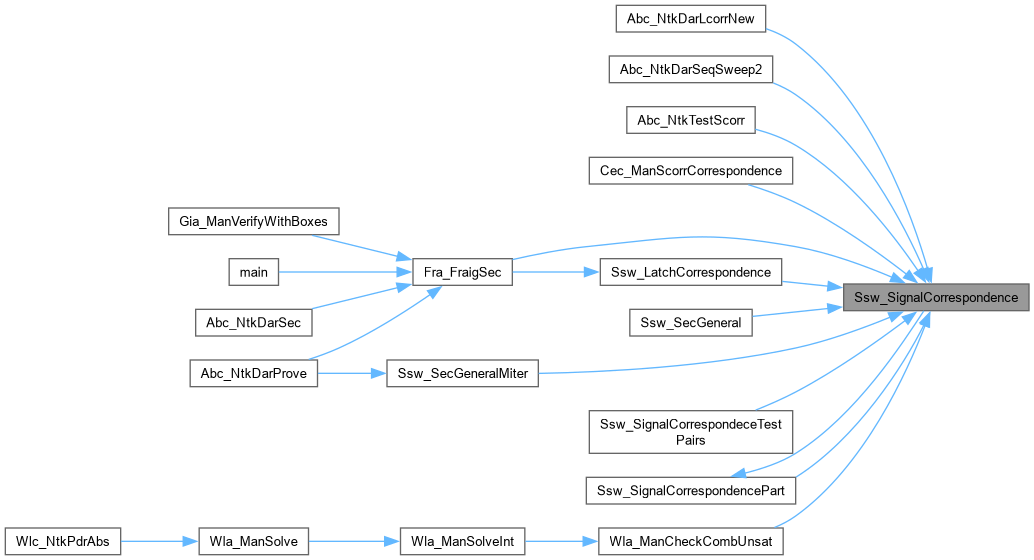

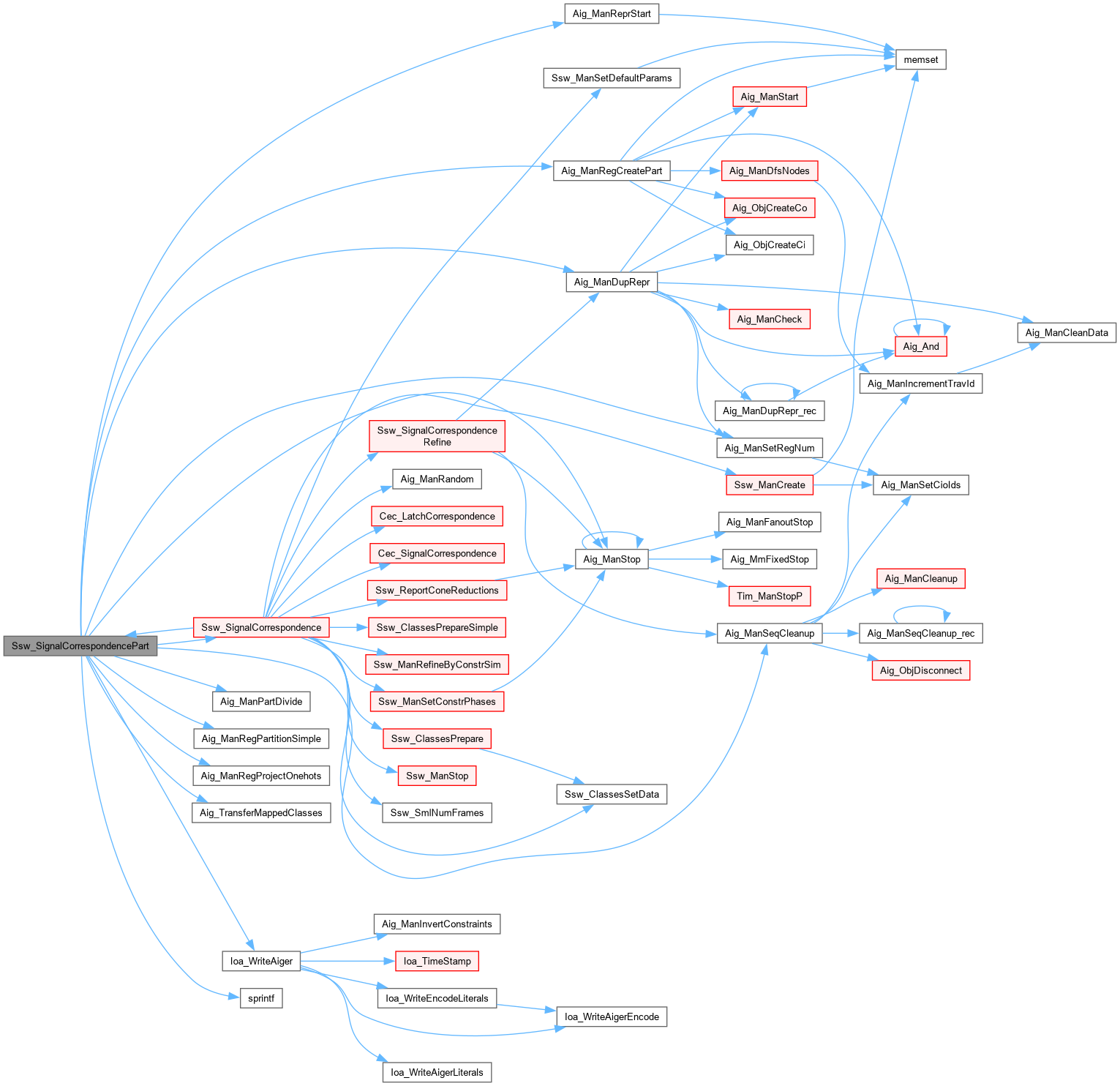

Function*************************************************************

Synopsis [Performs partitioned sequential SAT sweeping.]

Description []

SideEffects []

SeeAlso []

Definition at line 214 of file sswPart.c.

|

extern |

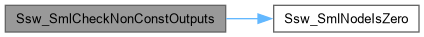

Function*************************************************************

Synopsis [Check if any of the POs becomes non-constant.]

Description []

SideEffects []

SeeAlso []

Definition at line 980 of file sswSim.c.

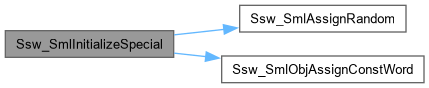

Function*************************************************************

Synopsis [Assings random simulation info for the PIs.]

Description []

SideEffects []

SeeAlso []

Definition at line 928 of file sswSim.c.

|

extern |

|

extern |

Function*************************************************************

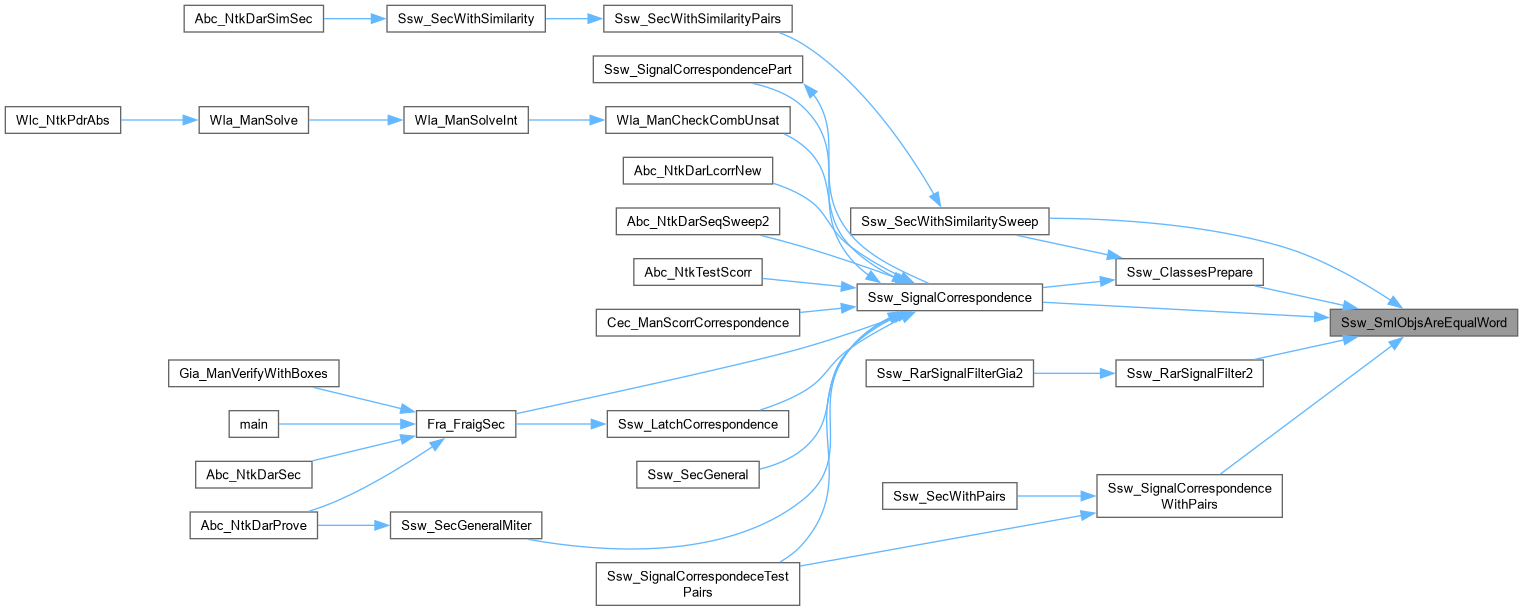

Synopsis [Returns 1 if simulation infos are equal.]

Description []

SideEffects []

SeeAlso []

Definition at line 124 of file sswSim.c.

Function*************************************************************

Synopsis [Get simulation data.]

Description []

SideEffects []

SeeAlso []

Function*************************************************************

Synopsis [Returns the pointer to the simulation info of the node.]

Description [The simulation info is normalized unless procedure Ssw_SmlUnnormalize() is called in advance.]

SideEffects []

SeeAlso []

Function*************************************************************

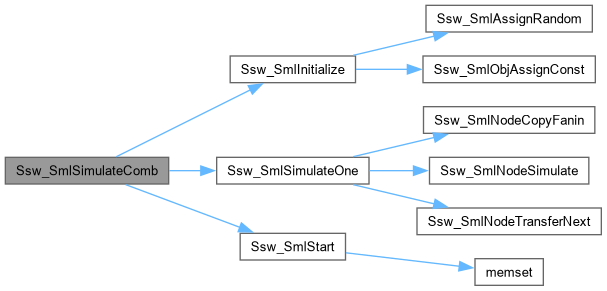

Synopsis [Performs simulation of the uninitialized circuit.]

Description []

SideEffects []

SeeAlso []

Definition at line 1228 of file sswSim.c.

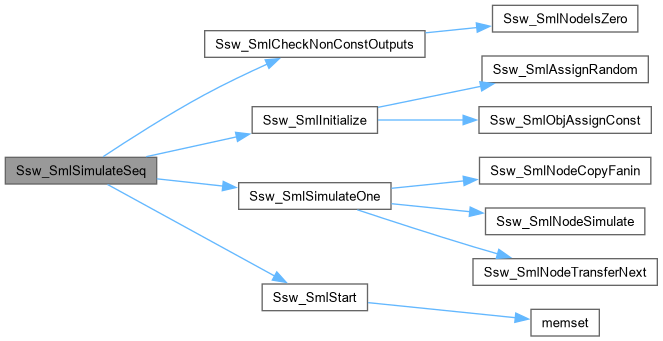

Function*************************************************************

Synopsis [Performs simulation of the initialized circuit.]

Description []

SideEffects []

SeeAlso []

Definition at line 1248 of file sswSim.c.

|

extern |

|

extern |

Function*************************************************************

Synopsis [Converts simulation information to be not normallized.]

Description []

SideEffects []

SeeAlso []

Definition at line 1044 of file sswSim.c.