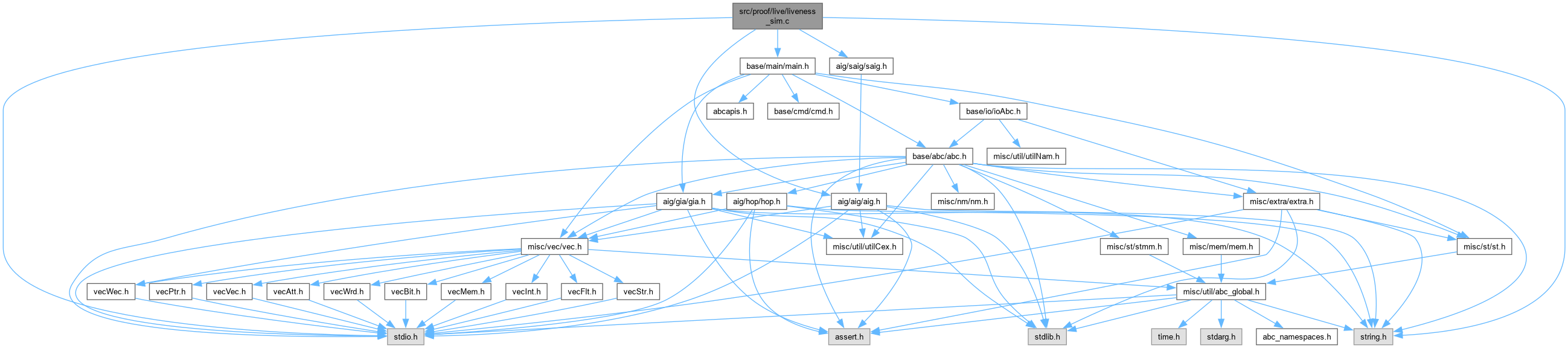

#include <stdio.h>#include "base/main/main.h"#include "aig/aig/aig.h"#include "aig/saig/saig.h"#include <string.h>

Go to the source code of this file.

Macros | |

| #define | PROPAGATE_NAMES |

Functions | |

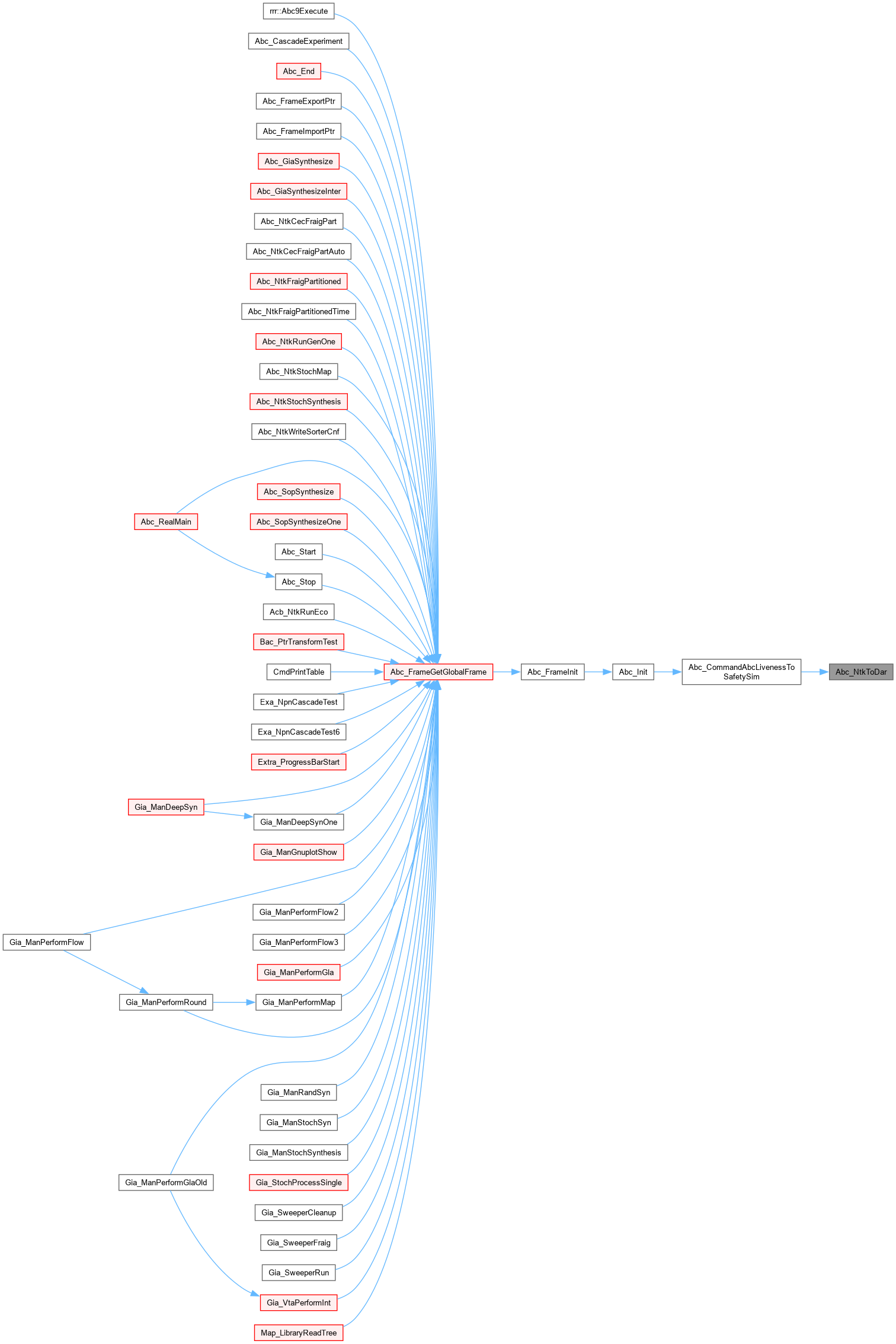

| Aig_Man_t * | Abc_NtkToDar (Abc_Ntk_t *pNtk, int fExors, int fRegisters) |

| DECLARATIONS ///. | |

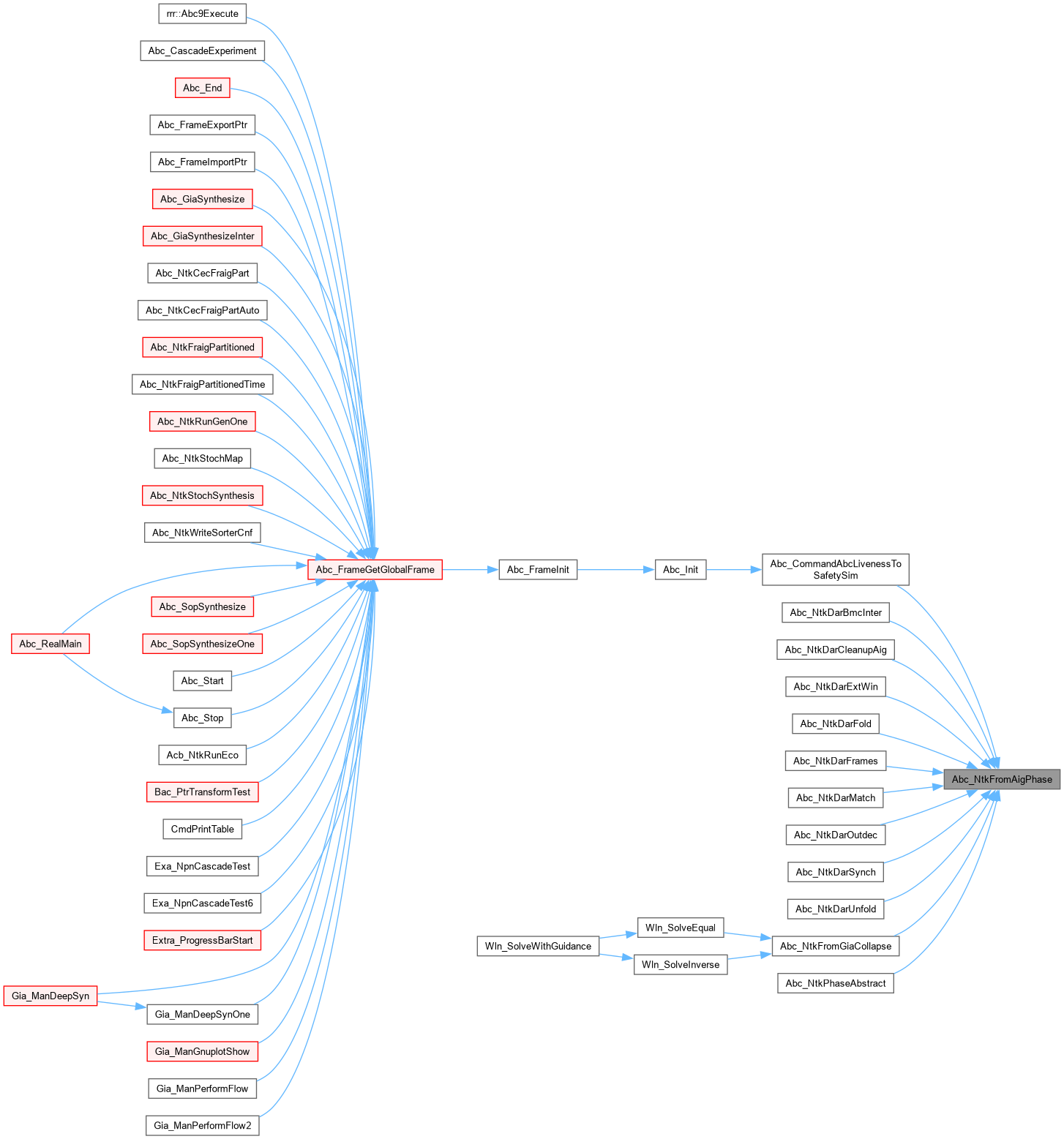

| Abc_Ntk_t * | Abc_NtkFromAigPhase (Aig_Man_t *pMan) |

| DECLARATIONS ///. | |

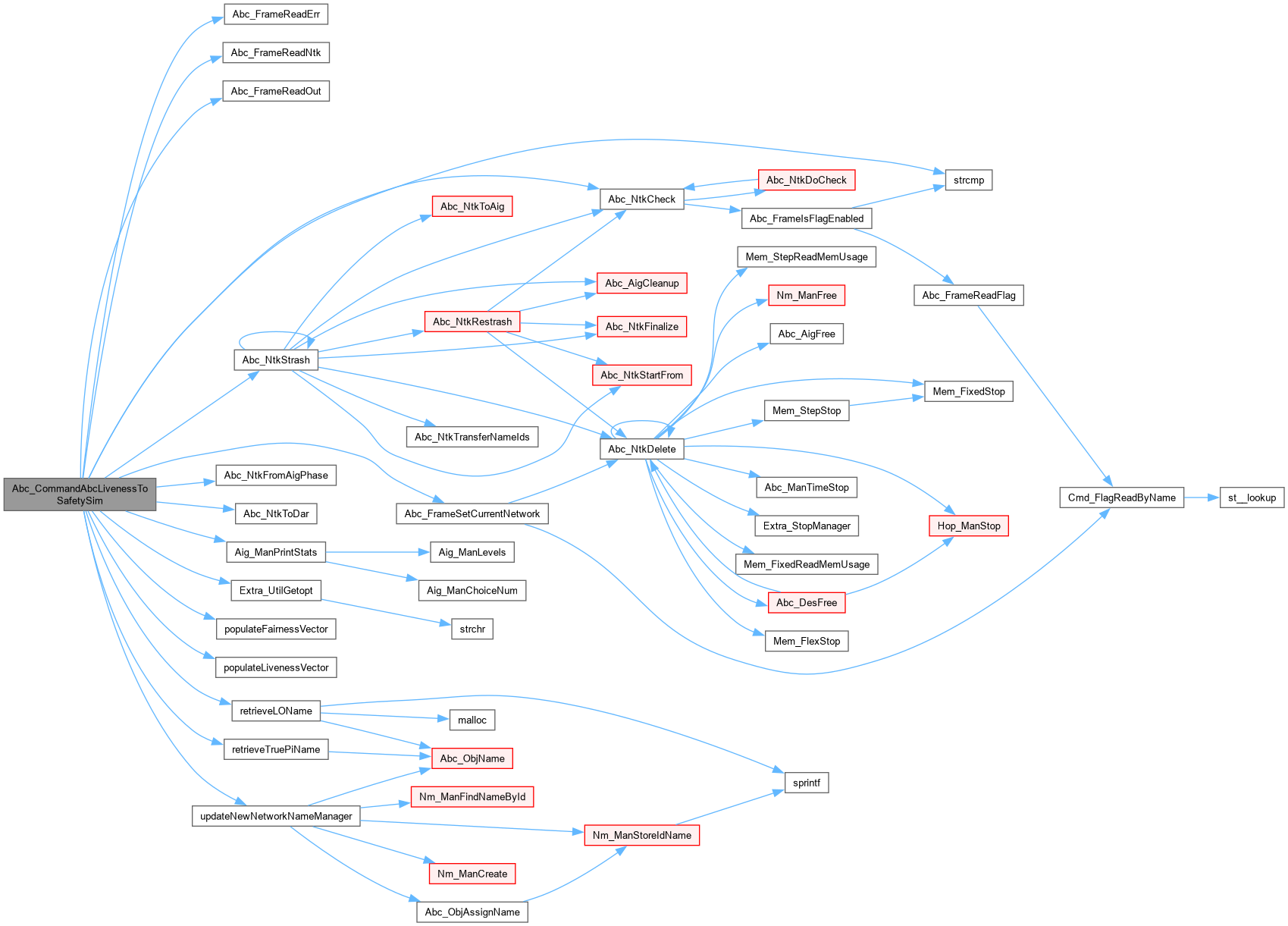

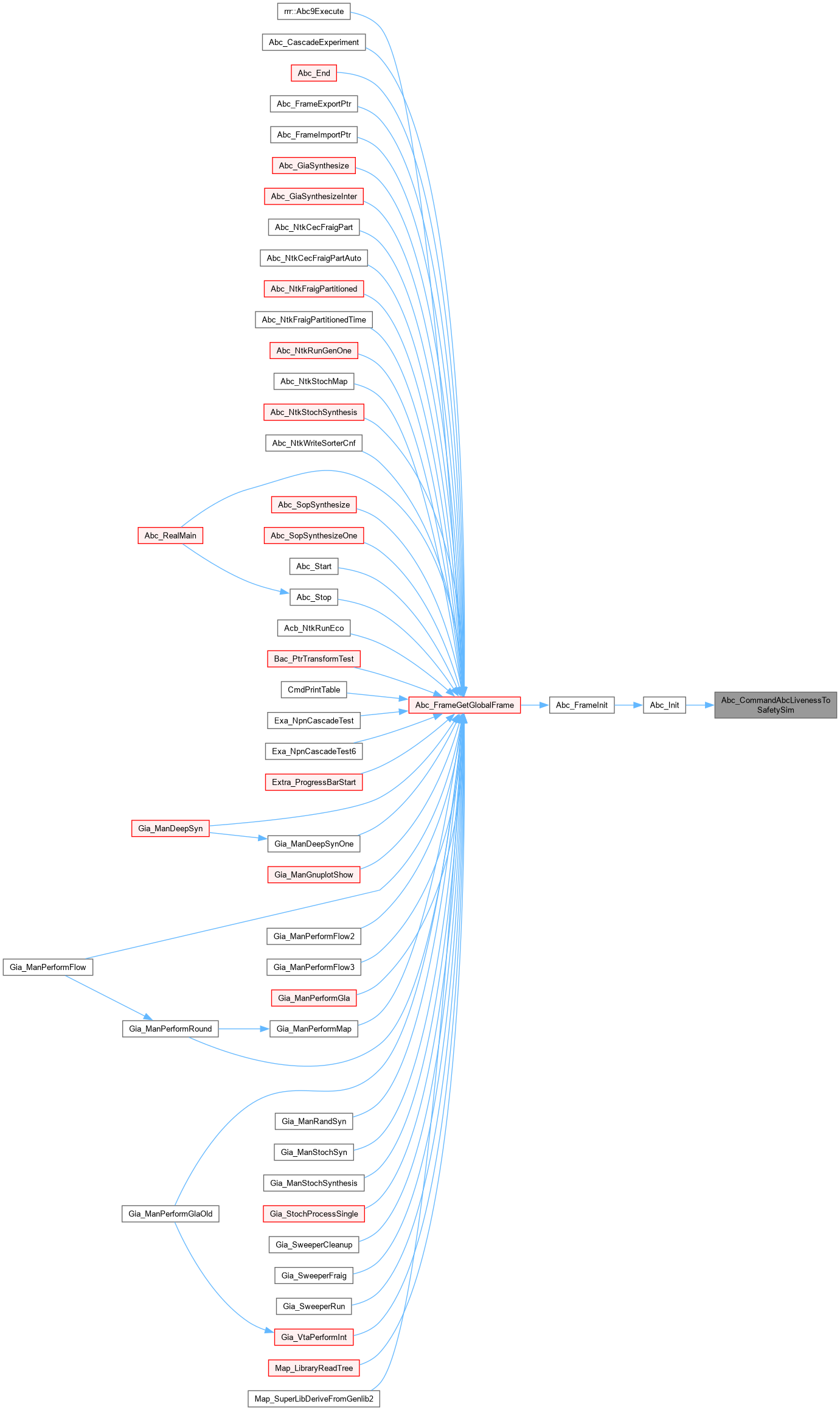

| int | Abc_CommandAbcLivenessToSafetySim (Abc_Frame_t *pAbc, int argc, char **argv) |

Variables | |

| Vec_Ptr_t * | vecPis |

| Vec_Ptr_t * | vecPiNames |

| Vec_Ptr_t * | vecLos |

| Vec_Ptr_t * | vecLoNames |

| #define PROPAGATE_NAMES |

CFile****************************************************************

FileName [liveness_sim.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Liveness property checking.]

Synopsis [Main implementation module.]

Author [Sayak Ray]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - January 1, 2009.]

Revision [

]

Definition at line 30 of file liveness_sim.c.

| int Abc_CommandAbcLivenessToSafetySim | ( | Abc_Frame_t * | pAbc, |

| int | argc, | ||

| char ** | argv ) |

Definition at line 754 of file liveness_sim.c.

DECLARATIONS ///.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [This procedure should be called after seq sweeping, which changes the number of registers.]

SideEffects []

SeeAlso []

Definition at line 595 of file abcDar.c.

DECLARATIONS ///.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [Assumes that registers are ordered after PIs/POs.]

SideEffects []

SeeAlso []

Definition at line 237 of file abcDar.c.

| Vec_Ptr_t * vecLoNames |

Definition at line 173 of file liveness_sim.c.

|

extern |

Definition at line 219 of file liveness.c.

| Vec_Ptr_t * vecPiNames |

Definition at line 172 of file liveness_sim.c.

|

extern |

Definition at line 218 of file liveness.c.