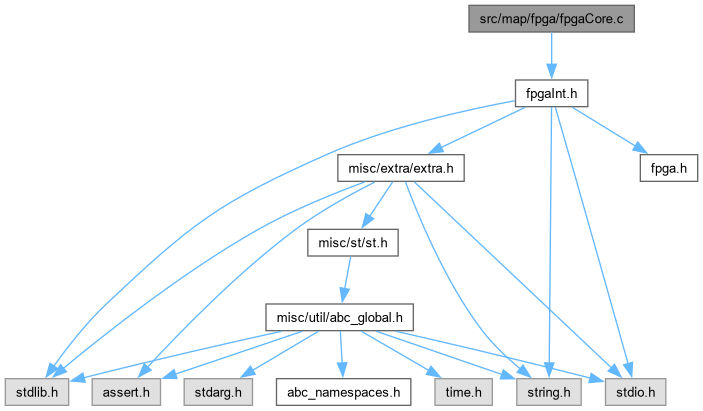

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

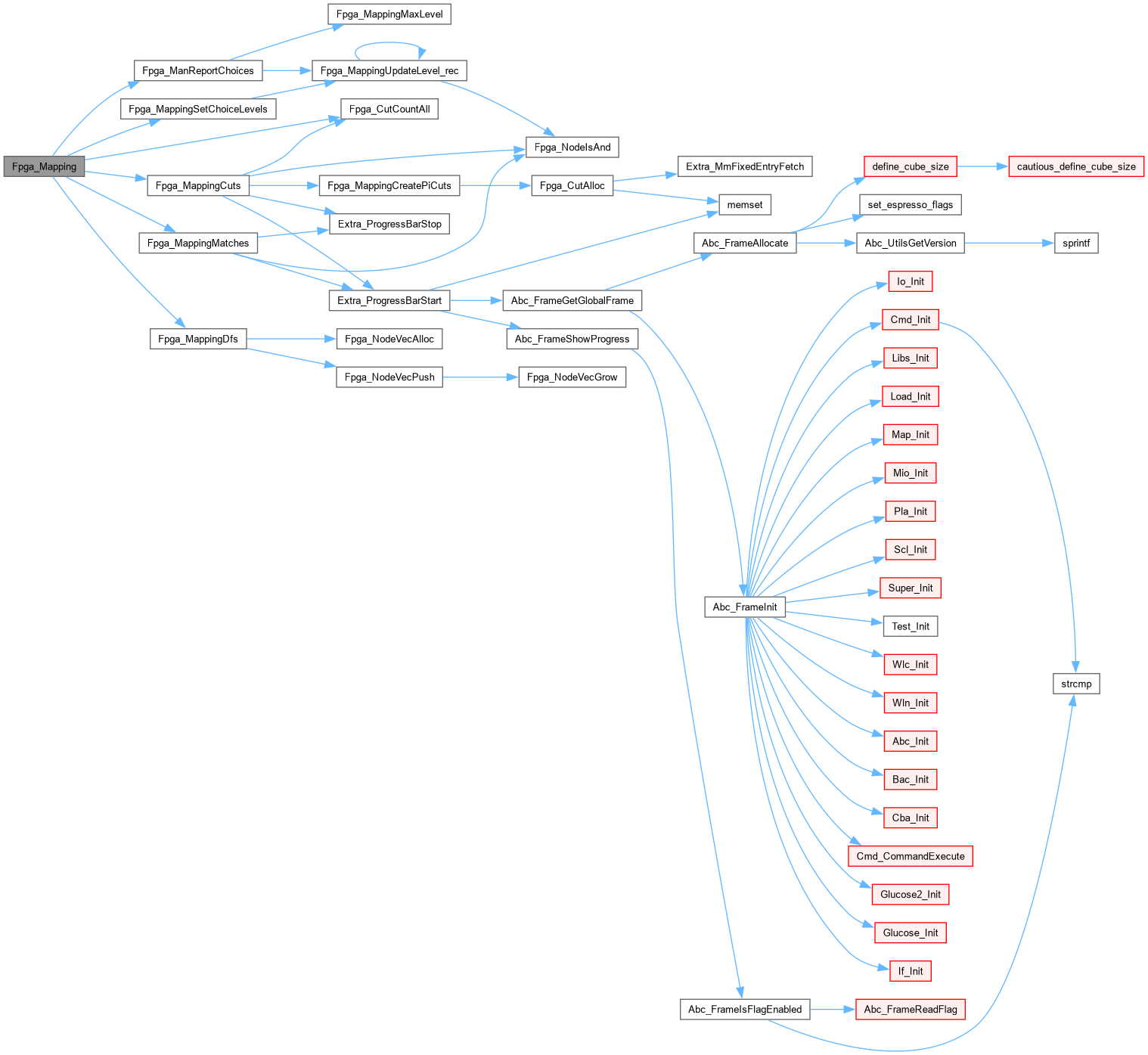

| int | Fpga_Mapping (Fpga_Man_t *p) |

| FUNCTION DEFINITIONS ///. | |

Variables | |

| clock_t | s_MappingTime |

| DECLARATIONS ///. | |

| int | s_MappingMem |

| int Fpga_Mapping | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Performs technology mapping for the given object graph.]

Description [The object graph is stored in the mapping manager. First, all the AND-nodes, which fanout into the POs, are collected in the DFS fashion. Next, three steps are performed: the k-feasible cuts are computed for each node, the truth tables are computed for each cut, and the delay-optimal matches are assigned for each node.]

SideEffects []

SeeAlso []

Definition at line 53 of file fpgaCore.c.

|

extern |

Definition at line 48 of file abcPrint.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [abcPrint.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Printing statistics.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

Definition at line 47 of file abcPrint.c.