345{

346 int fUseSimpleCnf = 0;

347 int fUseOldSimulation = 0;

348

349

350

351

352

353

359 int nNodesBeg, nRegsBeg;

360 int nIter = -1;

361 int i;

362 abctime clk = Abc_Clock(), clk2;

364

365 if ( Aig_ManNodeNum(pManAig) == 0 )

366 {

368

371 }

372 assert( Aig_ManRegNum(pManAig) > 0 );

374

375

377 {

379 printf( "Partitioning was disabled to allow implication writing.\n" );

380 }

381

383 || (pManAig->vClockDoms && Vec_VecSize(pManAig->vClockDoms) > 0) )

385

386 nNodesBeg = Aig_ManNodeNum(pManAig);

387 nRegsBeg = Aig_ManRegNum(pManAig);

388

389

390

391

392

394 pPars->nFramesP = pParams->

nFramesP;

395 pPars->nFramesK = pParams->

nFramesK;

396 pPars->nMaxImps = pParams->

nMaxImps;

397 pPars->nMaxLevs = pParams->

nMaxLevs;

398 pPars->fVerbose = pParams->

fVerbose;

399 pPars->fRewrite = pParams->

fRewrite;

401 pPars->fUseImps = pParams->

fUseImps;

403 pPars->fUse1Hot = pParams->

fUse1Hot;

404

405 assert( !(pPars->nFramesP > 0 && pPars->fUse1Hot) );

406 assert( !(pPars->nFramesK > 1 && pPars->fUse1Hot) );

407

408

410 p->pPars->nBTLimitNode = 0;

411

412 if ( fUseOldSimulation )

413 {

414 if ( pPars->nFramesP > 0 )

415 {

416 pPars->nFramesP = 0;

417 printf( "Fra_FraigInduction(): Prefix cannot be used.\n" );

418 }

419 p->pSml =

Fra_SmlStart( pManAig, 0, pPars->nFramesK + 1, pPars->nSimWords );

421 }

422 else

423 {

424

425

426

427if ( pPars->fVerbose )

428printf( "Simulating %d AIG nodes for %d cycles ... ", Aig_ManNodeNum(pManAig), pPars->nFramesP + 32 );

430if ( pPars->fVerbose )

431{

432ABC_PRT(

"Time", Abc_Clock() - clk );

433}

435

436

437 if (

p->pPars->fUse1Hot )

439

441 p->pSml =

Fra_SmlStart( pManAig, 0, pPars->nFramesK + 1, pPars->nSimWords );

442 }

443

444

445 if ( pPars->fUseImps )

446 p->pCla->vImps =

Fra_ImpDerive(

p, 5000000, pPars->nMaxImps, pPars->fLatchCorr );

447

448 if ( pParams->

TimeLimit != 0.0 && Abc_Clock() > TimeToStop )

449 {

451 printf( "Fra_FraigInduction(): Runtime limit exceeded.\n" );

452 goto finish;

453 }

454

455

457

458

459

460

462 p->nNodesBeg = nNodesBeg;

463 p->nRegsBeg = nRegsBeg;

464

465

466

467

468

469

470

471

472 p->pCla->fRefinement = 1;

473 for ( nIter = 0;

p->pCla->fRefinement; nIter++ )

474 {

476 int nImpsOld =

p->pCla->vImps? Vec_IntSize(

p->pCla->vImps) : 0;

479

480 if ( pParams->

TimeLimit != 0.0 && Abc_Clock() > TimeToStop )

481 {

483 printf( "Fra_FraigInduction(): Runtime limit exceeded.\n" );

484 goto finish;

485 }

486

487

488 p->pCla->fRefinement = 0;

489

490clk2 = Abc_Clock();

492p->timeTrav += Abc_Clock() - clk2;

493

494

495

496 if (

p->pPars->fRewrite )

498

499

500 if ( fUseSimpleCnf || pPars->fUseImps )

502 else

503 pCnf =

Cnf_Derive(

p->pManFraig, Aig_ManRegNum(

p->pManFraig) );

504

505

506

508 p->nSatVars = pCnf->

nVars;

510 if (

p->pSat == NULL )

511 printf( "Fra_FraigInduction(): Computed CNF is not valid.\n" );

512 if ( pPars->fUseImps )

513 {

515 if (

p->pSat == NULL )

516 printf( "Fra_FraigInduction(): Adding implicationsn to CNF led to a conflict.\n" );

517 }

518

519

522

523

524 Fra_ManClean(

p, Aig_ManObjNumMax(

p->pManFraig) + Aig_ManNodeNum(

p->pManAig) );

525

526

528 {

530 continue;

531 Fra_ObjSetSatNum( pObj, pCnf->

pVarNums[pObj->

Id] );

532 Fra_ObjSetFaninVec( pObj, (

Vec_Ptr_t *)1 );

533 }

535

536

537 if (

p->pPars->fUse1Hot )

539

540

541

542

543 if ( pPars->fVerbose )

544 {

545 printf( "%3d : C = %6d. Cl = %6d. L = %6d. LR = %6d. ",

546 nIter, Vec_PtrSize(

p->pCla->vClasses1), Vec_PtrSize(

p->pCla->vClasses),

548 if (

p->pCla->vImps )

549 printf(

"I = %6d. ", Vec_IntSize(

p->pCla->vImps) );

550 if (

p->pPars->fUse1Hot )

552 printf(

"NR = %6d. ", Aig_ManNodeNum(

p->pManFraig) );

553

554 }

555

556

557 p->nSatCallsRecent = 0;

558 p->nSatCallsSkipped = 0;

559clk2 = Abc_Clock();

560 if (

p->pPars->fUse1Hot )

563 if ( pPars->fVerbose )

564 {

565 ABC_PRT(

"T", Abc_Clock() - clk3 );

566 }

567

568

569

571

574

575 assert(

p->vTimeouts == NULL );

577 printf( "Fra_FraigInduction(): SAT solver timed out!\n" );

578

579

580 if (

p->pCla->fRefinement &&

582 nImpsOld == (

p->pCla->vImps? Vec_IntSize(

p->pCla->vImps) : 0) &&

584 {

585 printf( "Fra_FraigInduction(): Internal error. The result may not verify.\n" );

586 break;

587 }

588 }

589

590

591

592

593

594

595

596

597

598

599

600

601

602

603

604clk2 = Abc_Clock();

606 {

610 printf( "Care one-hotness clauses will be written into file \"%s\".\n", pFileName );

615 }

616 else

617 {

618

622 }

623

624

625

626

628

629

630

631

632

633p->timeTrav += Abc_Clock() - clk2;

634p->timeTotal = Abc_Clock() - clk;

635

637 p->nNodesEnd = Aig_ManNodeNum(pManAigNew);

638 p->nRegsEnd = Aig_ManRegNum(pManAigNew);

639

640finish:

642

643

644

645

647 return pManAigNew;

648}

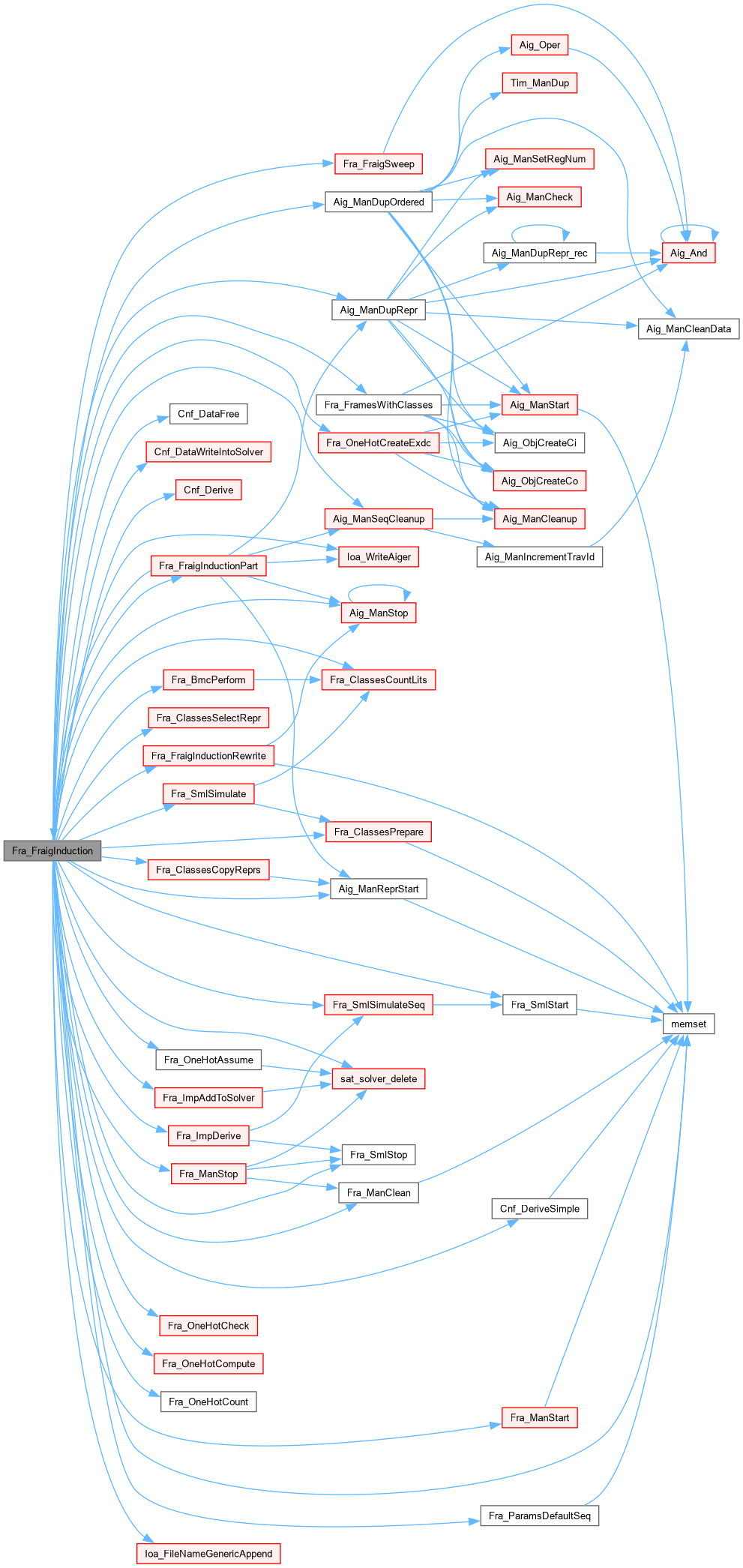

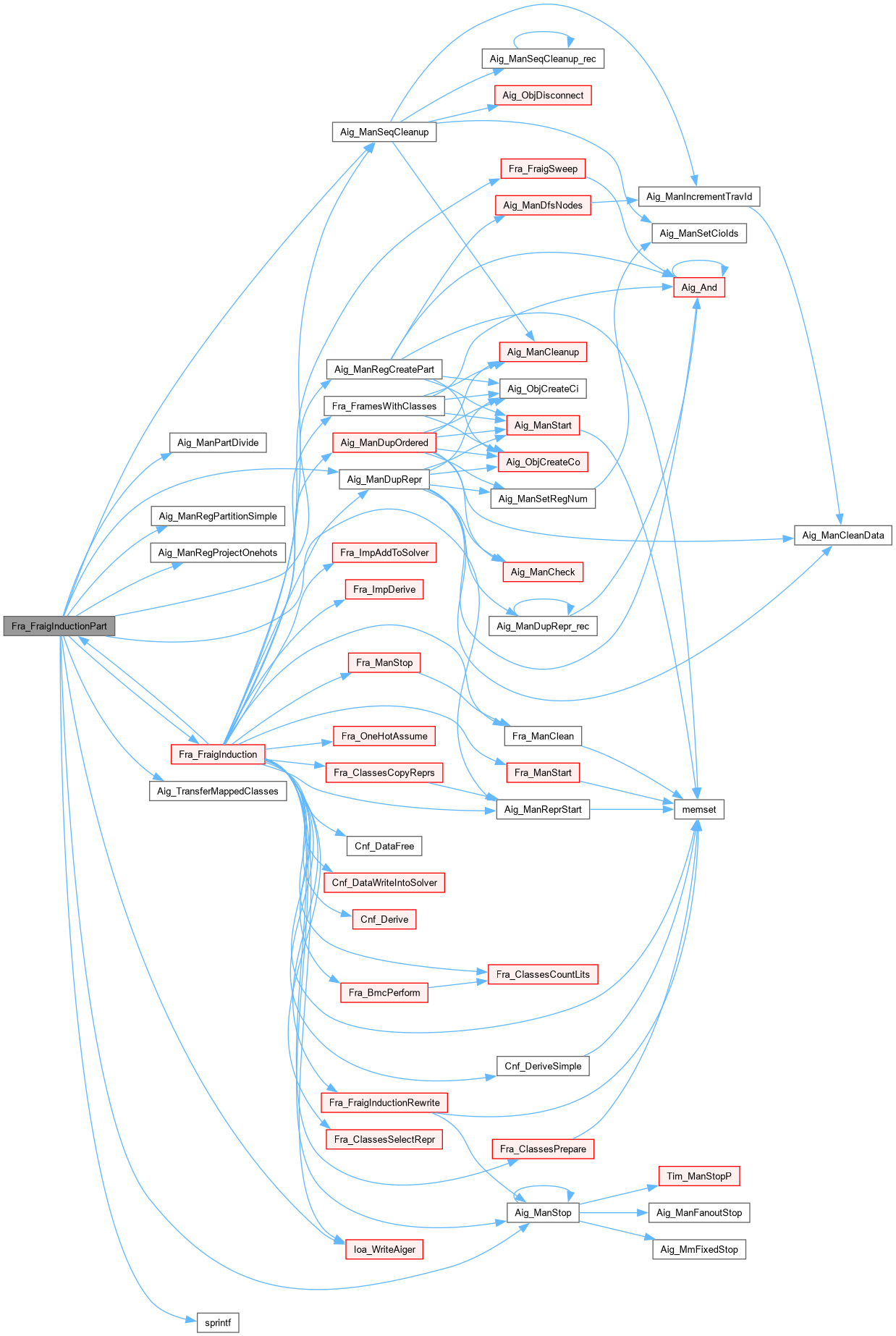

Aig_Man_t * Aig_ManDupRepr(Aig_Man_t *p, int fOrdered)

Aig_Man_t * Aig_ManDupOrdered(Aig_Man_t *p)

int Aig_ManSeqCleanup(Aig_Man_t *p)

void Aig_ManReprStart(Aig_Man_t *p, int nIdMax)

DECLARATIONS ///.

#define Aig_ManForEachObj(p, pObj, i)

void Aig_ManStop(Aig_Man_t *p)

struct Aig_Obj_t_ Aig_Obj_t

typedefABC_NAMESPACE_HEADER_START struct Aig_Man_t_ Aig_Man_t

INCLUDES ///.

Cnf_Dat_t * Cnf_DeriveSimple(Aig_Man_t *p, int nOutputs)

Cnf_Dat_t * Cnf_Derive(Aig_Man_t *pAig, int nOutputs)

struct Cnf_Dat_t_ Cnf_Dat_t

void Cnf_DataFree(Cnf_Dat_t *p)

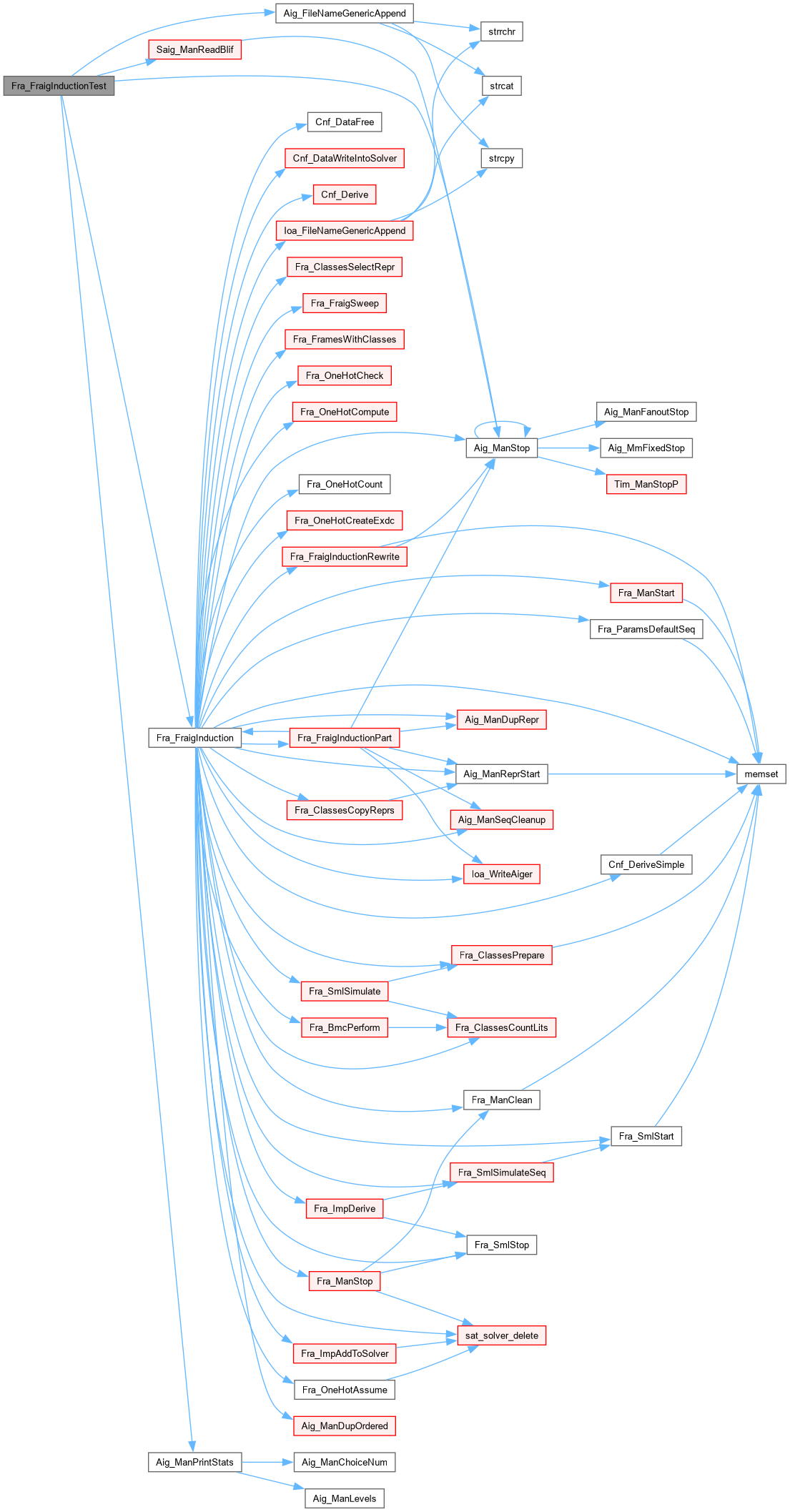

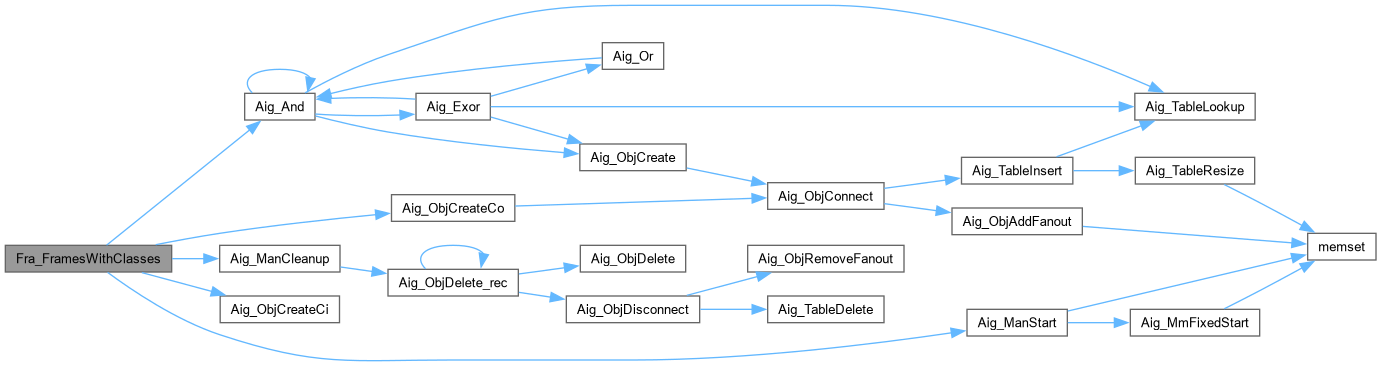

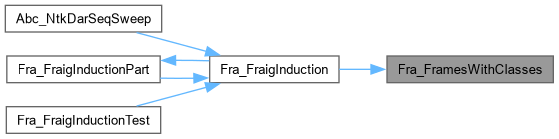

Aig_Man_t * Fra_FramesWithClasses(Fra_Man_t *p)

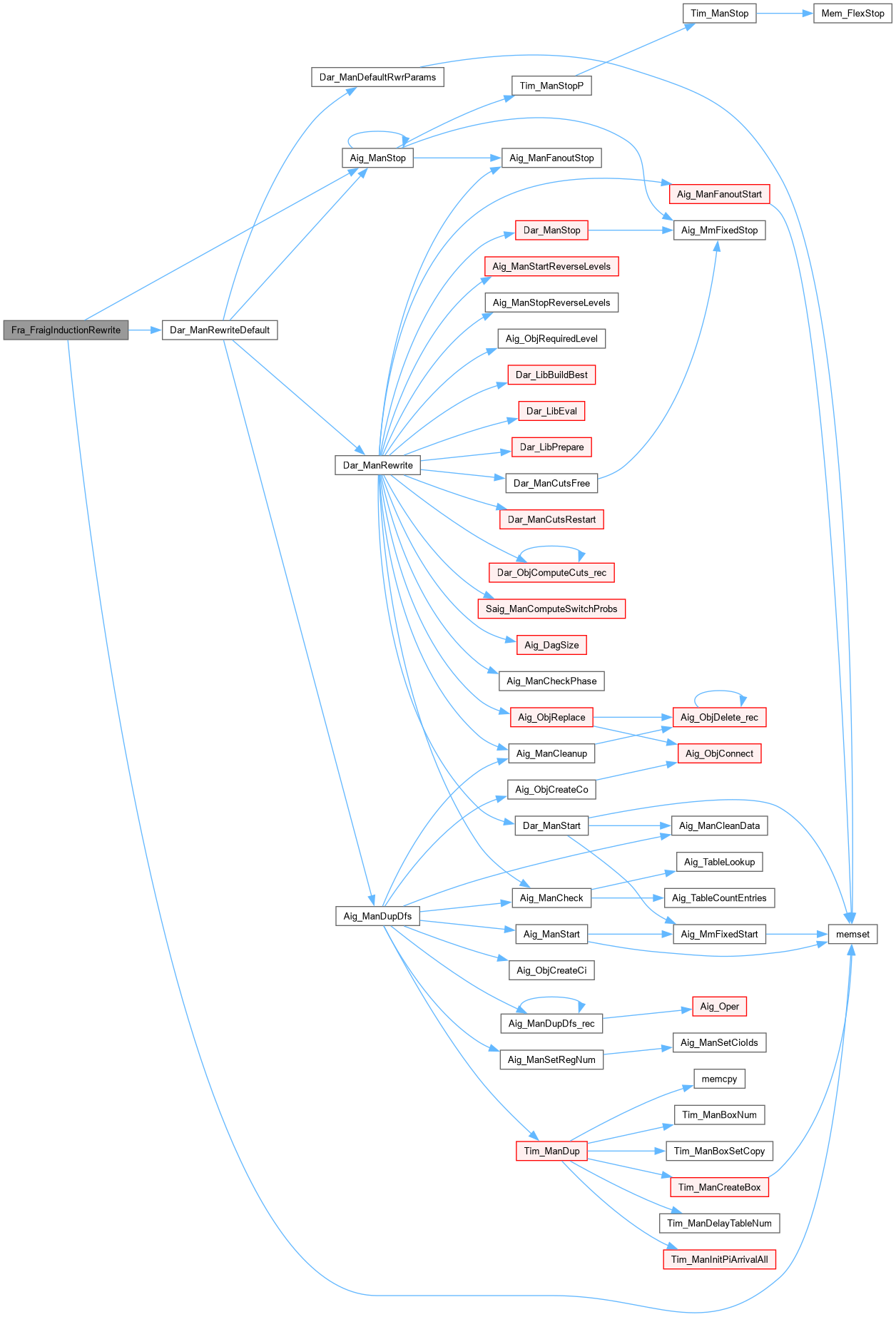

ABC_NAMESPACE_IMPL_START void Fra_FraigInductionRewrite(Fra_Man_t *p)

DECLARATIONS ///.

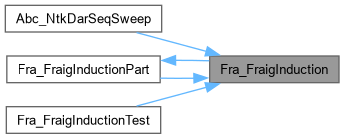

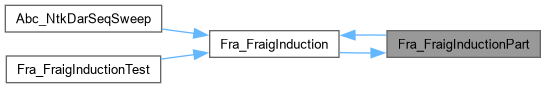

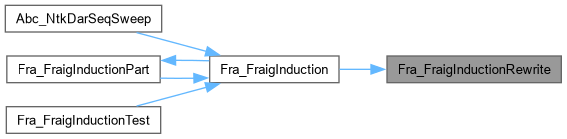

Aig_Man_t * Fra_FraigInductionPart(Aig_Man_t *pAig, Fra_Ssw_t *pPars)

void Fra_ClassesCopyReprs(Fra_Cla_t *p, Vec_Ptr_t *vFailed)

void Fra_FraigSweep(Fra_Man_t *pManAig)

typedefABC_NAMESPACE_HEADER_START struct Fra_Par_t_ Fra_Par_t

INCLUDES ///.

void Fra_SmlSimulate(Fra_Man_t *p, int fInit)

Vec_Int_t * Fra_OneHotCompute(Fra_Man_t *p, Fra_Sml_t *pSim)

void Fra_OneHotAssume(Fra_Man_t *p, Vec_Int_t *vOneHots)

void Fra_SmlStop(Fra_Sml_t *p)

void Fra_ClassesPrepare(Fra_Cla_t *p, int fLatchCorr, int nMaxLevs)

struct Fra_Man_t_ Fra_Man_t

Fra_Sml_t * Fra_SmlStart(Aig_Man_t *pAig, int nPref, int nFrames, int nWordsFrame)

Aig_Man_t * Fra_OneHotCreateExdc(Fra_Man_t *p, Vec_Int_t *vOneHots)

Vec_Int_t * Fra_ImpDerive(Fra_Man_t *p, int nImpMaxLimit, int nImpUseLimit, int fLatchCorr)

void Fra_ManStop(Fra_Man_t *p)

int Fra_ClassesCountLits(Fra_Cla_t *p)

Fra_Man_t * Fra_ManStart(Aig_Man_t *pManAig, Fra_Par_t *pParams)

void Fra_ImpAddToSolver(Fra_Man_t *p, Vec_Int_t *vImps, int *pSatVarNums)

void Fra_ClassesSelectRepr(Fra_Cla_t *p)

void Fra_OneHotCheck(Fra_Man_t *p, Vec_Int_t *vOneHots)

Fra_Sml_t * Fra_SmlSimulateSeq(Aig_Man_t *pAig, int nPref, int nFrames, int nWords, int fCheckMiter)

void Fra_ManClean(Fra_Man_t *p, int nNodesMax)

int Fra_OneHotCount(Fra_Man_t *p, Vec_Int_t *vOneHots)

void Fra_BmcPerform(Fra_Man_t *p, int nPref, int nDepth)

void Fra_ParamsDefaultSeq(Fra_Par_t *pParams)

void Ioa_WriteAiger(Aig_Man_t *pMan, char *pFileName, int fWriteSymbols, int fCompact)

char * Ioa_FileNameGenericAppend(char *pBase, char *pSuffix)

void * Cnf_DataWriteIntoSolver(Cnf_Dat_t *p, int nFrames, int fInit)

void sat_solver_delete(sat_solver *s)

typedefABC_NAMESPACE_HEADER_START struct Vec_Ptr_t_ Vec_Ptr_t

INCLUDES ///.