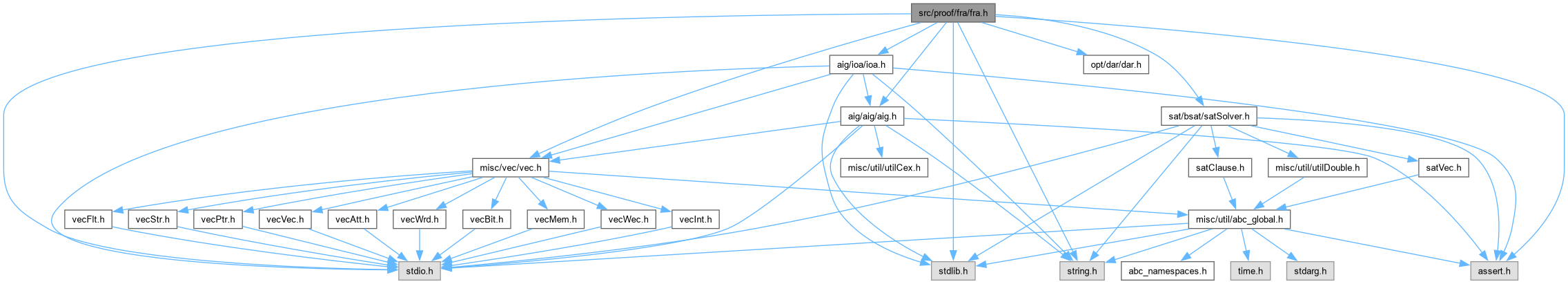

#include <stdio.h>#include <stdlib.h>#include <string.h>#include <assert.h>#include "misc/vec/vec.h"#include "aig/aig/aig.h"#include "opt/dar/dar.h"#include "sat/bsat/satSolver.h"#include "aig/ioa/ioa.h"

Go to the source code of this file.

Classes | |

| struct | Fra_Par_t_ |

| struct | Fra_Ssw_t_ |

| struct | Fra_Sec_t_ |

| struct | Fra_Cla_t_ |

| struct | Fra_Sml_t_ |

| struct | Fra_Man_t_ |

Typedefs | |

| typedef typedefABC_NAMESPACE_HEADER_START struct Fra_Par_t_ | Fra_Par_t |

| INCLUDES ///. | |

| typedef struct Fra_Ssw_t_ | Fra_Ssw_t |

| typedef struct Fra_Sec_t_ | Fra_Sec_t |

| typedef struct Fra_Man_t_ | Fra_Man_t |

| typedef struct Fra_Cla_t_ | Fra_Cla_t |

| typedef struct Fra_Sml_t_ | Fra_Sml_t |

| typedef struct Fra_Bmc_t_ | Fra_Bmc_t |

| typedef struct Fra_Bmc_t_ Fra_Bmc_t |

| typedef struct Fra_Cla_t_ Fra_Cla_t |

| typedef struct Fra_Man_t_ Fra_Man_t |

| typedef typedefABC_NAMESPACE_HEADER_START struct Fra_Par_t_ Fra_Par_t |

INCLUDES ///.

CFile****************************************************************

FileName [fra.h]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [[New FRAIG package.]

Synopsis [External declarations.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] PARAMETERS /// BASIC TYPES ///

| typedef struct Fra_Sec_t_ Fra_Sec_t |

| typedef struct Fra_Sml_t_ Fra_Sml_t |

| typedef struct Fra_Ssw_t_ Fra_Ssw_t |

|

extern |

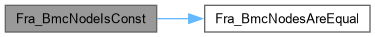

Function*************************************************************

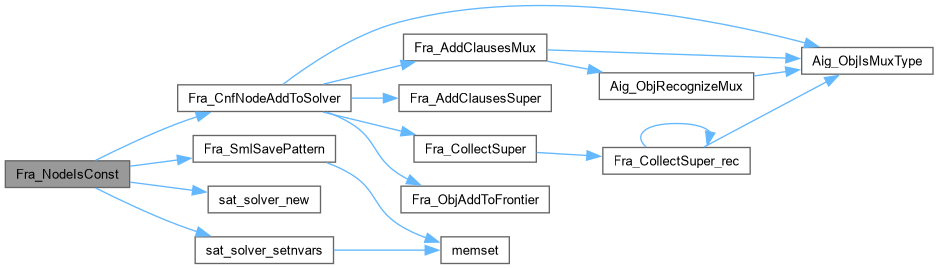

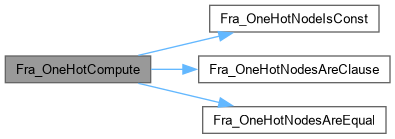

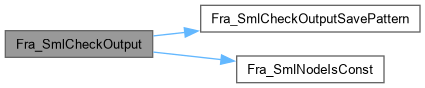

Synopsis [Returns 1 if the node is costant.]

Description []

SideEffects []

SeeAlso []

Definition at line 103 of file fraBmc.c.

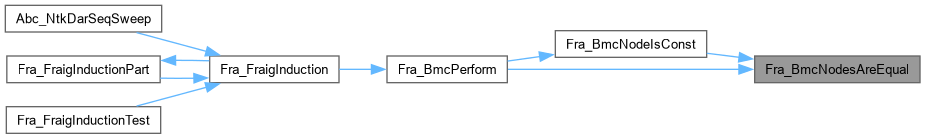

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Returns 1 if the nodes are equivalent.]

Description []

SideEffects []

SeeAlso []

Definition at line 72 of file fraBmc.c.

|

extern |

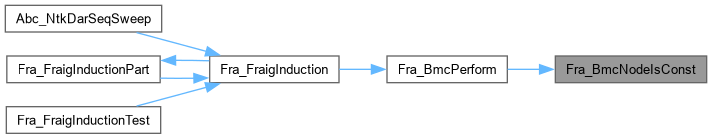

Function*************************************************************

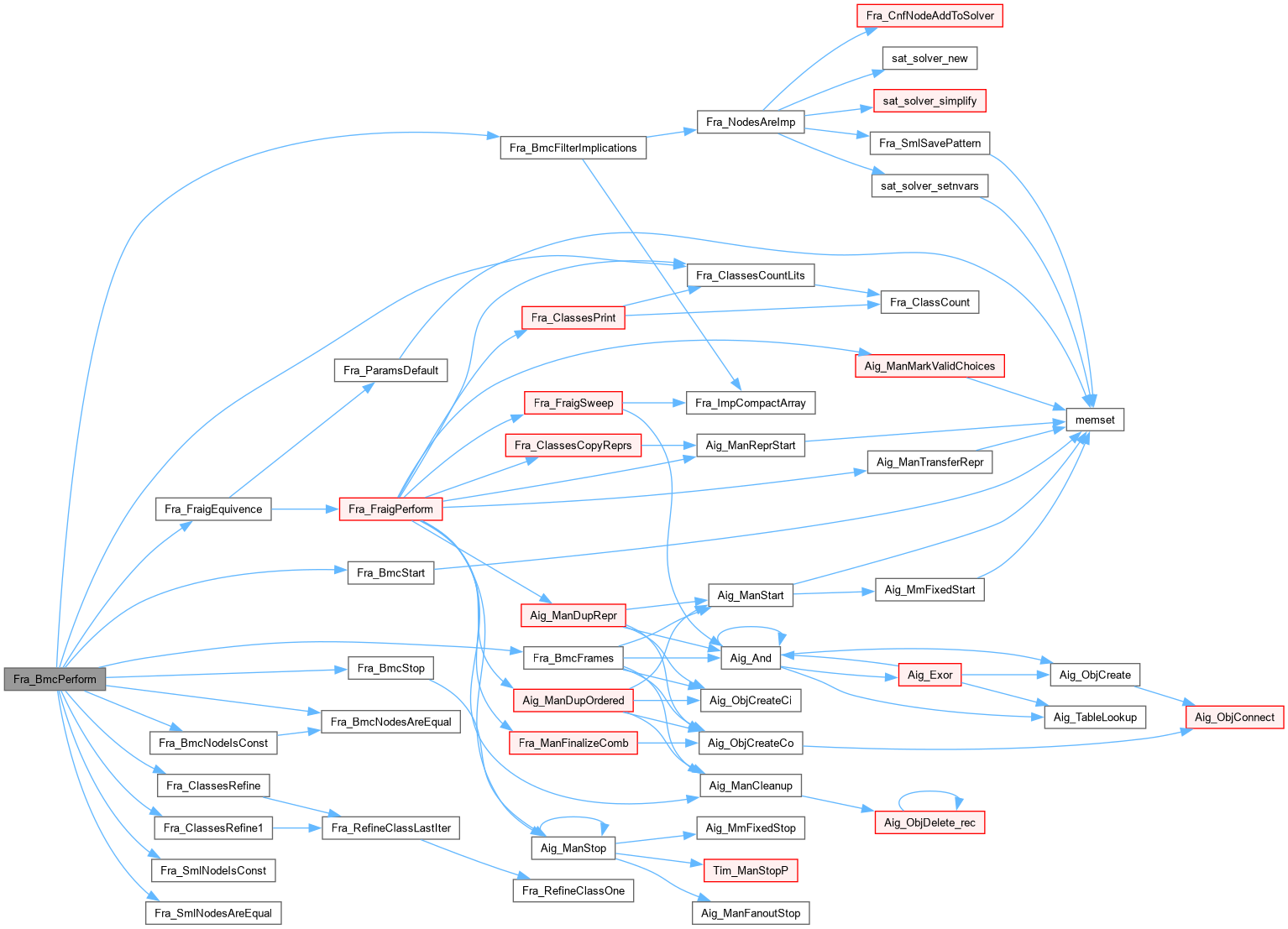

Synopsis [Performs BMC for the given AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 311 of file fraBmc.c.

|

extern |

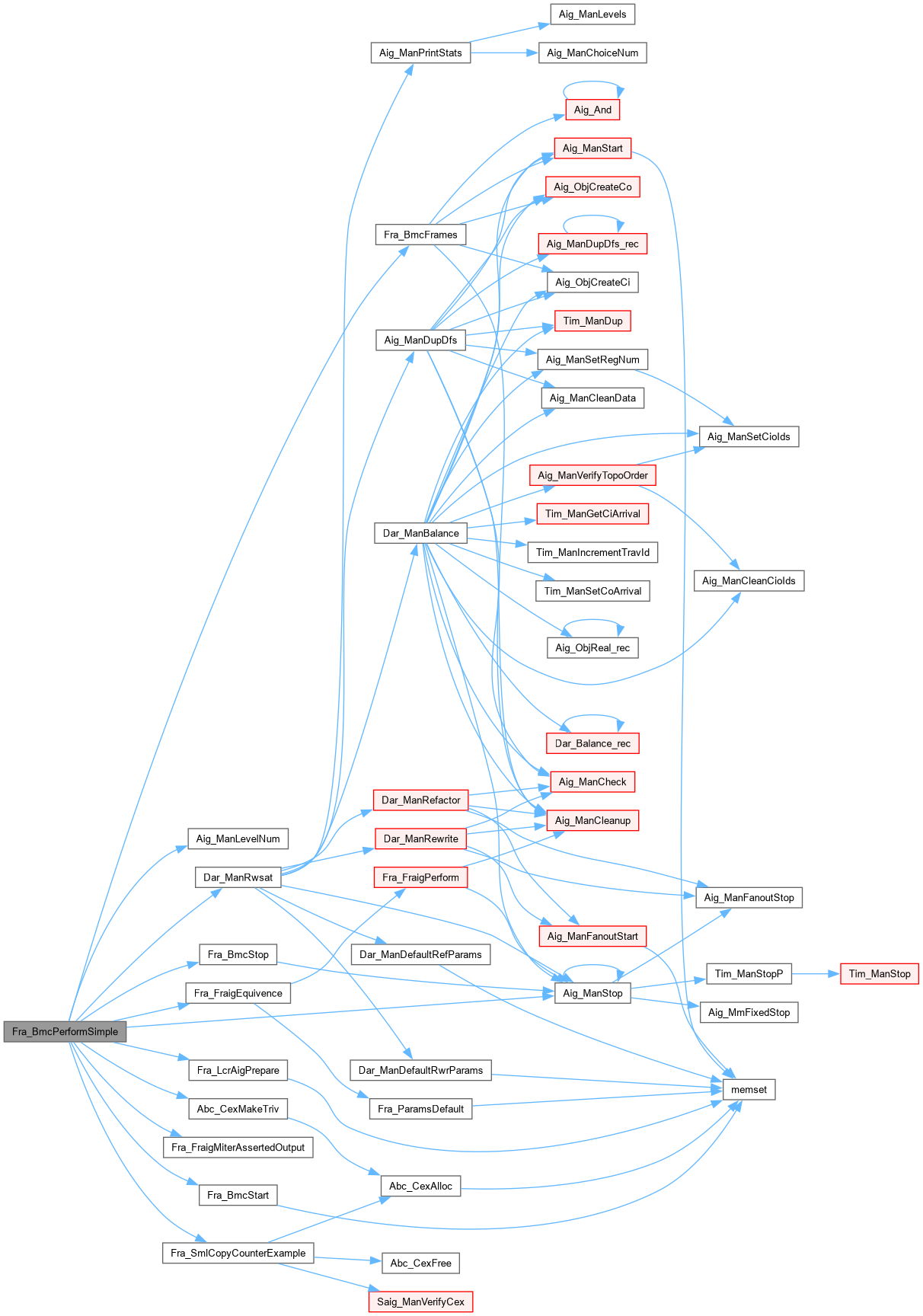

Function*************************************************************

Synopsis [Performs BMC for the given AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 383 of file fraBmc.c.

|

extern |

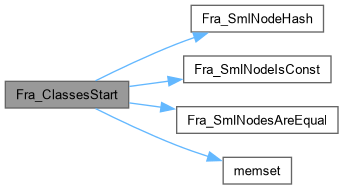

Function*************************************************************

Synopsis [Starts representation of equivalence classes.]

Description []

SideEffects []

SeeAlso []

Definition at line 114 of file fraClass.c.

|

extern |

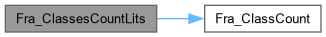

Function*************************************************************

Synopsis [Count the number of literals.]

Description []

SideEffects []

SeeAlso []

Definition at line 164 of file fraClass.c.

|

extern |

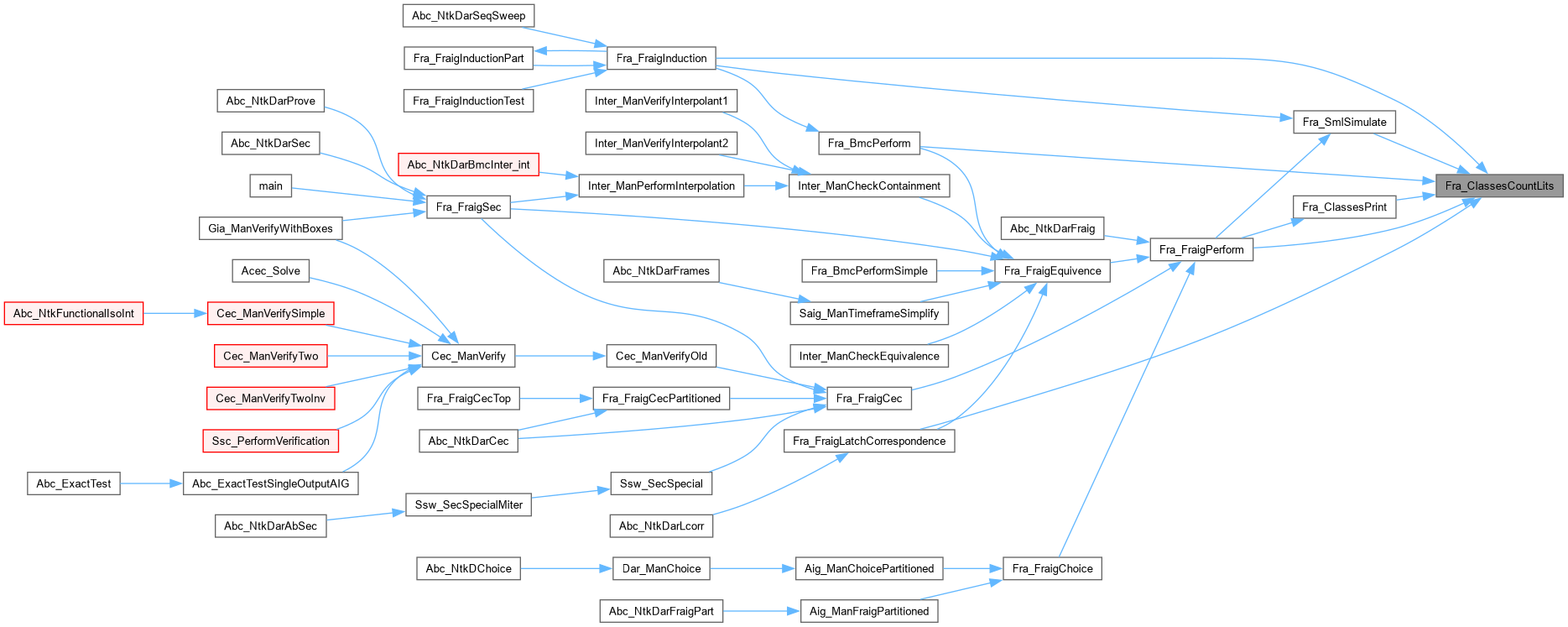

Function*************************************************************

Synopsis [Count the number of pairs.]

Description []

SideEffects []

SeeAlso []

Definition at line 189 of file fraClass.c.

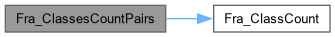

Function*************************************************************

Synopsis [Derives AIG for the partitioned problem.]

Description []

SideEffects []

SeeAlso []

Definition at line 796 of file fraClass.c.

|

extern |

Function*************************************************************

Synopsis [Creates latch correspondence classes.]

Description []

SideEffects []

SeeAlso []

Definition at line 615 of file fraClass.c.

|

extern |

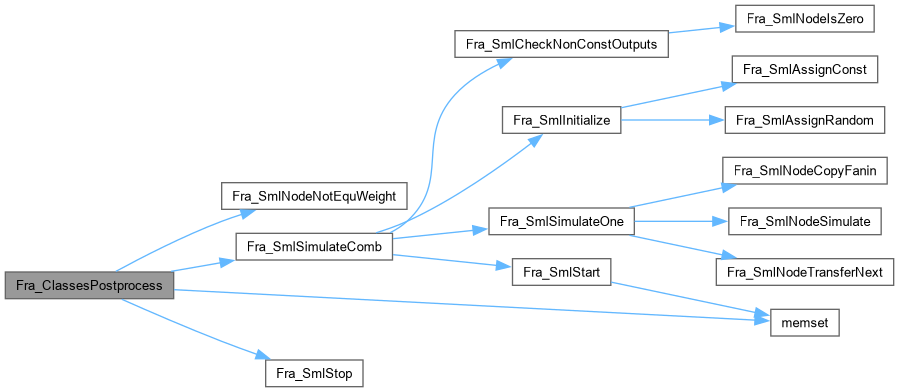

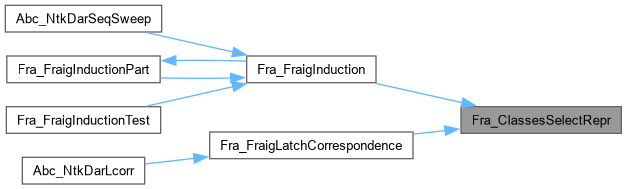

Function*************************************************************

Synopsis [Postprocesses the classes by removing half of the less useful.]

Description []

SideEffects []

SeeAlso []

Definition at line 641 of file fraClass.c.

|

extern |

Function*************************************************************

Synopsis [Creates initial simulation classes.]

Description [Assumes that simulation info is assigned.]

SideEffects []

SeeAlso []

Definition at line 276 of file fraClass.c.

|

extern |

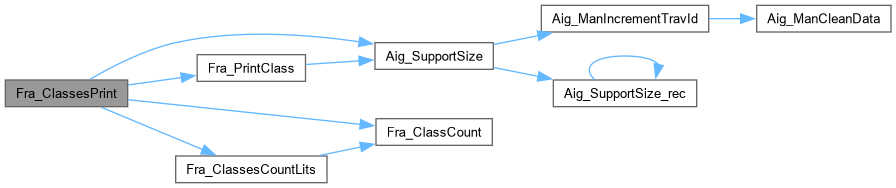

Function*************************************************************

Synopsis [Prints simulation classes.]

Description []

SideEffects []

SeeAlso []

Definition at line 236 of file fraClass.c.

|

extern |

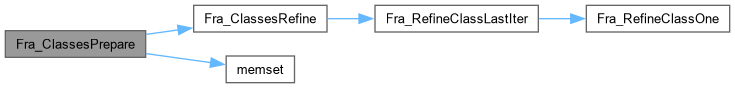

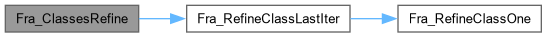

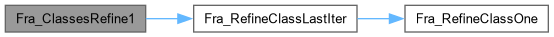

Function*************************************************************

Synopsis [Refines the classes after simulation.]

Description [Assumes that simulation info is assigned. Returns the number of classes refined.]

SideEffects []

SeeAlso []

Definition at line 493 of file fraClass.c.

|

extern |

Function*************************************************************

Synopsis [Refines constant 1 equivalence class.]

Description []

SideEffects []

SeeAlso []

Definition at line 527 of file fraClass.c.

|

extern |

Function*************************************************************

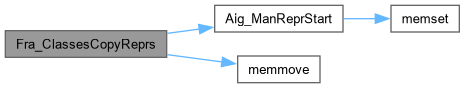

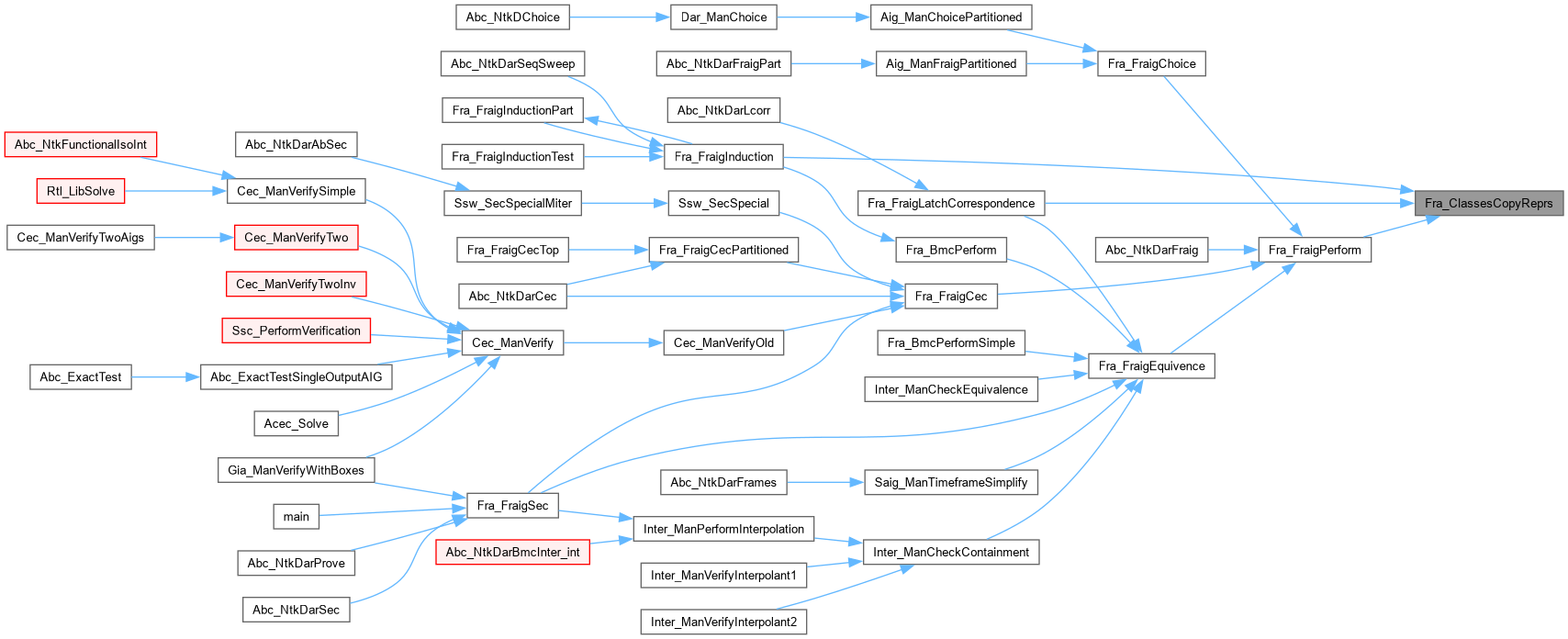

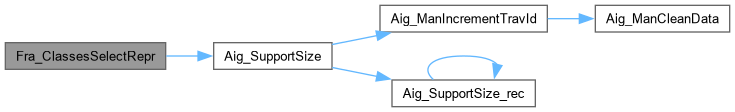

Synopsis [Postprocesses the classes by selecting representative lowest in top order.]

Description []

SideEffects []

SeeAlso []

Definition at line 706 of file fraClass.c.

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Starts representation of equivalence classes.]

Description []

SideEffects []

SeeAlso []

Definition at line 60 of file fraClass.c.

|

extern |

Function*************************************************************

Synopsis [Stop representation of equivalence classes.]

Description []

SideEffects []

SeeAlso []

Definition at line 90 of file fraClass.c.

|

extern |

Function*************************************************************

Synopsis [Starts representation of equivalence classes with one class.]

Description []

SideEffects []

SeeAlso []

Definition at line 590 of file fraClass.c.

Function*************************************************************

Synopsis [Updates the solver clause database.]

Description []

SideEffects []

SeeAlso []

Definition at line 238 of file fraCnf.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 320 of file fraCec.c.

|

extern |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 451 of file fraCec.c.

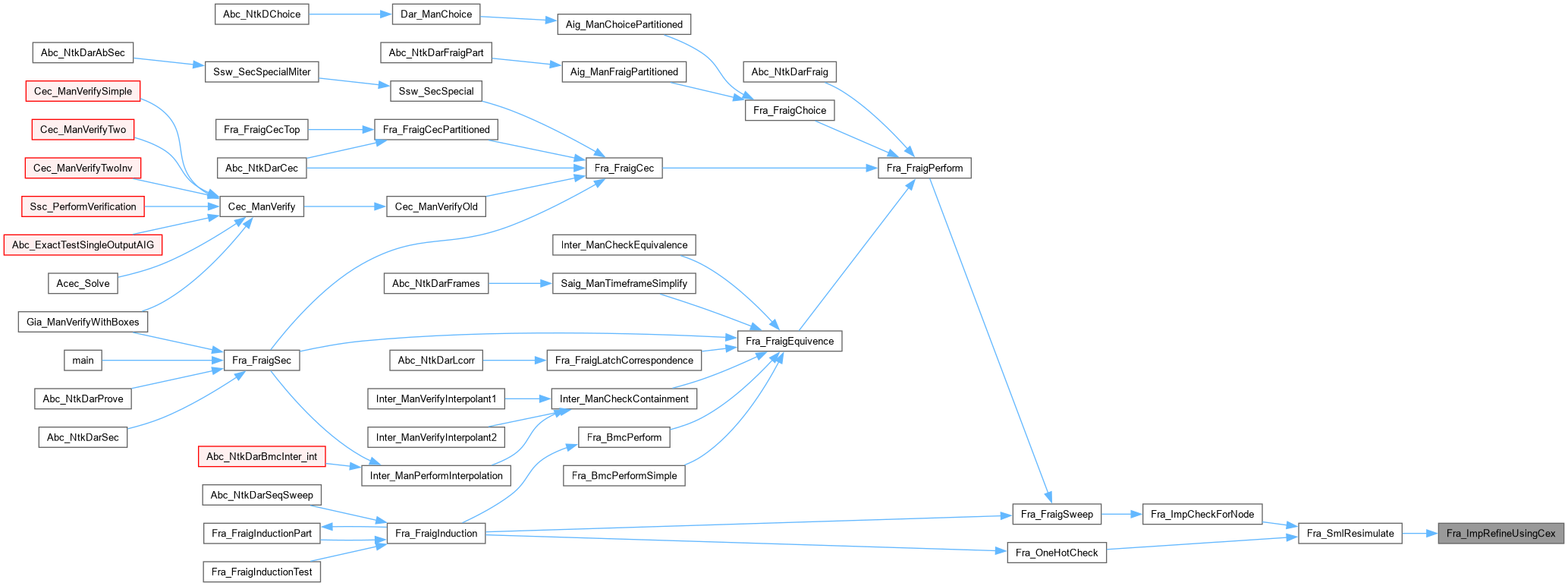

Function*************************************************************

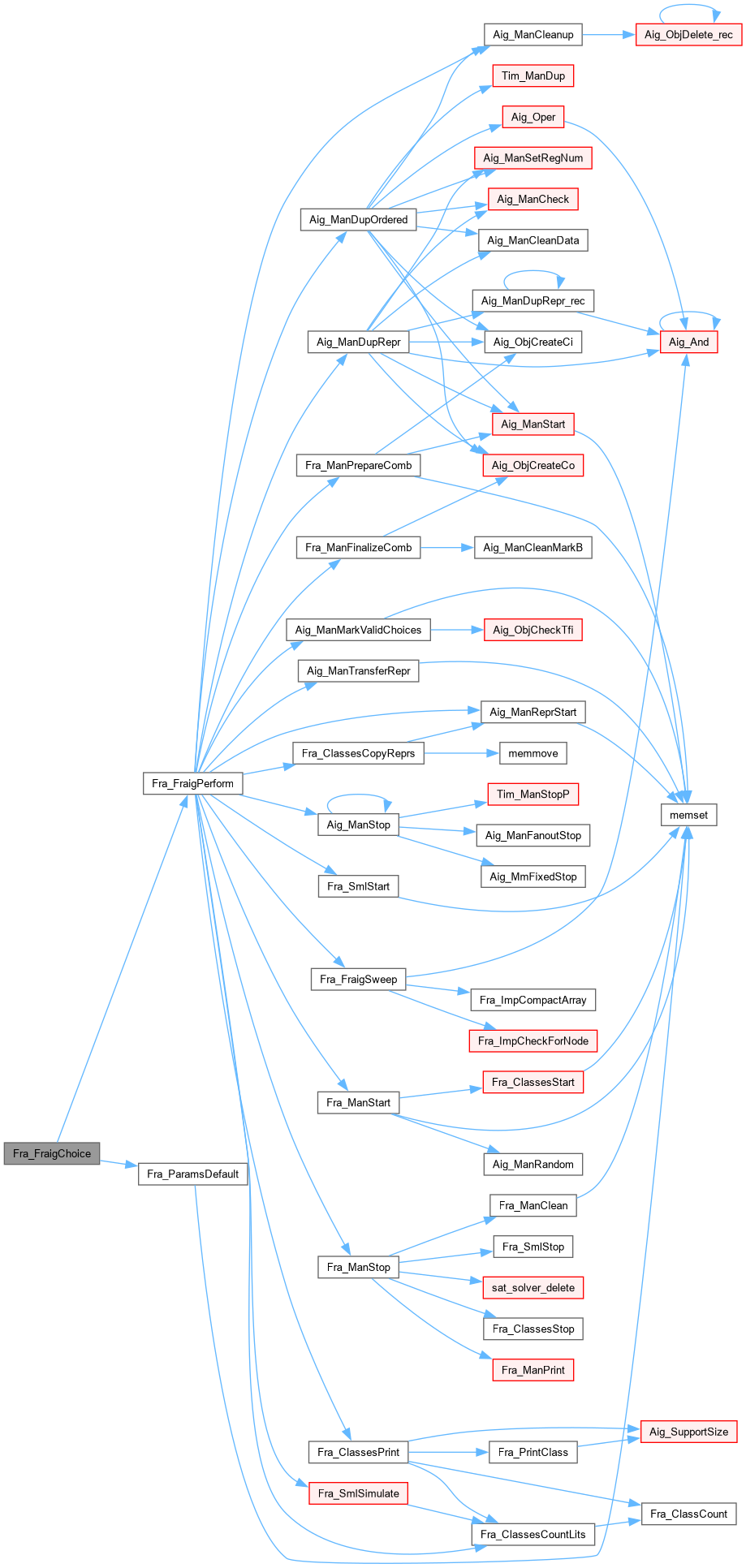

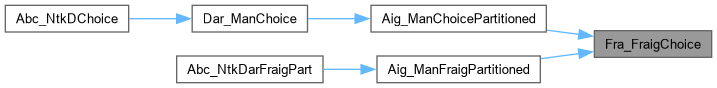

Synopsis [Performs choicing of the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 442 of file fraCore.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 468 of file fraCore.c.

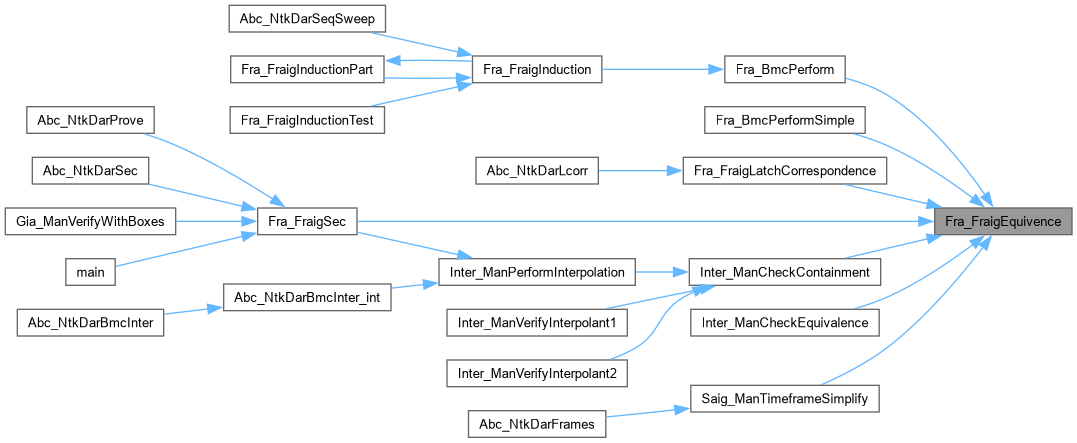

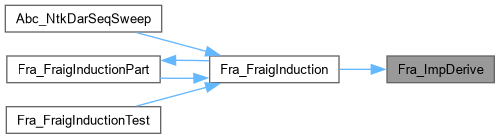

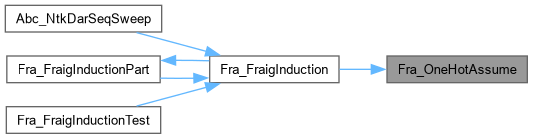

Function*************************************************************

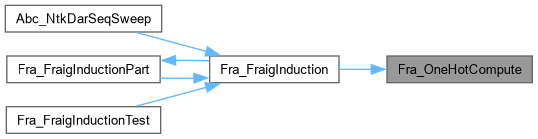

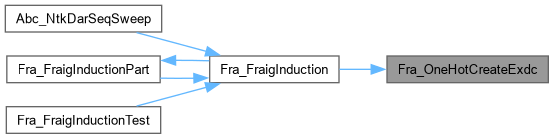

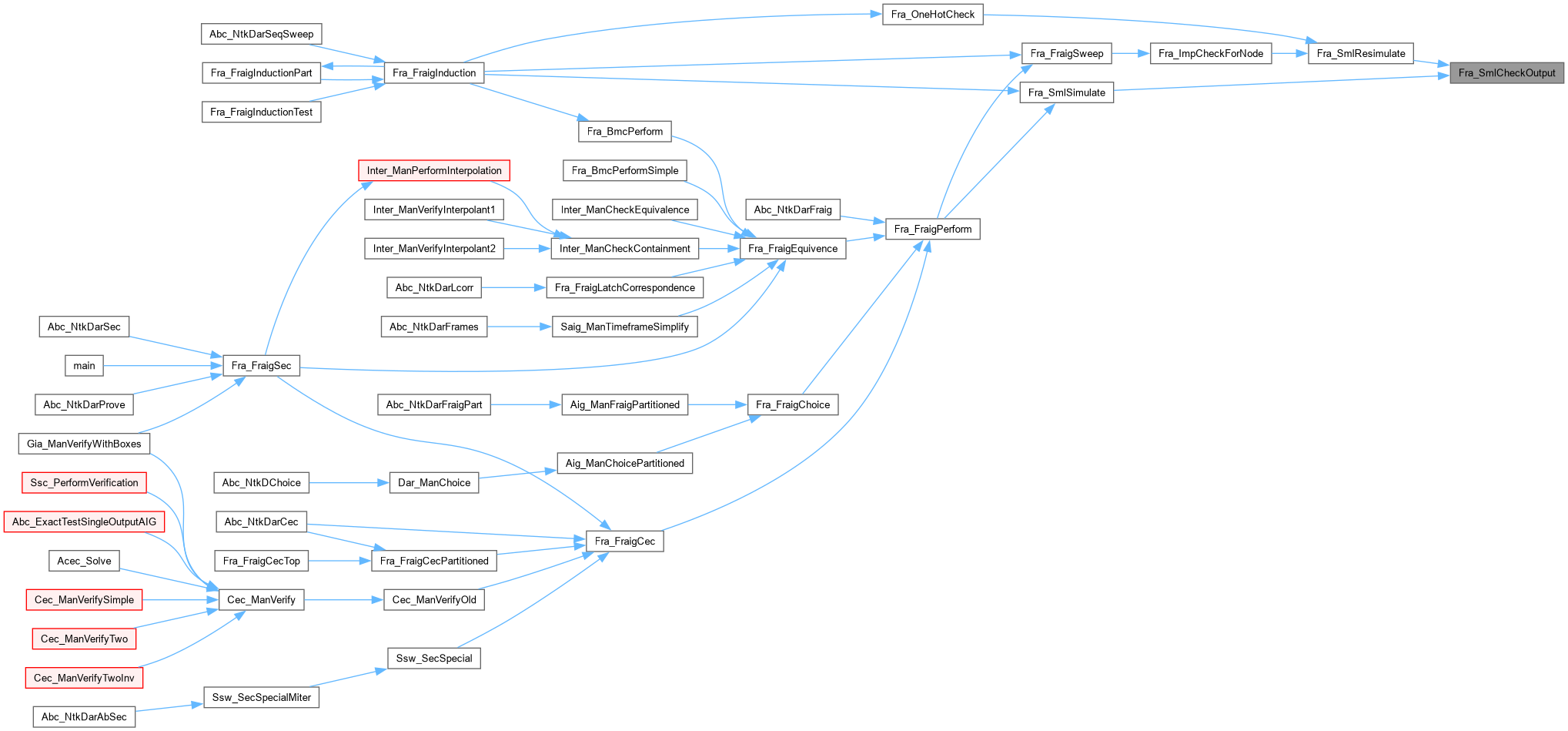

Synopsis [Performs sequential SAT sweeping.]

Description []

SideEffects []

SeeAlso []

Definition at line 344 of file fraInd.c.

|

extern |

Function*************************************************************

Synopsis [Performs choicing of the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 531 of file fraLcr.c.

|

extern |

Function*************************************************************

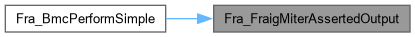

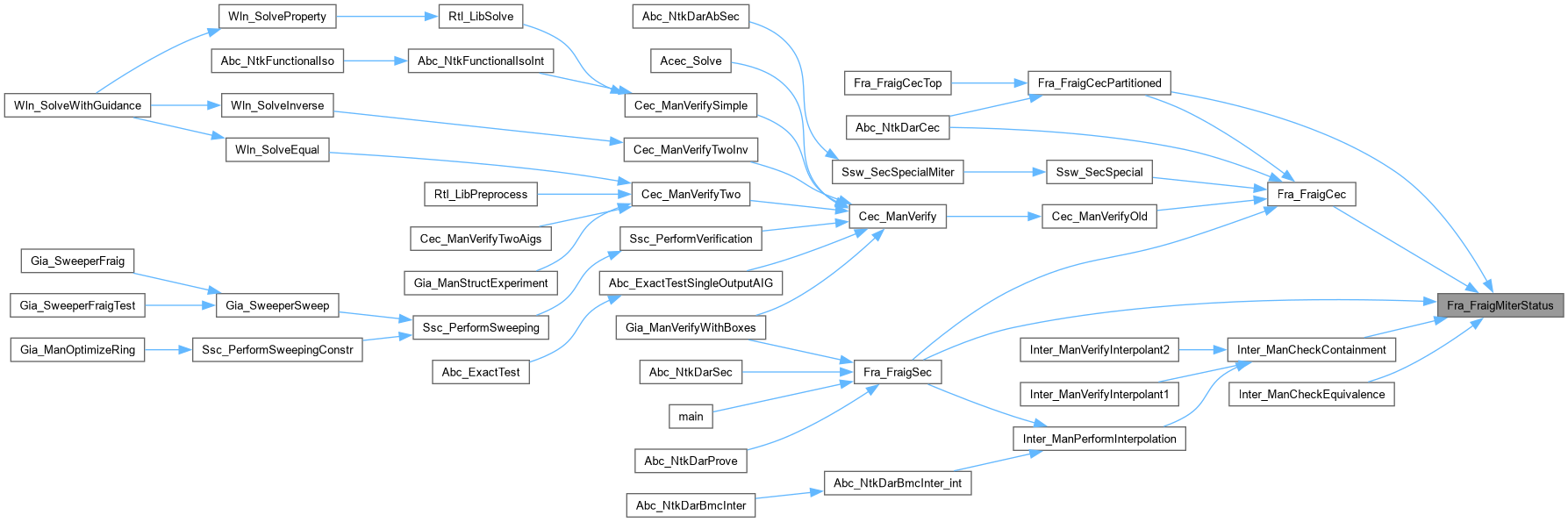

Synopsis [Reports the status of the miter.]

Description []

SideEffects []

SeeAlso []

Definition at line 125 of file fraCore.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fraCore.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis []

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Reports the status of the miter.]

Description []

SideEffects []

SeeAlso []

Definition at line 62 of file fraCore.c.

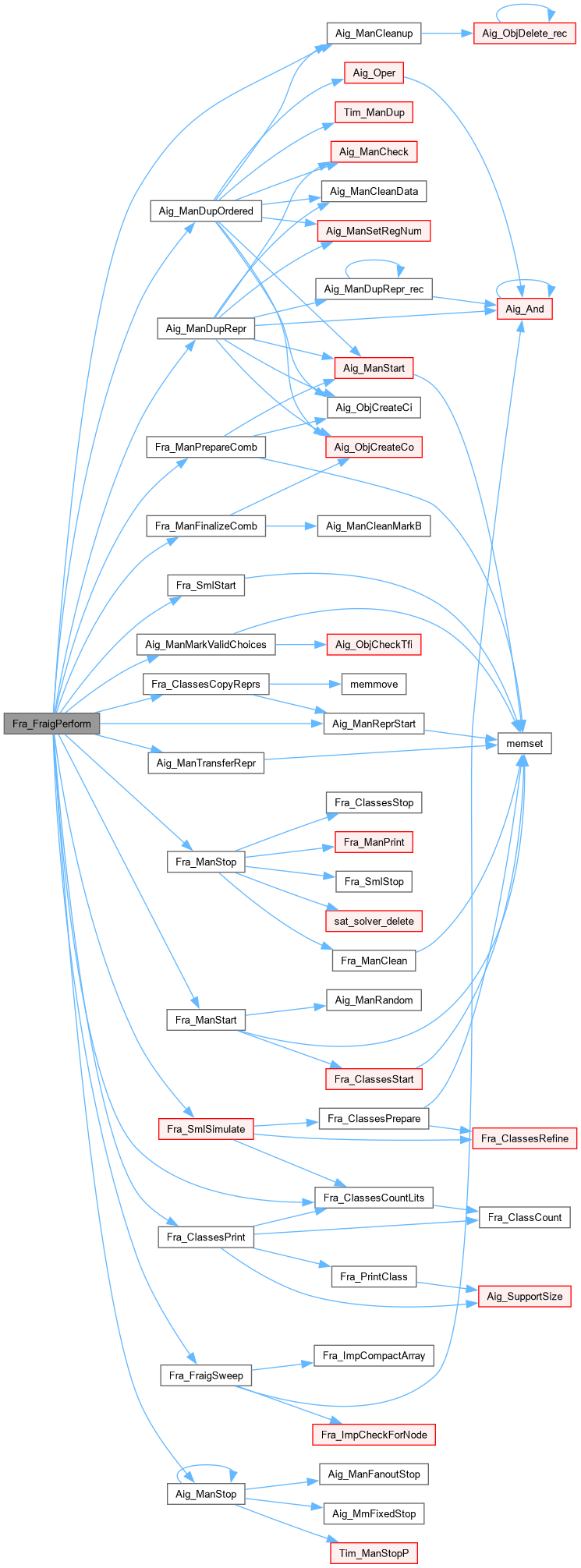

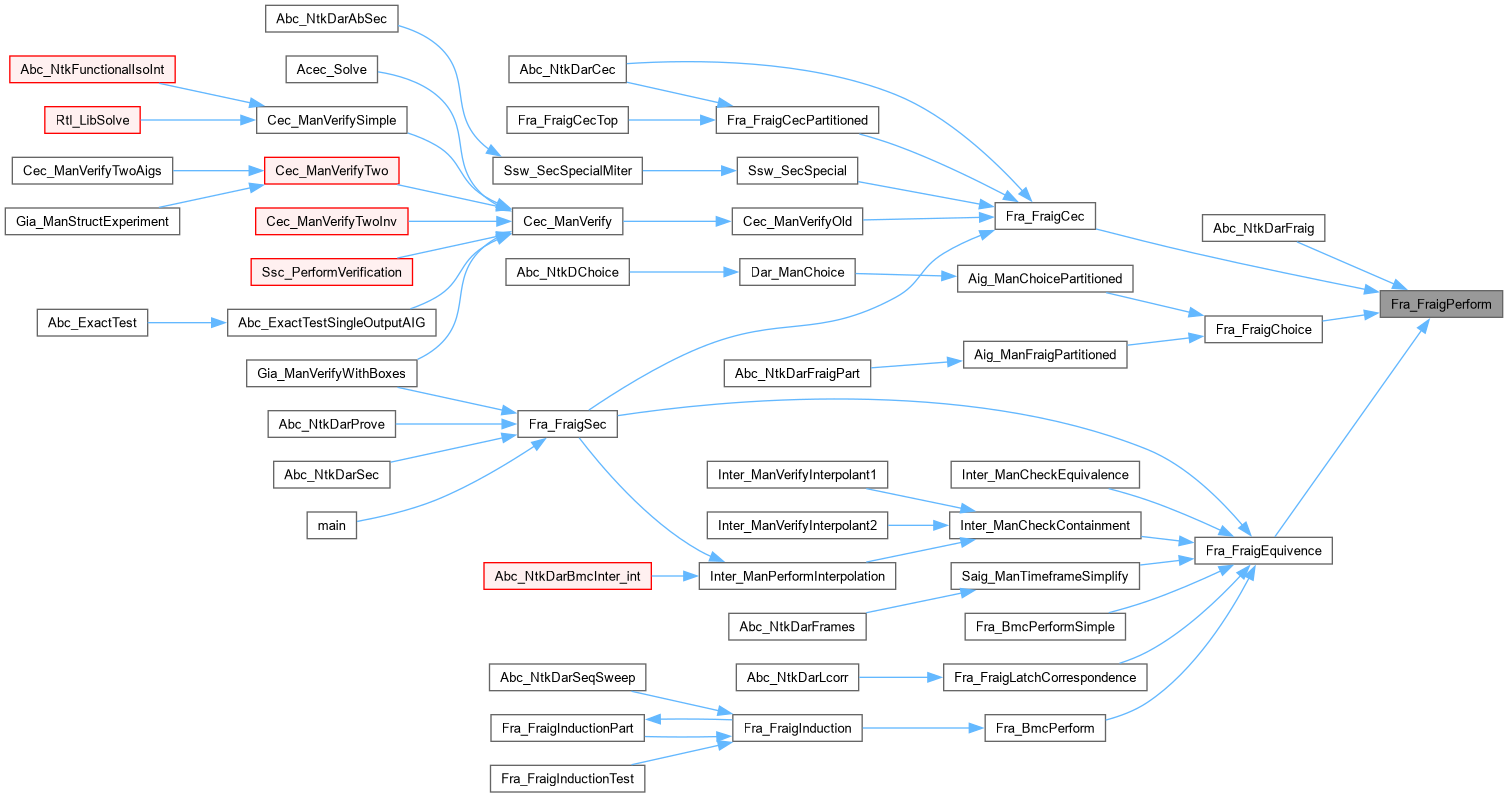

Function*************************************************************

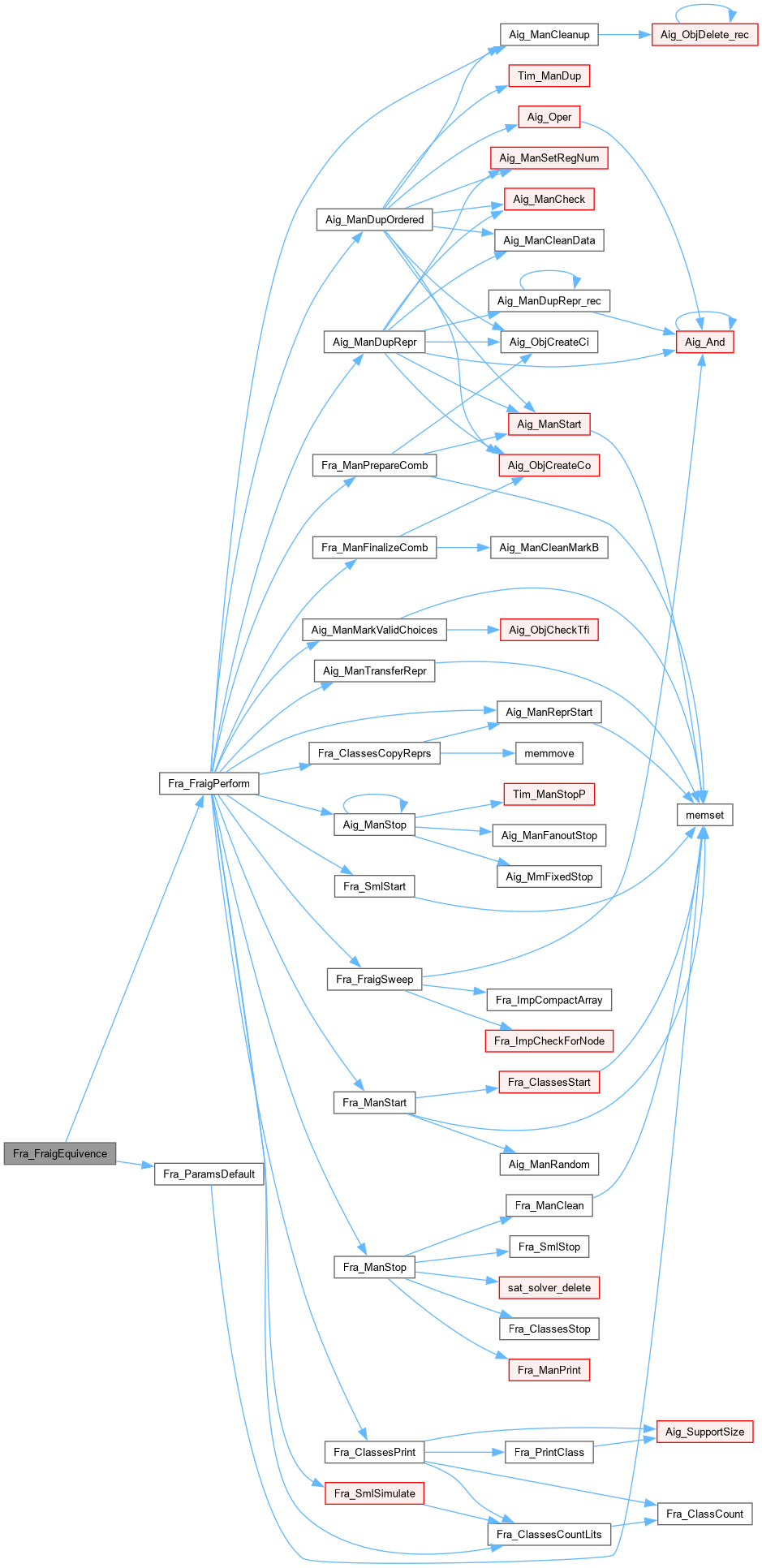

Synopsis [Performs fraiging of the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 375 of file fraCore.c.

|

extern |

ITERATORS ///.

FUNCTION DECLARATIONS ///

ITERATORS ///.

CFile****************************************************************

FileName [fraCec.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis [CEC engined based on fraiging.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 47 of file fraCec.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 118 of file fraSec.c.

|

extern |

Function*************************************************************

Synopsis [Performs fraiging for the internal nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 310 of file fraCore.c.

Function*************************************************************

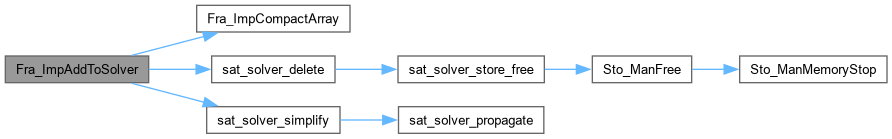

Synopsis [Add implication clauses to the SAT solver.]

Description [Note that implications should be checked in the first frame!]

SideEffects []

SeeAlso []

Definition at line 428 of file fraImp.c.

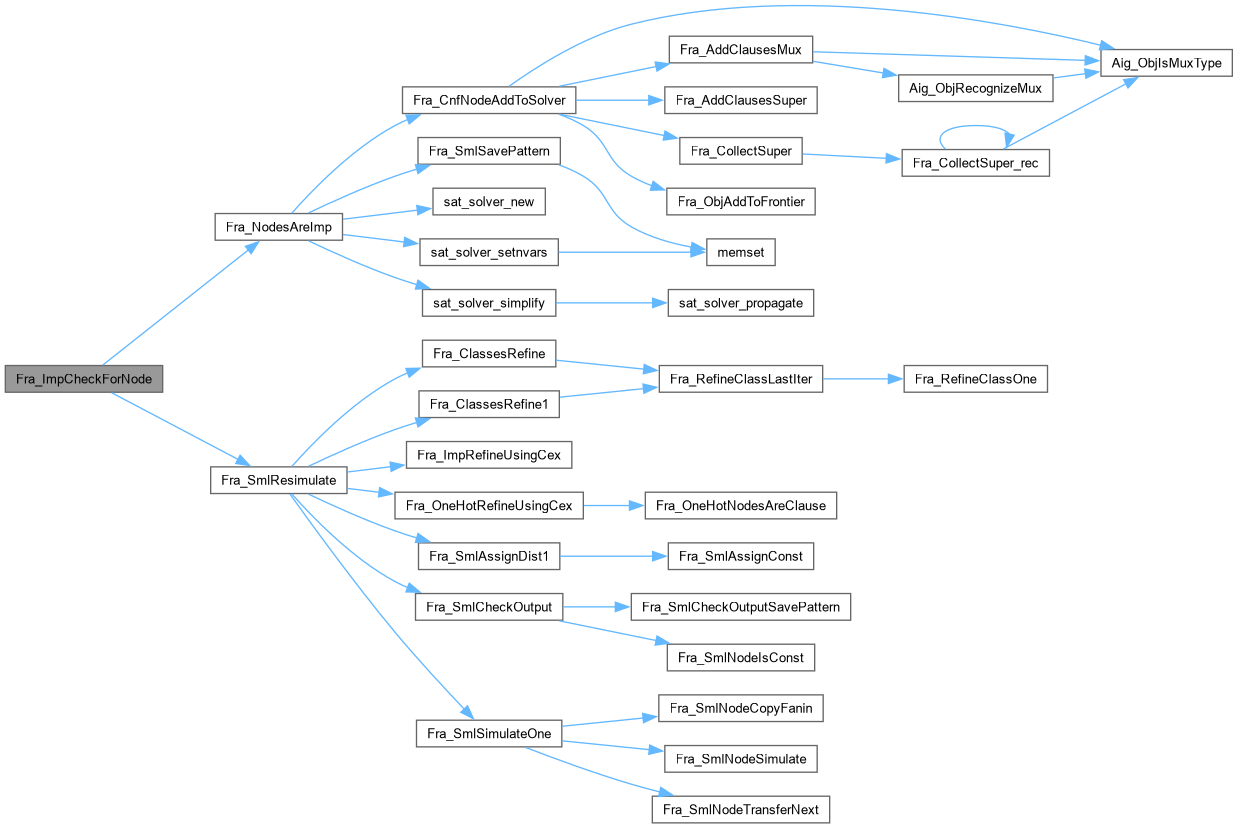

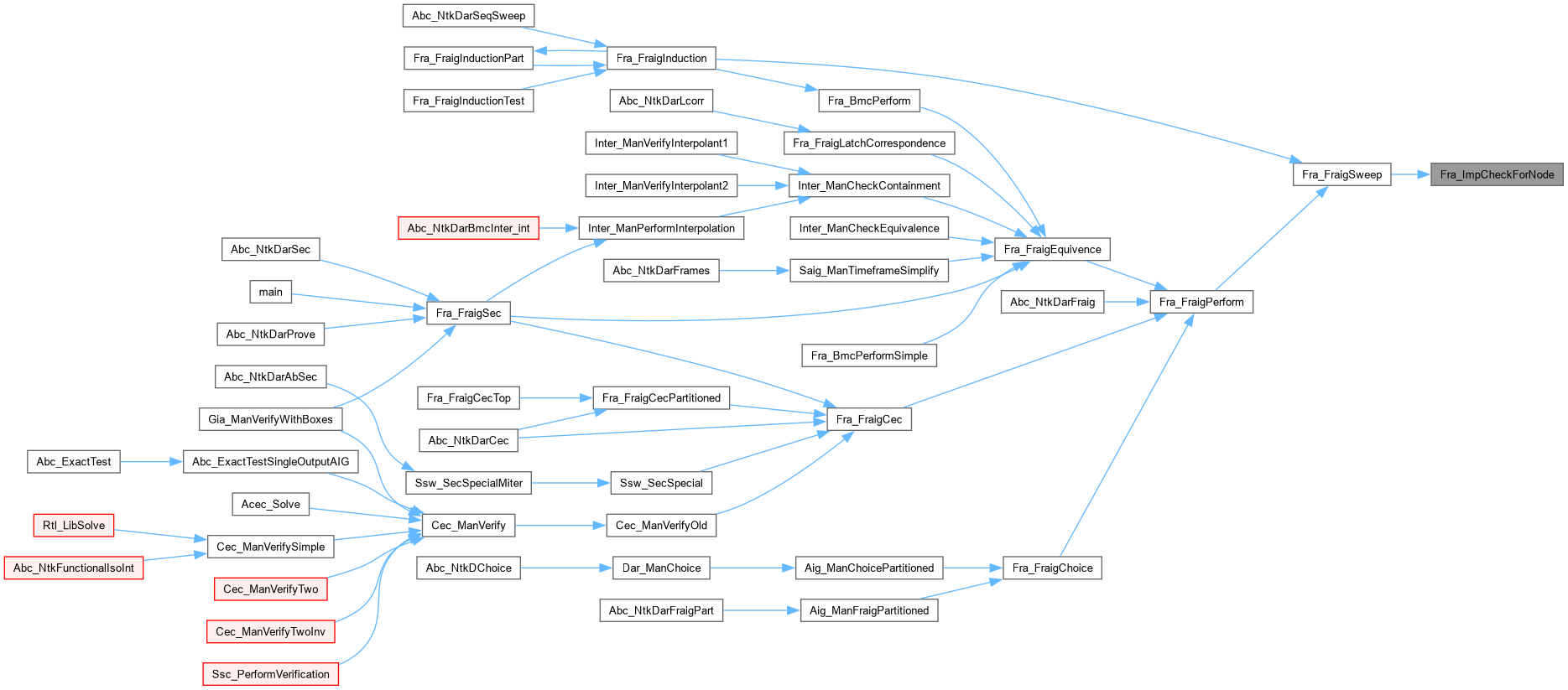

Function*************************************************************

Synopsis [Check implications for the node (if they are present).]

Description [Returns the new position in the array.]

SideEffects []

SeeAlso []

Definition at line 503 of file fraImp.c.

|

extern |

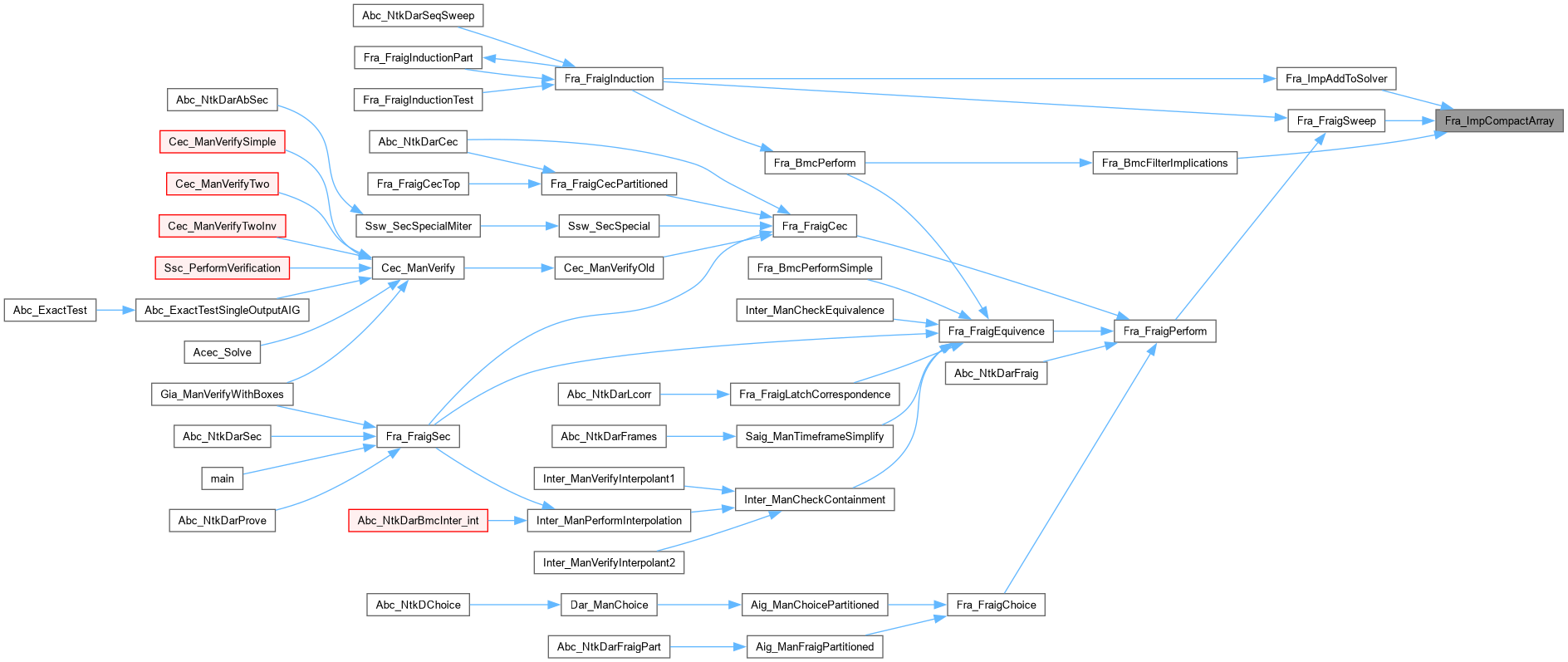

Function*************************************************************

Synopsis [Removes empty implications.]

Description []

SideEffects []

SeeAlso []

Definition at line 607 of file fraImp.c.

|

extern |

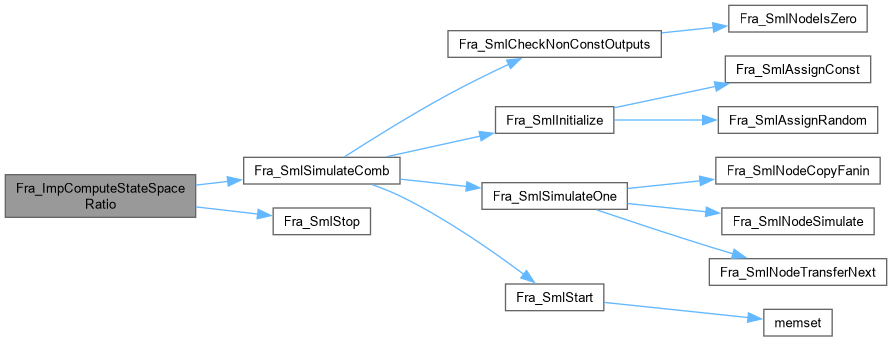

Function*************************************************************

Synopsis [Determines the ratio of the state space by computed implications.]

Description []

SideEffects []

SeeAlso []

Definition at line 628 of file fraImp.c.

|

extern |

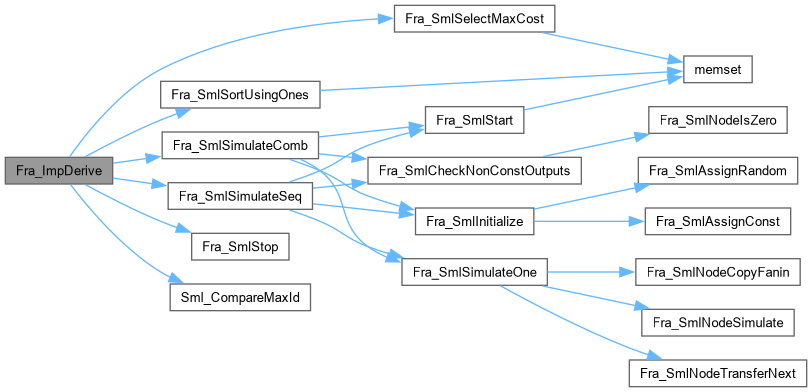

Function*************************************************************

Synopsis [Derives implication candidates.]

Description [Implication candidates have the property that (1) they hold using sequential simulation information (2) they do not hold using combinational simulation information (3) they have as high expressive power as possible (heuristically) that is, they are easy to disprove combinationally meaning they cover relatively larger sequential subspace.]

SideEffects []

SeeAlso []

Definition at line 321 of file fraImp.c.

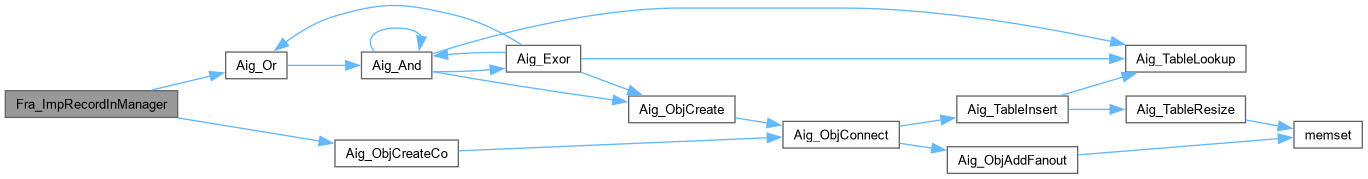

Function*************************************************************

Synopsis [Record proven implications in the AIG manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 705 of file fraImp.c.

Function*************************************************************

Synopsis [Removes those implications that no longer hold.]

Description [Returns 1 if refinement has happened.]

SideEffects []

SeeAlso []

Definition at line 575 of file fraImp.c.

|

extern |

Function*************************************************************

Synopsis [Returns the number of failed implications.]

Description []

SideEffects []

SeeAlso []

Definition at line 665 of file fraImp.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fraIndVer.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis [Verification of the inductive invariant.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Verifies the inductive invariant.]

Description []

SideEffects []

SeeAlso []

Definition at line 46 of file fraIndVer.c.

|

extern |

Function*************************************************************

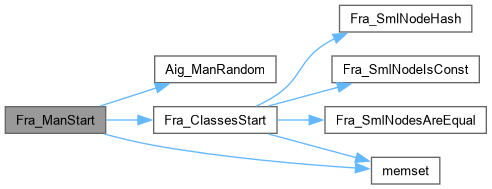

Synopsis [Starts the fraiging manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 145 of file fraMan.c.

|

extern |

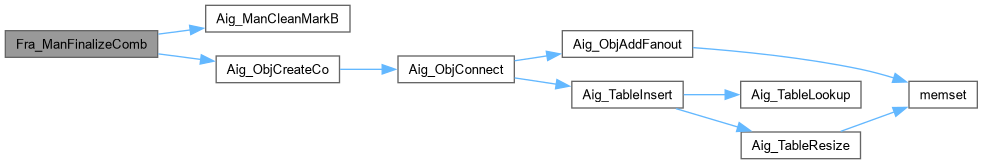

Function*************************************************************

Synopsis [Finalizes the combinational miter after fraiging.]

Description []

SideEffects []

SeeAlso []

Definition at line 217 of file fraMan.c.

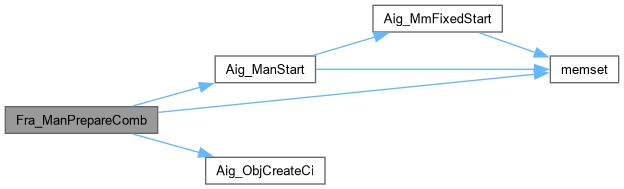

Function*************************************************************

Synopsis [Prepares the new manager to begin fraiging.]

Description []

SideEffects []

SeeAlso []

Definition at line 176 of file fraMan.c.

|

extern |

Function*************************************************************

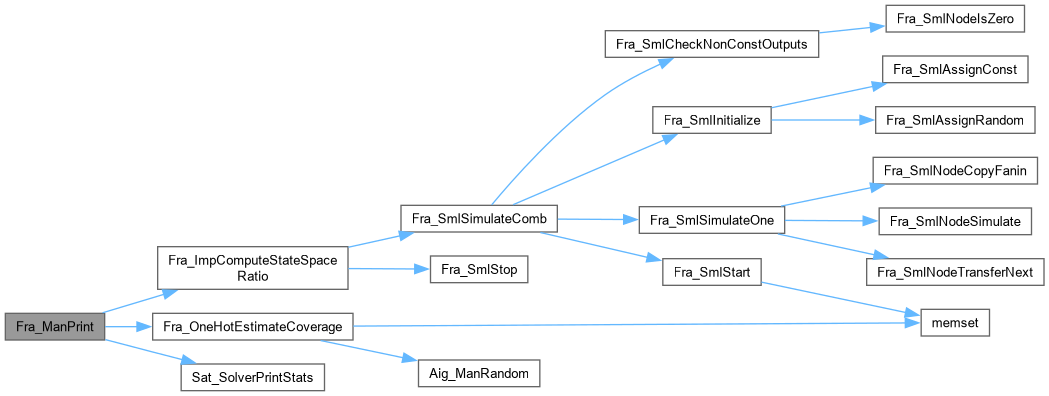

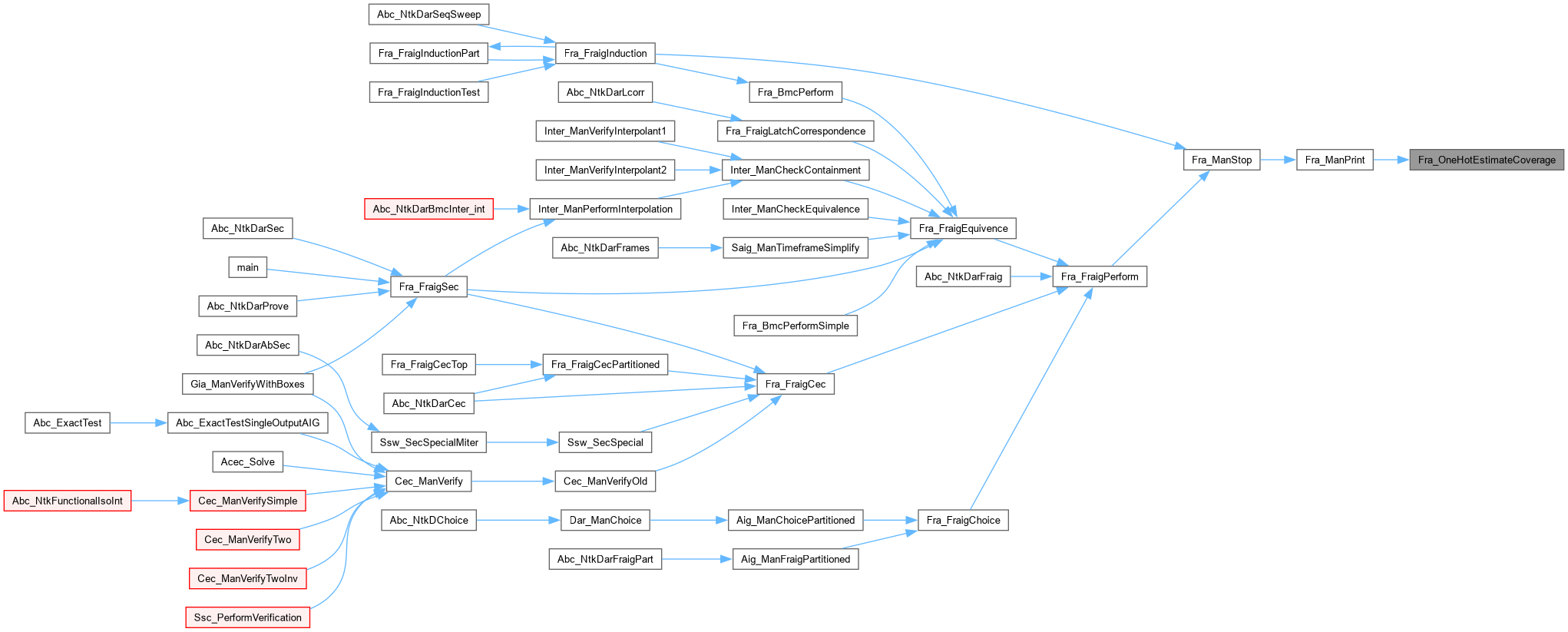

Synopsis [Prints stats for the fraiging manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 278 of file fraMan.c.

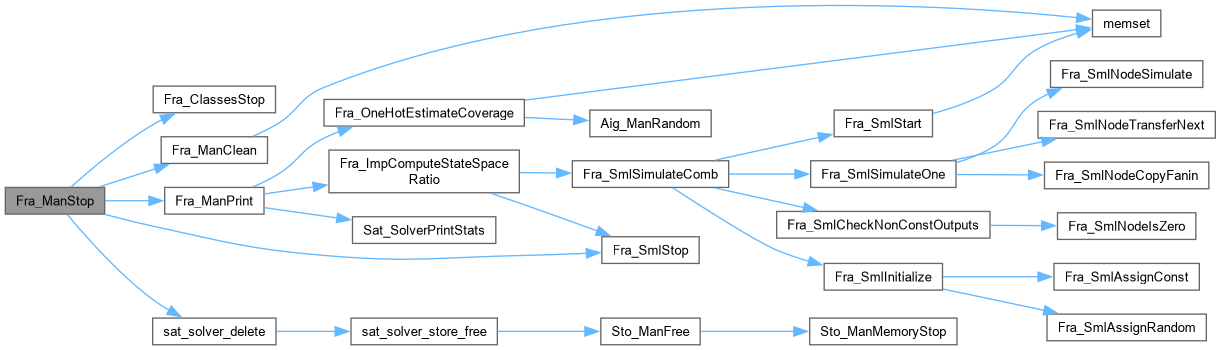

Function*************************************************************

Synopsis [Starts the fraiging manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 104 of file fraMan.c.

|

extern |

Function*************************************************************

Synopsis [Stops the fraiging manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 240 of file fraMan.c.

Function*************************************************************

Synopsis [Runs equivalence test for one node.]

Description [Returns the fraiged node.]

SideEffects []

SeeAlso []

Definition at line 425 of file fraSat.c.

|

extern |

Function*************************************************************

Synopsis [Runs the result of test for pObj => pNew.]

Description []

SideEffects []

SeeAlso []

Definition at line 317 of file fraSat.c.

FUNCTION DEFINITIONS ///.

Function*************************************************************

Synopsis [Runs equivalence test for the two nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 48 of file fraSat.c.

|

extern |

Function*************************************************************

Synopsis [Runs the result of test for pObj => pNew.]

Description []

SideEffects []

SeeAlso []

Definition at line 209 of file fraSat.c.

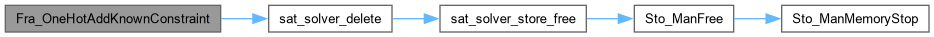

Function*************************************************************

Synopsis [Assumes one-hot implications in the SAT solver.]

Description []

SideEffects []

SeeAlso []

Definition at line 439 of file fraHot.c.

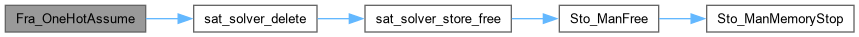

Function*************************************************************

Synopsis [Assumes one-hot implications in the SAT solver.]

Description []

SideEffects []

SeeAlso []

Definition at line 191 of file fraHot.c.

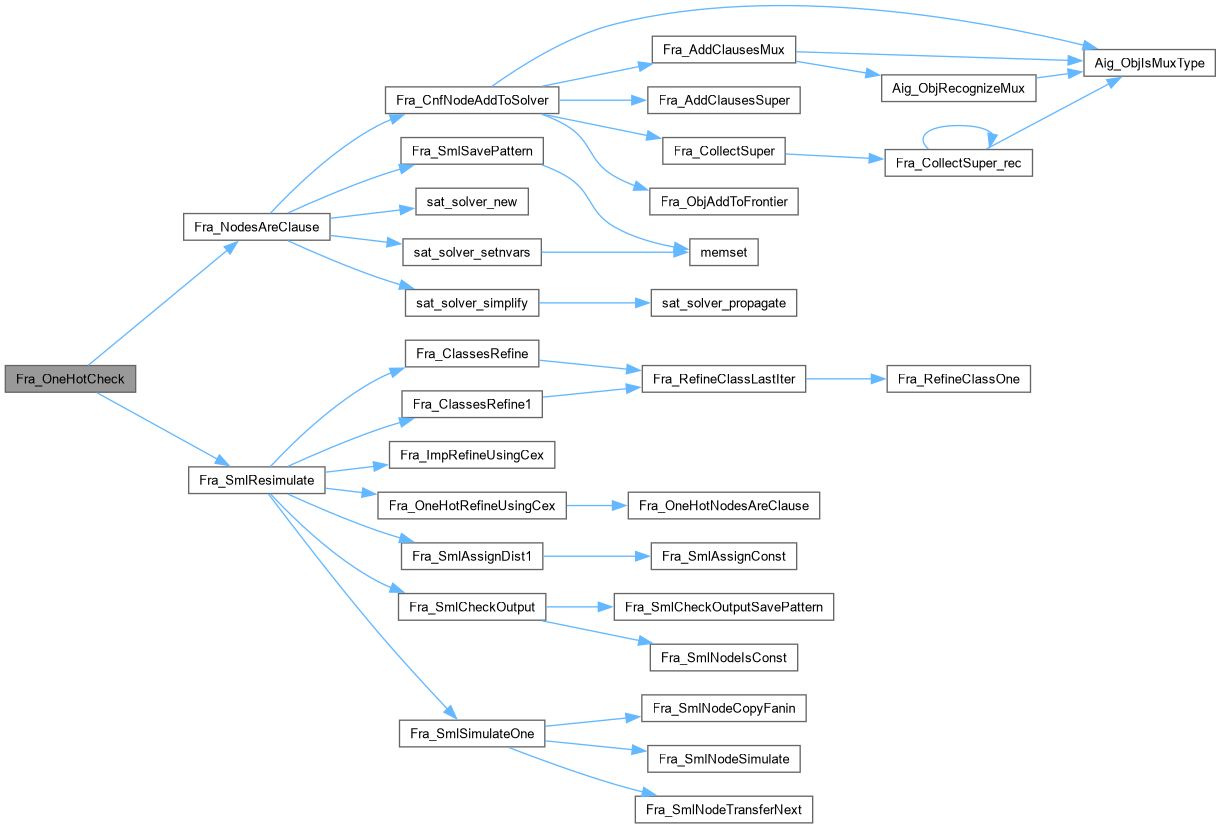

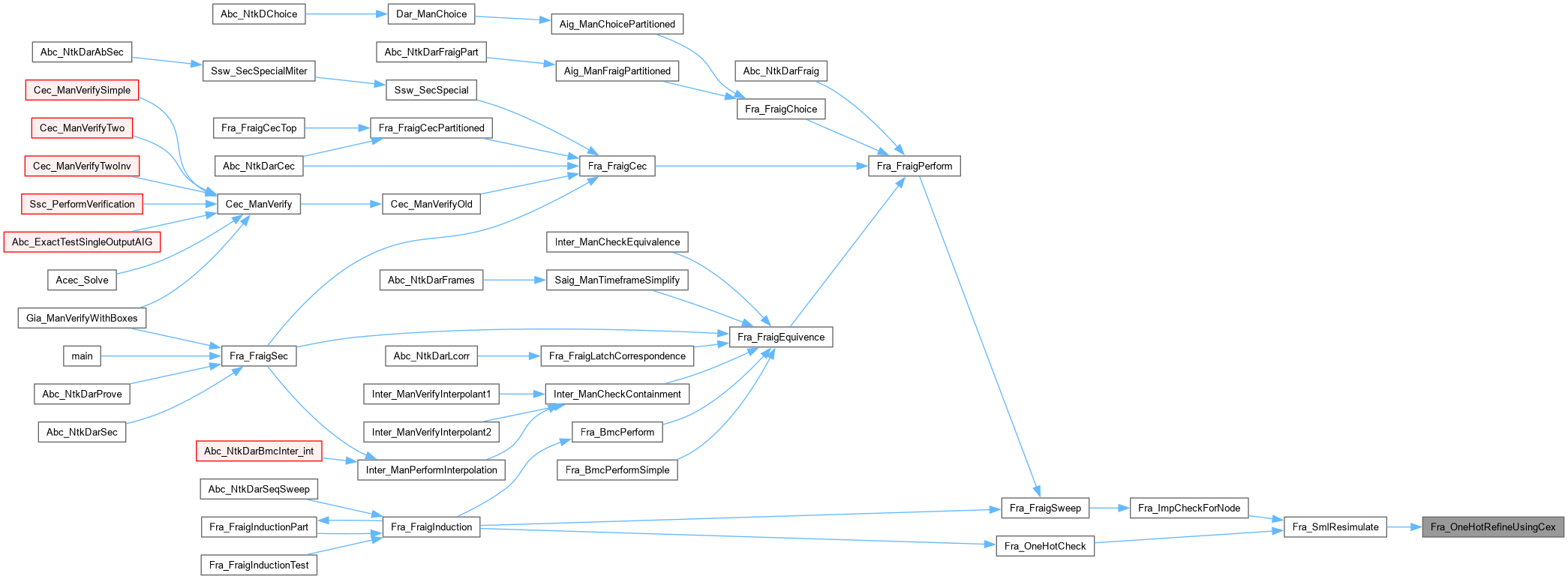

Function*************************************************************

Synopsis [Checks one-hot implications.]

Description []

SideEffects []

SeeAlso []

Definition at line 229 of file fraHot.c.

Function*************************************************************

Synopsis [Computes one-hot implications.]

Description []

SideEffects []

SeeAlso []

Definition at line 134 of file fraHot.c.

Function*************************************************************

Synopsis [Removes those implications that no longer hold.]

Description [Returns 1 if refinement has happened.]

SideEffects []

SeeAlso []

Definition at line 303 of file fraHot.c.

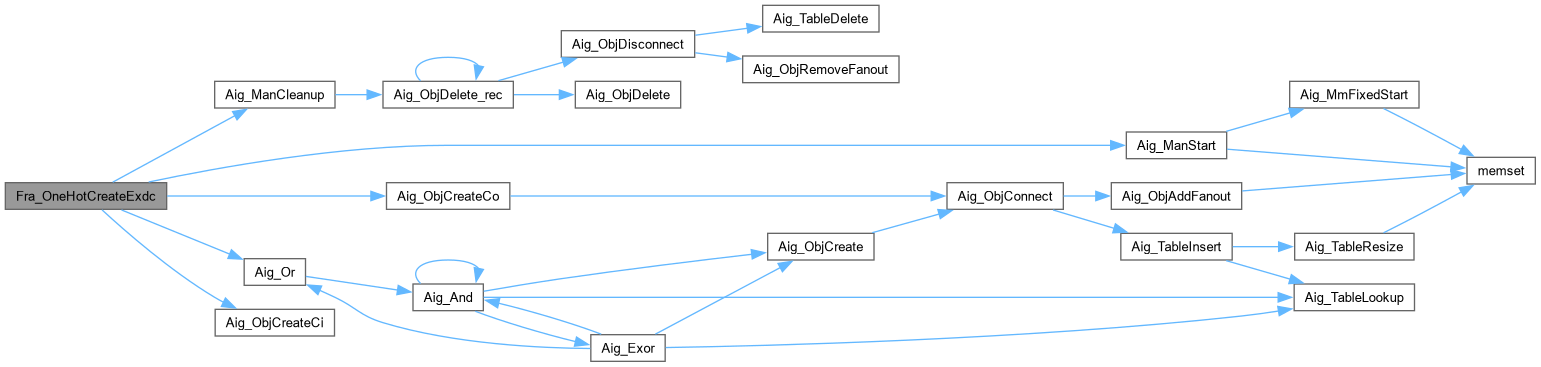

Function*************************************************************

Synopsis [Creates one-hotness EXDC.]

Description []

SideEffects []

SeeAlso []

Definition at line 398 of file fraHot.c.

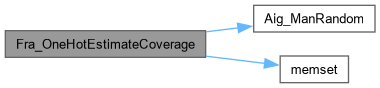

Function*************************************************************

Synopsis [Estimates the coverage of state space by clauses.]

Description []

SideEffects []

SeeAlso []

Definition at line 328 of file fraHot.c.

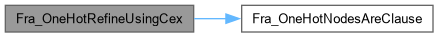

Function*************************************************************

Synopsis [Removes those implications that no longer hold.]

Description [Returns 1 if refinement has happened.]

SideEffects []

SeeAlso []

Definition at line 266 of file fraHot.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fraMan.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis [Starts the FRAIG manager.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

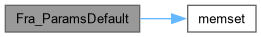

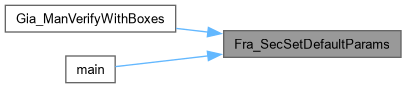

Synopsis [Sets the default solving parameters.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file fraMan.c.

|

extern |

Function*************************************************************

Synopsis [Sets the default solving parameters.]

Description []

SideEffects []

SeeAlso []

Definition at line 75 of file fraMan.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fraSec.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis [Performs SEC based on seq sweeping.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 52 of file fraSec.c.

|

extern |

Function*************************************************************

Synopsis [Returns 1 if the one of the output is already non-constant 0.]

Description []

SideEffects []

SeeAlso []

Definition at line 326 of file fraSim.c.

|

extern |

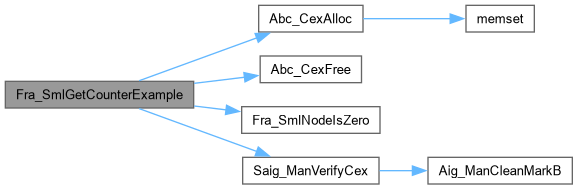

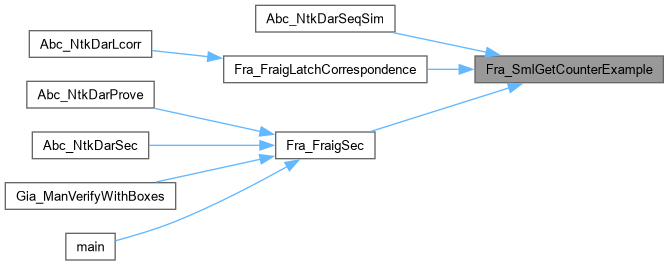

Function*************************************************************

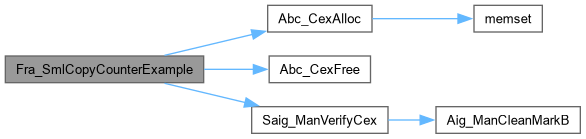

Synopsis [Generates seq counter-example from the combinational one.]

Description []

SideEffects []

SeeAlso []

Definition at line 1123 of file fraSim.c.

Function*************************************************************

Synopsis [Creates sequential counter-example from the simulation info.]

Description []

SideEffects []

SeeAlso []

Definition at line 1049 of file fraSim.c.

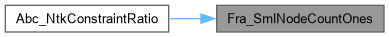

Function*************************************************************

Synopsis [Counts the number of one's in the patten of the output.]

Description []

SideEffects []

SeeAlso []

Definition at line 177 of file fraSim.c.

|

extern |

DECLARATIONS ///.

CFile****************************************************************

FileName [fraSim.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis []

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Computes hash value of the node using its simulation info.]

Description []

SideEffects []

SeeAlso []

Definition at line 46 of file fraSim.c.

|

extern |

Function*************************************************************

Synopsis [Returns 1 if simulation info is composed of all zeros.]

Description []

SideEffects []

SeeAlso []

Definition at line 86 of file fraSim.c.

|

extern |

Function*************************************************************

Synopsis [Counts the number of 1s in the XOR of simulation data.]

Description []

SideEffects []

SeeAlso []

Definition at line 133 of file fraSim.c.

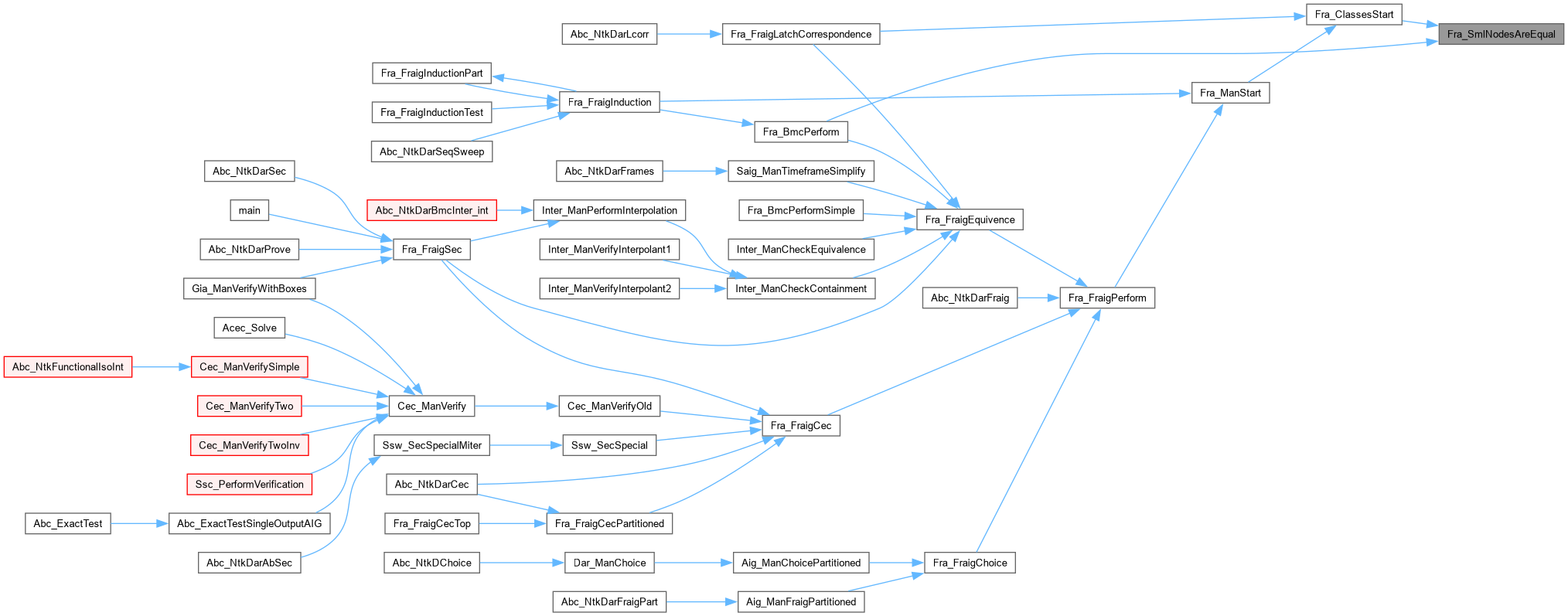

Function*************************************************************

Synopsis [Returns 1 if simulation infos are equal.]

Description []

SideEffects []

SeeAlso []

Definition at line 109 of file fraSim.c.

|

extern |

Function*************************************************************

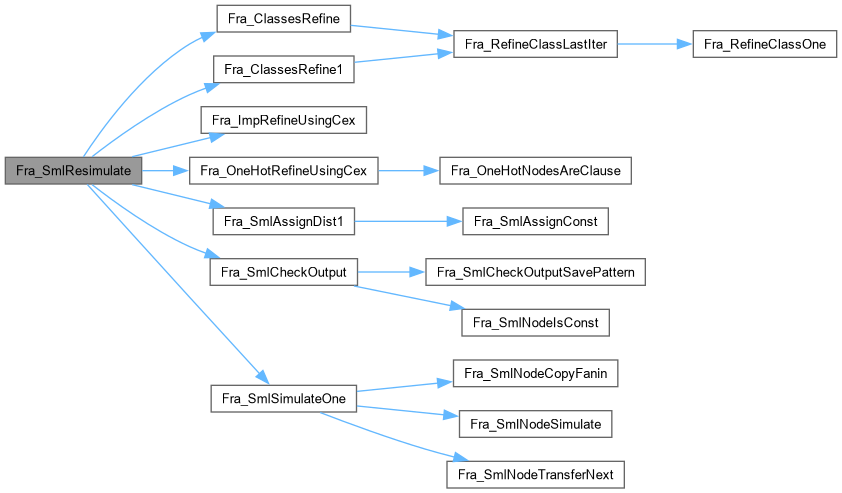

Synopsis [Resimulates fraiging manager after finding a counter-example.]

Description []

SideEffects []

SeeAlso []

Definition at line 703 of file fraSim.c.

|

extern |

Function*************************************************************

Synopsis [Copy pattern from the solver into the internal storage.]

Description []

SideEffects []

SeeAlso []

Definition at line 241 of file fraSim.c.

|

extern |

Function*************************************************************

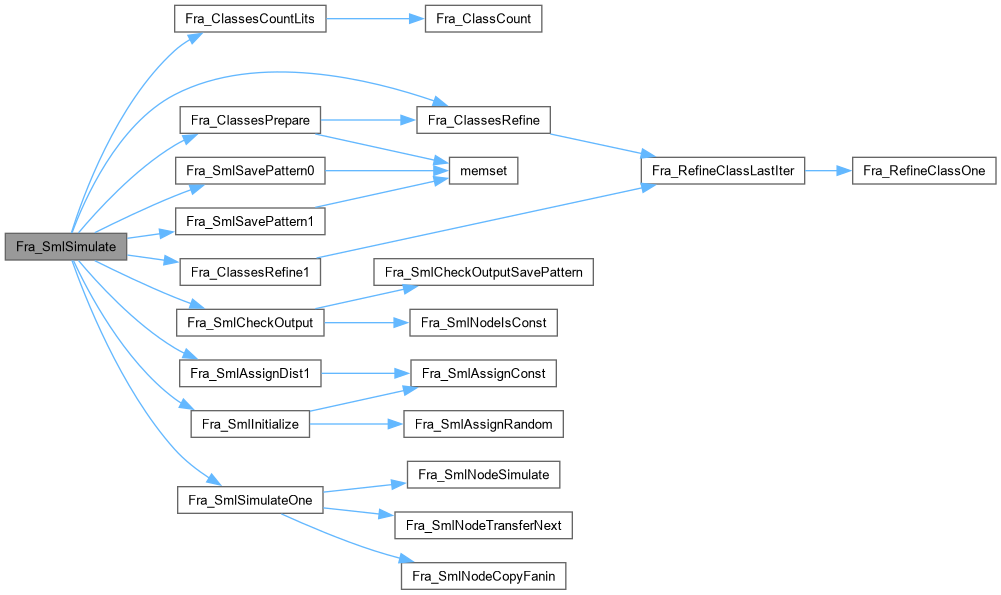

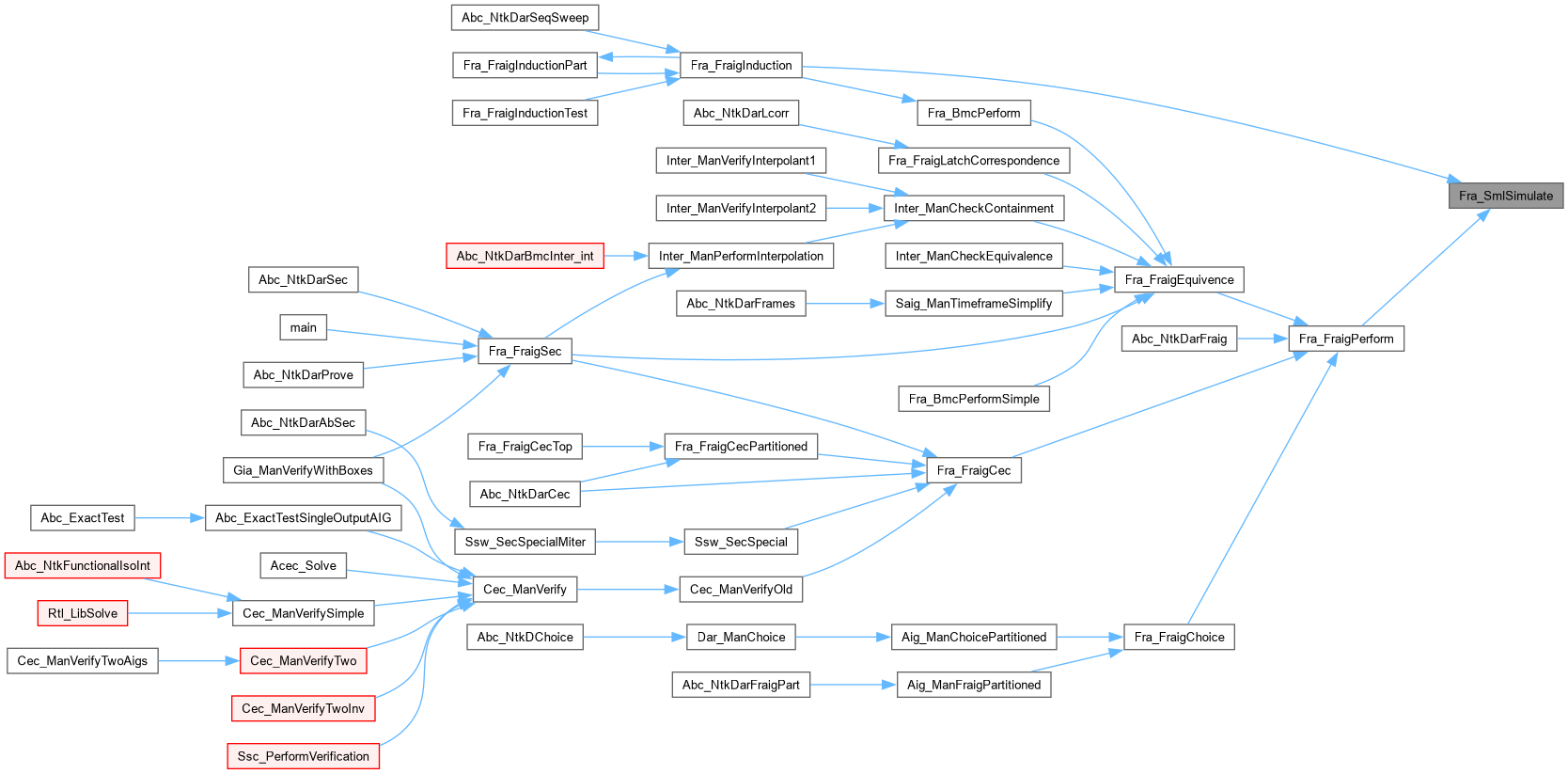

Synopsis [Performs simulation of the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 738 of file fraSim.c.

Function*************************************************************

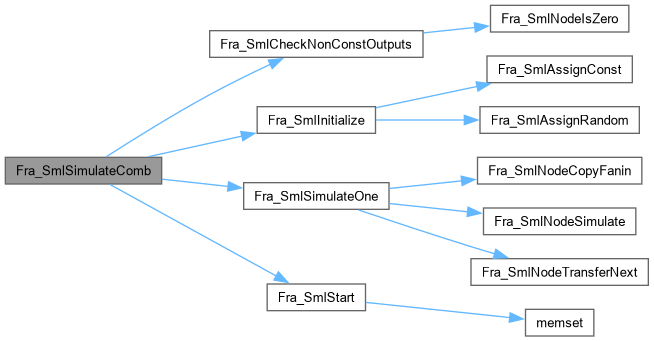

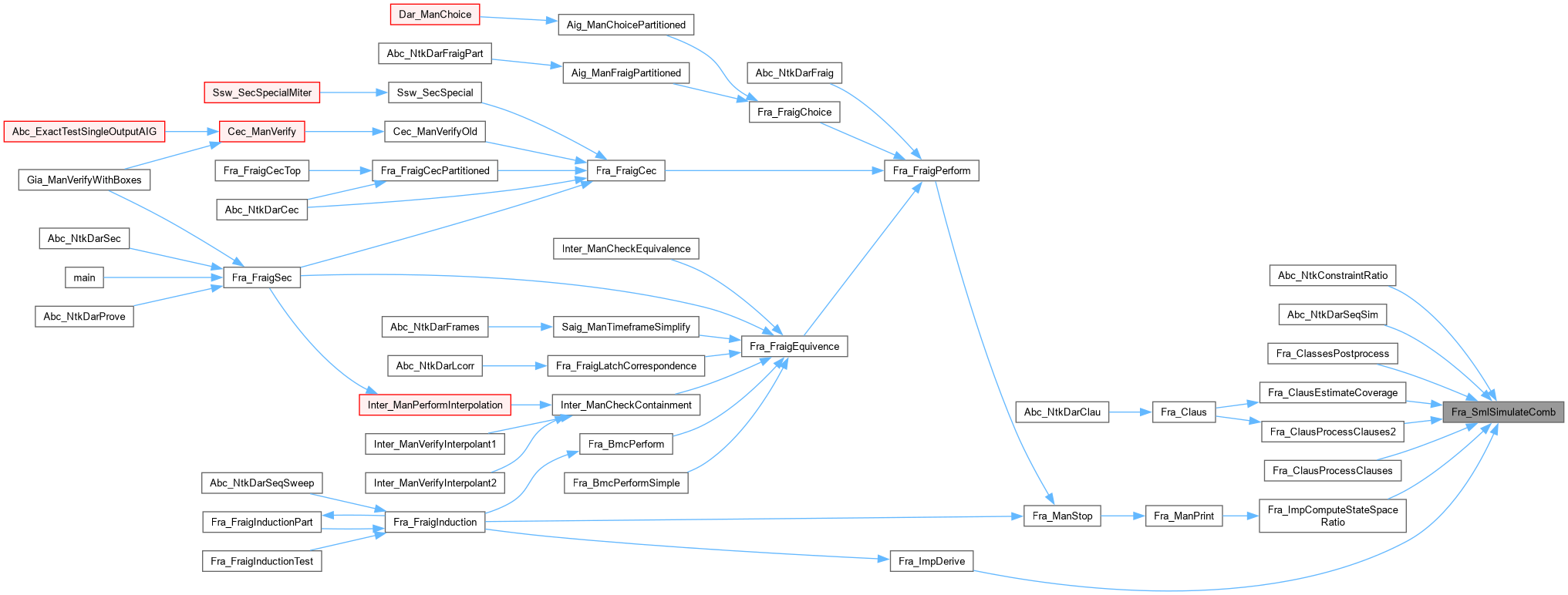

Synopsis [Performs simulation of the uninitialized circuit.]

Description []

SideEffects []

SeeAlso []

Definition at line 856 of file fraSim.c.

|

extern |

Function*************************************************************

Synopsis [Assigns simulation patters derived from file.]

Description []

SideEffects []

SeeAlso []

Definition at line 987 of file fraSim.c.

|

extern |

Function*************************************************************

Synopsis [Performs simulation of the initialized circuit.]

Description []

SideEffects []

SeeAlso []

Definition at line 1027 of file fraSim.c.

Function*************************************************************

Synopsis [Allocates simulation manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 813 of file fraSim.c.

|

extern |