119{

124 int nFrames, RetValue, nIter;

125 abctime clk, clkTotal = Abc_Clock();

126 int TimeOut = 0;

127 int fLatchCorr = 0;

128 float TimeLeft = 0.0;

130

131

134 if ( RetValue >= 0 )

135 goto finish;

136

137

142 {

143 printf( "Original miter: Latches = %5d. Nodes = %6d.\n",

144 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

145 }

146

147

148

149clk = Abc_Clock();

150 if ( pNew->nRegs )

152 if ( pNew->nRegs )

155 {

156 printf( "Sequential cleanup: Latches = %5d. Nodes = %6d. ",

157 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

158ABC_PRT(

"Time", Abc_Clock() - clk );

159 }

161 if ( RetValue >= 0 )

162 goto finish;

163

164

165clk = Abc_Clock();

167 {

169 pNew->nTruePis = Aig_ManCiNum(pNew) - Aig_ManRegNum(pNew);

170 pNew->nTruePos = Aig_ManCoNum(pNew) - Aig_ManRegNum(pNew);

174 {

175 printf( "Phase abstraction: Latches = %5d. Nodes = %6d. ",

176 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

177ABC_PRT(

"Time", Abc_Clock() - clk );

178 }

179 }

180

181

183 {

184clk = Abc_Clock();

185

189 {

190 printf( "Forward retiming: Latches = %5d. Nodes = %6d. ",

191 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

192ABC_PRT(

"Time", Abc_Clock() - clk );

193 }

194 }

195

196

197clk = Abc_Clock();

198 if ( pNew->nRegs )

199 {

201

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

218

219

220

223 nIter = pPars2->nIters;

224

225

227

228 if ( pTemp->pSeqModel )

229 {

231 printf( "Fra_FraigSec(): Counter-example verification has FAILED.\n" );

232 if ( Saig_ManPiNum(

p) != Saig_ManPiNum(pTemp) )

233 printf( "The counter-example is invalid because of phase abstraction.\n" );

234 else

235 {

237 p->pSeqModel =

Abc_CexDup( pTemp->pSeqModel, Aig_ManRegNum(

p) );

239 }

240 }

241 if ( pNew == NULL )

242 {

244 {

245 RetValue = 0;

247 {

248 printf( "Networks are NOT EQUIVALENT after simulation. " );

249ABC_PRT(

"Time", Abc_Clock() - clkTotal );

250 }

252 {

253 printf( "SOLUTION: FAIL " );

254ABC_PRT(

"Time", Abc_Clock() - clkTotal );

255 }

257 return RetValue;

258 }

259 pNew = pTemp;

260 RetValue = -1;

261 TimeOut = 1;

262 goto finish;

263 }

265

267 {

268 printf( "Latch-corr (I=%3d): Latches = %5d. Nodes = %6d. ",

269 nIter, Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

270ABC_PRT(

"Time", Abc_Clock() - clk );

271 }

272 }

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

290 {

291clk = Abc_Clock();

293

296 {

297 printf( "Fraiging: Latches = %5d. Nodes = %6d. ",

298 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

299ABC_PRT(

"Time", Abc_Clock() - clk );

300 }

301 }

302

303 if ( pNew->nRegs == 0 )

305

307 if ( RetValue >= 0 )

308 goto finish;

309

310

311

312

313

314

315

316

317

318

319

320

321

322

323

324

326 {

327

328clk = Abc_Clock();

329 pNew->nTruePis = Aig_ManCiNum(pNew) - Aig_ManRegNum(pNew);

330 pNew->nTruePos = Aig_ManCoNum(pNew) - Aig_ManRegNum(pNew);

331

337 {

338 printf( "Min-reg retiming: Latches = %5d. Nodes = %6d. ",

339 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

340ABC_PRT(

"Time", Abc_Clock() - clk );

341 }

342 }

343

344

347 for ( nFrames = 1; nFrames <= pParSec->

nFramesMax; nFrames *= 2 )

348 {

349

350

351

352

353

354

355

356

357

358

359

360

361

362

363

364

365clk = Abc_Clock();

369

370

371 pPars2->nFramesK = nFrames;

372 pPars2->nBTLimit = pParSec->

nBTLimit;

374

375

376 if ( RetValue == -1 && pPars2->nConflicts > pPars2->nBTLimitGlobal )

377 {

379 printf( "Global conflict limit (%d) exceeded.\n", pPars2->nBTLimitGlobal );

380 RetValue = -1;

381 TimeOut = 1;

382 goto finish;

383 }

384

386

387 if ( Aig_ManRegNum(pNew) > 0 )

389 else

391

392 if ( pNew == NULL )

393 {

394 pNew = pTemp;

395 RetValue = -1;

396 TimeOut = 1;

397 goto finish;

398 }

399

400

401

405 {

406 printf( "K-step (K=%2d,I=%3d): Latches = %5d. Nodes = %6d. ",

407 nFrames, pPars2->nIters, Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

408ABC_PRT(

"Time", Abc_Clock() - clk );

409 }

410 if ( RetValue != -1 )

411 break;

412

413

414

415 if ( pNew->nRegs )

416 {

417

418clk = Abc_Clock();

419 pNew->nTruePis = Aig_ManCiNum(pNew) - Aig_ManRegNum(pNew);

420 pNew->nTruePos = Aig_ManCoNum(pNew) - Aig_ManRegNum(pNew);

421

427 {

428 printf( "Min-reg retiming: Latches = %5d. Nodes = %6d. ",

429 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

430ABC_PRT(

"Time", Abc_Clock() - clk );

431 }

432 }

433

434 if ( pNew->nRegs )

436

437

438clk = Abc_Clock();

441

445 {

446 printf( "Rewriting: Latches = %5d. Nodes = %6d. ",

447 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

448ABC_PRT(

"Time", Abc_Clock() - clk );

449 }

450

451

452 if ( pNew->nRegs )

453 {

454clk = Abc_Clock();

455 pSml =

Fra_SmlSimulateSeq( pNew, 0, 128 * nFrames, 1 + 16/(1+Aig_ManNodeNum(pNew)/1000), 1 );

457 {

458 printf( "Seq simulation : Latches = %5d. Nodes = %6d. ",

459 Aig_ManRegNum(pNew), Aig_ManNodeNum(pNew) );

460ABC_PRT(

"Time", Abc_Clock() - clk );

461 }

463 {

465

466 if ( Saig_ManPiNum(

p) != Saig_ManPiNum(pNew) )

467 printf( "The counter-example is invalid because of phase abstraction.\n" );

468 else

469 {

471 p->pSeqModel =

Abc_CexDup( pNew->pSeqModel, Aig_ManRegNum(

p) );

473 }

474

477 RetValue = 0;

479 {

480 printf( "Networks are NOT EQUIVALENT after simulation. " );

481ABC_PRT(

"Time", Abc_Clock() - clkTotal );

482 }

484 {

485 printf( "SOLUTION: FAIL " );

486ABC_PRT(

"Time", Abc_Clock() - clkTotal );

487 }

488 return RetValue;

489 }

491 }

492 }

493

494

496

497

498clk = Abc_Clock();

500 if ( pParSec->

fInterpolation && RetValue == -1 && Aig_ManRegNum(pNew) > 0 )

501 {

503 int Depth;

506

509 if ( Saig_ManPoNum(pNew) == 1 )

510 {

512 }

514 {

518 int i, Counter = 0;

520 {

521 if ( Aig_ObjFanin0(pObjPo) == Aig_ManConst1(pNew) )

522 continue;

523 if ( pPars->fVerbose )

524 printf( "Solving output %2d (out of %2d):\n", i, Saig_ManPoNum(pNew) );

526 pTemp =

Aig_ManScl( pAux = pTemp, 1, 1, 0, -1, -1, 0, 0 );

528 if ( Saig_ManRegNum(pTemp) > 0 )

529 {

531 if ( pTemp->pSeqModel )

532 {

533 pCex =

p->pSeqModel =

Abc_CexDup( pTemp->pSeqModel, Aig_ManRegNum(

p) );

534 pCex->iPo = i;

536 break;

537 }

538

539 if ( RetValue == 1 )

540 {

542

543 }

544 else

545 {

546 Counter++;

547

548 }

549 }

550 else

551 Counter++;

552

554 printf( "Solving output %3d (out of %3d) using interpolation.\r", i, Saig_ManPoNum(pNew) );

555 }

557 if ( pCex == NULL )

558 {

559 printf( "Interpolation left %d (out of %d) outputs unsolved \n", Counter, Saig_ManPoNum(pNew) );

560 if ( Counter )

561 RetValue = -1;

562 }

565 pNew =

Aig_ManScl( pTemp = pNew, 1, 1, 0, -1, -1, 0, 0 );

567 }

568 else

569 {

572 if ( pNewOrpos->pSeqModel )

573 {

575 pCex = pNew->pSeqModel = pNewOrpos->pSeqModel; pNewOrpos->pSeqModel = NULL;

577 }

579 }

580

582 {

583 if ( RetValue == 1 )

584 printf( "Property proved using interpolation. " );

585 else if ( RetValue == 0 )

586 printf( "Property DISPROVED in frame %d using interpolation. ", Depth );

587 else if ( RetValue == -1 )

588 printf( "Property UNDECIDED after interpolation. " );

589 else

591ABC_PRT(

"Time", Abc_Clock() - clk );

592 }

593 }

594

595

596 if ( pParSec->

fReachability && RetValue == -1 && Aig_ManRegNum(pNew) > 0 && Aig_ManRegNum(pNew) < pParSec->

nBddVarsMax )

597 {

608 pNew->nTruePis = Aig_ManCiNum(pNew) - Aig_ManRegNum(pNew);

609 pNew->nTruePos = Aig_ManCoNum(pNew) - Aig_ManRegNum(pNew);

611 }

612

613

614 if ( pParSec->

fUsePdr && RetValue == -1 && Aig_ManRegNum(pNew) > 0 )

615 {

619 pPars->fVerbose = pParSec->

fVerbose;

621 printf( "Running property directed reachability...\n" );

623 if ( pNew->pSeqModel )

625 }

626

627finish:

628

629 if ( RetValue == 1 )

630 {

632 {

633 printf( "Networks are equivalent. " );

634ABC_PRT(

"Time", Abc_Clock() - clkTotal );

635 }

637 {

638 printf( "SOLUTION: PASS " );

639ABC_PRT(

"Time", Abc_Clock() - clkTotal );

640 }

641 }

642 else if ( RetValue == 0 )

643 {

644 if ( pNew->pSeqModel == NULL )

645 {

646 int i;

647

648 pNew->pSeqModel =

Abc_CexAlloc( Aig_ManRegNum(pNew), pNew->nTruePis, 1 );

649

650

652 for ( i = 0; i < pNew->nTruePis; i++ )

653 Abc_InfoSetBit( pNew->pSeqModel->pData, i );

654 }

656 {

657 printf( "Networks are NOT EQUIVALENT. " );

658ABC_PRT(

"Time", Abc_Clock() - clkTotal );

659 }

661 {

662 printf( "SOLUTION: FAIL " );

663ABC_PRT(

"Time", Abc_Clock() - clkTotal );

664 }

665 }

666 else

667 {

669

674 {

675 printf( "Networks are UNDECIDED. " );

676ABC_PRT(

"Time", Abc_Clock() - clkTotal );

677 }

679 {

680 printf( "SOLUTION: UNDECIDED " );

681ABC_PRT(

"Time", Abc_Clock() - clkTotal );

682 }

683 if ( !TimeOut && !pParSec->

fSilent )

684 {

685 static int Counter = 1;

686 char pFileName[1000];

688 sprintf( pFileName,

"sm%02d.aig", Counter++ );

690 printf( "The unsolved reduced miter is written into file \"%s\".\n", pFileName );

691 }

692 }

693 if ( pNew->pSeqModel )

694 {

695 if ( Saig_ManPiNum(

p) != Saig_ManPiNum(pNew) )

696 printf( "The counter-example is invalid because of phase abstraction.\n" );

697 else

698 {

700 p->pSeqModel =

Abc_CexDup( pNew->pSeqModel, Aig_ManRegNum(

p) );

702 }

703 }

704 if ( ppResult != NULL )

706 if ( pNew )

708 return RetValue;

709}

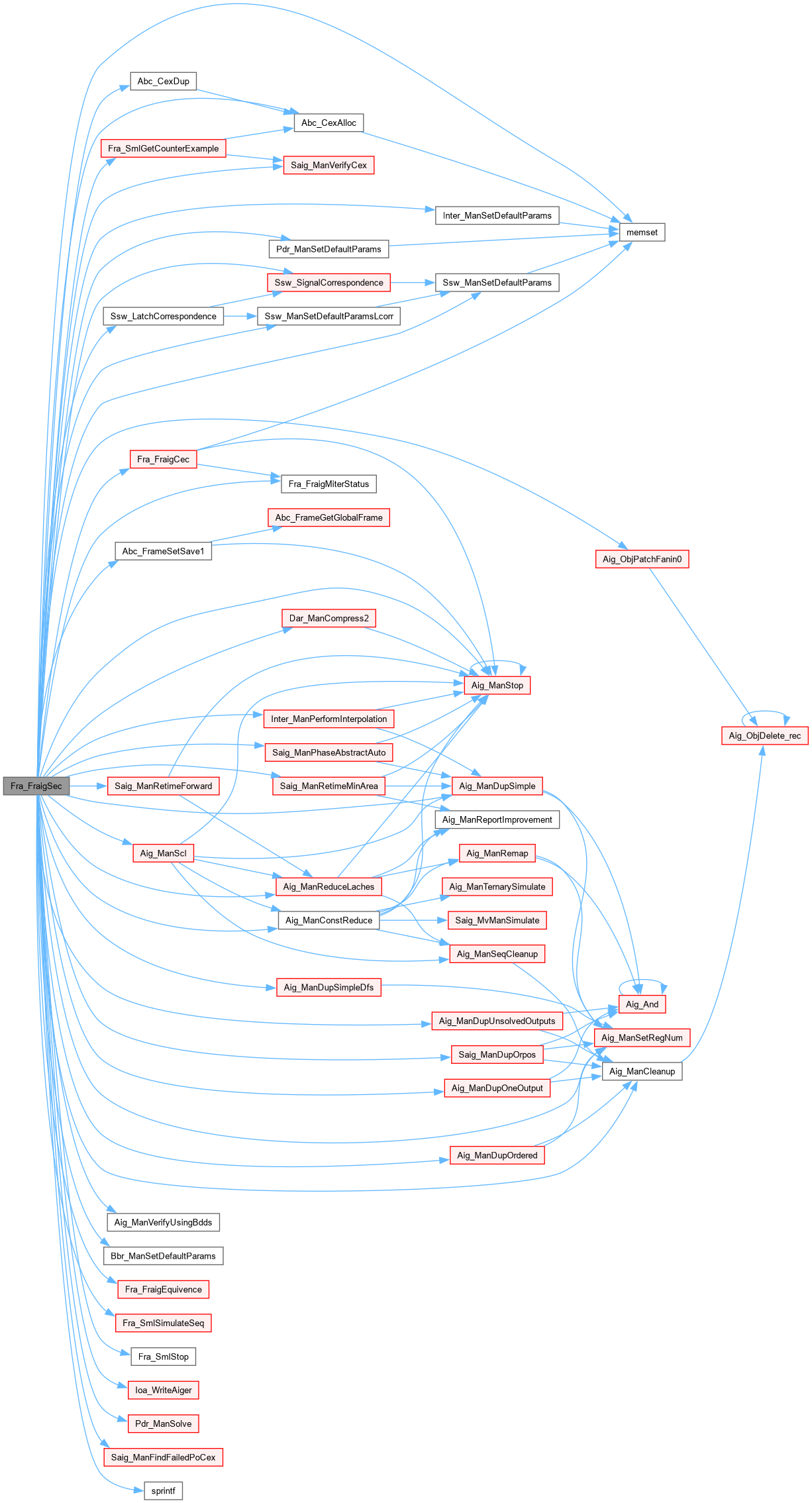

Aig_Man_t * Aig_ManDupOrdered(Aig_Man_t *p)

void Aig_ManSetRegNum(Aig_Man_t *p, int nRegs)

Aig_Man_t * Aig_ManDupSimple(Aig_Man_t *p)

DECLARATIONS ///.

Aig_Man_t * Aig_ManDupSimpleDfs(Aig_Man_t *p)

void Aig_ManStop(Aig_Man_t *p)

Aig_Man_t * Aig_ManReduceLaches(Aig_Man_t *p, int fVerbose)

Aig_Man_t * Aig_ManConstReduce(Aig_Man_t *p, int fUseMvSweep, int nFramesSymb, int nFramesSatur, int fVerbose, int fVeryVerbose)

struct Aig_Obj_t_ Aig_Obj_t

int Aig_ManCleanup(Aig_Man_t *p)

void Aig_ObjPatchFanin0(Aig_Man_t *p, Aig_Obj_t *pObj, Aig_Obj_t *pFaninNew)

Aig_Man_t * Aig_ManDupUnsolvedOutputs(Aig_Man_t *p, int fAddRegs)

Aig_Man_t * Aig_ManDupOneOutput(Aig_Man_t *p, int iPoNum, int fAddRegs)

Aig_Man_t * Aig_ManScl(Aig_Man_t *pAig, int fLatchConst, int fLatchEqual, int fUseMvSweep, int nFramesSymb, int nFramesSatur, int fVerbose, int fVeryVerbose)

Aig_Man_t * Dar_ManCompress2(Aig_Man_t *pAig, int fBalance, int fUpdateLevel, int fFanout, int fPower, int fVerbose)

Aig_Man_t * Fra_FraigEquivence(Aig_Man_t *pManAig, int nConfMax, int fProve)

void Fra_SmlStop(Fra_Sml_t *p)

int Fra_FraigCec(Aig_Man_t **ppAig, int nConfLimit, int fVerbose)

struct Fra_Sml_t_ Fra_Sml_t

int Fra_FraigMiterStatus(Aig_Man_t *p)

DECLARATIONS ///.

struct Fra_Ssw_t_ Fra_Ssw_t

Fra_Sml_t * Fra_SmlSimulateSeq(Aig_Man_t *pAig, int nPref, int nFrames, int nWords, int fCheckMiter)

Abc_Cex_t * Fra_SmlGetCounterExample(Fra_Sml_t *p)

typedefABC_NAMESPACE_HEADER_START struct Inter_ManParams_t_ Inter_ManParams_t

INCLUDES ///.

void Inter_ManSetDefaultParams(Inter_ManParams_t *p)

MACRO DEFINITIONS ///.

int Inter_ManPerformInterpolation(Aig_Man_t *pAig, Inter_ManParams_t *pPars, int *piFrame)

void Ioa_WriteAiger(Aig_Man_t *pMan, char *pFileName, int fWriteSymbols, int fCompact)

void Abc_FrameSetSave1(void *pAig)

void Pdr_ManSetDefaultParams(Pdr_Par_t *pPars)

MACRO DEFINITIONS ///.

typedefABC_NAMESPACE_HEADER_START struct Pdr_Par_t_ Pdr_Par_t

INCLUDES ///.

int Pdr_ManSolve(Aig_Man_t *p, Pdr_Par_t *pPars)

void Bbr_ManSetDefaultParams(Saig_ParBbr_t *p)

int Aig_ManVerifyUsingBdds(Aig_Man_t *pInit, Saig_ParBbr_t *pPars)

Aig_Man_t * Saig_ManPhaseAbstractAuto(Aig_Man_t *p, int fVerbose)

struct Saig_ParBbr_t_ Saig_ParBbr_t

Aig_Man_t * Saig_ManRetimeMinArea(Aig_Man_t *p, int nMaxIters, int fForwardOnly, int fBackwardOnly, int fInitial, int fVerbose)

#define Saig_ManForEachPo(p, pObj, i)

int Saig_ManFindFailedPoCex(Aig_Man_t *pAig, Abc_Cex_t *p)

Aig_Man_t * Saig_ManRetimeForward(Aig_Man_t *p, int nMaxIters, int fVerbose)

Aig_Man_t * Saig_ManDupOrpos(Aig_Man_t *p)

DECLARATIONS ///.

int Saig_ManVerifyCex(Aig_Man_t *pAig, Abc_Cex_t *p)

void Ssw_ManSetDefaultParams(Ssw_Pars_t *p)

DECLARATIONS ///.

void Ssw_ManSetDefaultParamsLcorr(Ssw_Pars_t *p)

typedefABC_NAMESPACE_HEADER_START struct Ssw_Pars_t_ Ssw_Pars_t

INCLUDES ///.

Aig_Man_t * Ssw_LatchCorrespondence(Aig_Man_t *pAig, Ssw_Pars_t *pPars)

Aig_Man_t * Ssw_SignalCorrespondence(Aig_Man_t *pAig, Ssw_Pars_t *pPars)

Abc_Cex_t * Abc_CexDup(Abc_Cex_t *p, int nRegsNew)

ABC_NAMESPACE_IMPL_START Abc_Cex_t * Abc_CexAlloc(int nRegs, int nRealPis, int nFrames)

DECLARATIONS ///.

typedefABC_NAMESPACE_HEADER_START struct Abc_Cex_t_ Abc_Cex_t

INCLUDES ///.