DECLARATIONS ///.

Date [Ver. 1.0. Started - June 20, 2005.]

] FUNCTION DEFINITIONS /// Function*************************************************************

48{

54 unsigned * pNext, * pThis;

55 int i, k, iBit, status, nRegs;

56

57

58

59

60

61

62

63

64

65 nRegs = Aig_ManRegNum(pAig); pAig->nRegs = 0;

67 pAig->nRegs = nRegs;

68

69

71 if ( pSat == NULL )

72 {

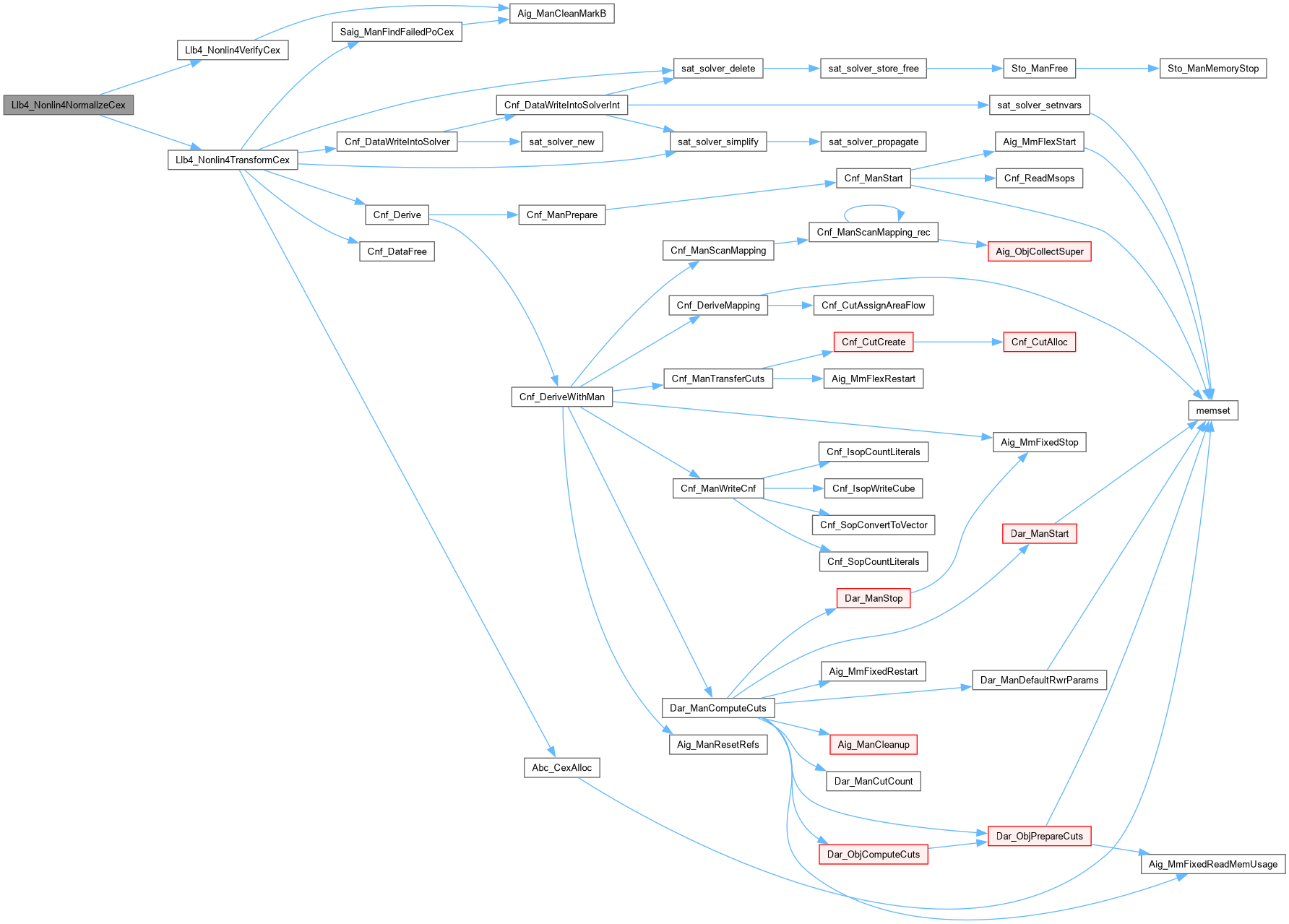

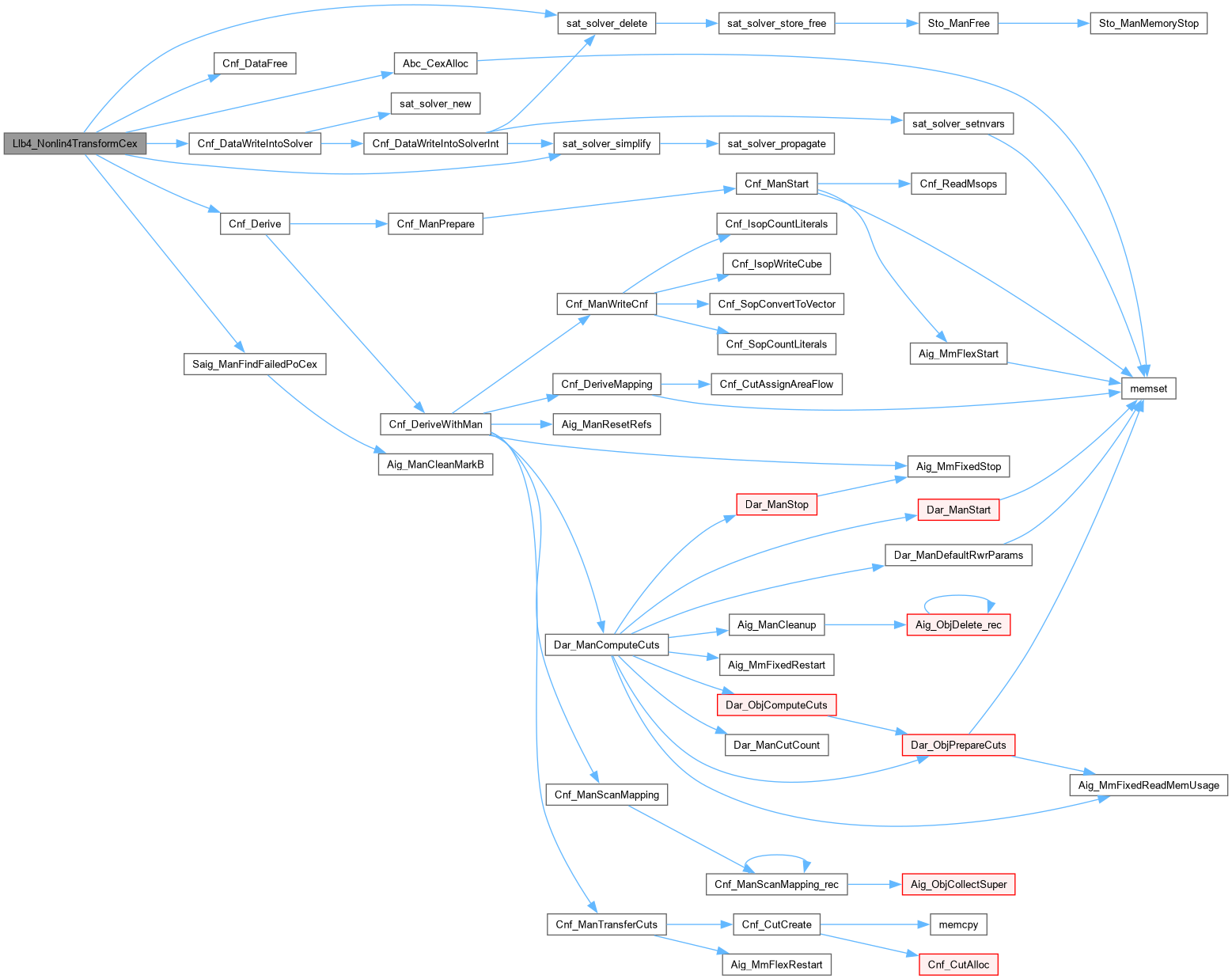

73 printf( "Llb4_Nonlin4TransformCex(): Counter-example generation has failed.\n" );

75 return NULL;

76 }

77

79 if ( status == 0 )

80 {

81 printf( "Llb4_Nonlin4TransformCex(): SAT solver is invalid.\n" );

84 return NULL;

85 }

86

87 pCex =

Abc_CexAlloc( Saig_ManRegNum(pAig), Saig_ManPiNum(pAig), Vec_PtrSize(vStates) );

88 pCex->iFrame = Vec_PtrSize(vStates)-1;

89 pCex->iPo = -1;

90

91

92 iBit = Saig_ManRegNum(pAig);

93 pThis = (unsigned *)Vec_PtrEntry( vStates, 0 );

94 vAssumps = Vec_IntAlloc( 2 * Aig_ManRegNum(pAig) );

96 {

97

98 Vec_IntClear( vAssumps );

100 Vec_IntPush( vAssumps, toLitCond( pCnf->

pVarNums[Aig_ObjId(pObj)], !Abc_InfoHasBit(pThis,k) ) );

102 Vec_IntPush( vAssumps, toLitCond( pCnf->

pVarNums[Aig_ObjId(pObj)], !Abc_InfoHasBit(pNext,k) ) );

103

104 status =

sat_solver_solve( pSat, Vec_IntArray(vAssumps), Vec_IntArray(vAssumps) + Vec_IntSize(vAssumps),

105 (ABC_INT64_T)0, (ABC_INT64_T)0, (ABC_INT64_T)0, (ABC_INT64_T)0 );

106

108 {

109 printf( "Llb4_Nonlin4TransformCex(): There is no transition between state %d and %d.\n", i-1, i );

110 Vec_IntFree( vAssumps );

114 return NULL;

115 }

116

118 if ( sat_solver_var_value(pSat, pCnf->

pVarNums[Aig_ObjId(pObj)]) )

119 Abc_InfoSetBit( pCex->pData, iBit + k );

120

121 iBit += Saig_ManPiNum(pAig);

122 pThis = pNext;

123 }

124

125

126 Vec_IntClear( vAssumps );

127 if ( iCexPo >= 0 )

128 {

130 if ( k == iCexPo )

131 Vec_IntPush( vAssumps, toLitCond( pCnf->

pVarNums[Aig_ObjId(pObj)], 0 ) );

132 }

133 else

134 {

136 Vec_IntPush( vAssumps, toLitCond( pCnf->

pVarNums[Aig_ObjId(pObj)], 0 ) );

137 }

138

139

140 status =

sat_solver_addclause( pSat, Vec_IntArray(vAssumps), Vec_IntArray(vAssumps) + Vec_IntSize(vAssumps) );

141 if ( status == 0 )

142 {

143 printf( "Llb4_Nonlin4TransformCex(): The SAT solver is unsat after adding last clause.\n" );

144 Vec_IntFree( vAssumps );

148 return NULL;

149 }

150

151 Vec_IntClear( vAssumps );

153 Vec_IntPush( vAssumps, toLitCond( pCnf->

pVarNums[Aig_ObjId(pObj)], !Abc_InfoHasBit(pThis,k) ) );

154

155 status =

sat_solver_solve( pSat, Vec_IntArray(vAssumps), Vec_IntArray(vAssumps) + Vec_IntSize(vAssumps),

156 (ABC_INT64_T)0, (ABC_INT64_T)0, (ABC_INT64_T)0, (ABC_INT64_T)0 );

158 {

159 printf( "Llb4_Nonlin4TransformCex(): There is no last transition that makes the property fail.\n" );

160 Vec_IntFree( vAssumps );

164 return NULL;

165 }

166

168 if ( sat_solver_var_value(pSat, pCnf->

pVarNums[Aig_ObjId(pObj)]) )

169 Abc_InfoSetBit( pCex->pData, iBit + k );

170 iBit += Saig_ManPiNum(pAig);

171 assert( iBit == pCex->nBits );

172

173

174 Vec_IntFree( vAssumps );

177

178

180 if ( status >= 0 && status < Saig_ManPoNum(pAig) )

181 pCex->iPo = status;

182 else

183 {

184 printf( "Llb4_Nonlin4TransformCex(): Counter-example verification has FAILED.\n" );

186 return NULL;

187 }

188

189

190

191 return pCex;

192}

struct Aig_Obj_t_ Aig_Obj_t

typedefABC_NAMESPACE_IMPL_START struct Vec_Int_t_ Vec_Int_t

DECLARATIONS ///.

#define sat_solver_addclause

Cnf_Dat_t * Cnf_Derive(Aig_Man_t *pAig, int nOutputs)

struct Cnf_Dat_t_ Cnf_Dat_t

void Cnf_DataFree(Cnf_Dat_t *p)

void * Cnf_DataWriteIntoSolver(Cnf_Dat_t *p, int nFrames, int fInit)

#define Saig_ManForEachLi(p, pObj, i)

#define Saig_ManForEachPo(p, pObj, i)

int Saig_ManFindFailedPoCex(Aig_Man_t *pAig, Abc_Cex_t *p)

#define Saig_ManForEachLo(p, pObj, i)

#define Saig_ManForEachPi(p, pObj, i)

int sat_solver_simplify(sat_solver *s)

void sat_solver_delete(sat_solver *s)

ABC_NAMESPACE_IMPL_START Abc_Cex_t * Abc_CexAlloc(int nRegs, int nRealPis, int nFrames)

DECLARATIONS ///.

#define Vec_PtrForEachEntryStart(Type, vVec, pEntry, i, Start)