#include "rewire_map.h"

Go to the source code of this file.

|

extern |

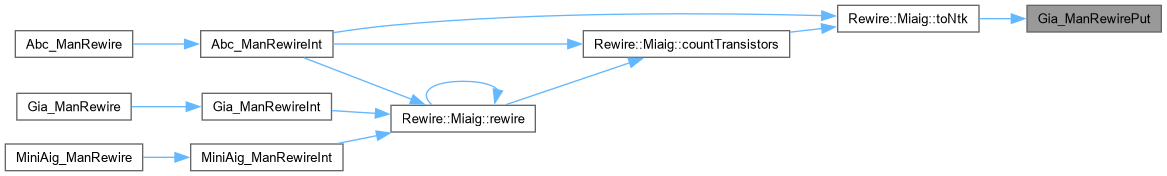

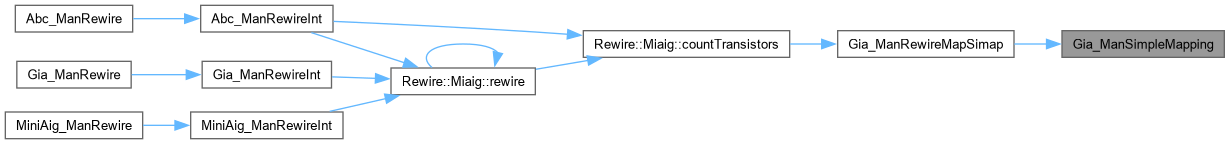

Definition at line 60 of file mainFrame.c.

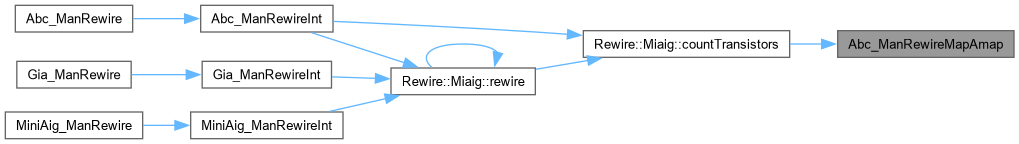

Definition at line 46 of file rewire_map.c.

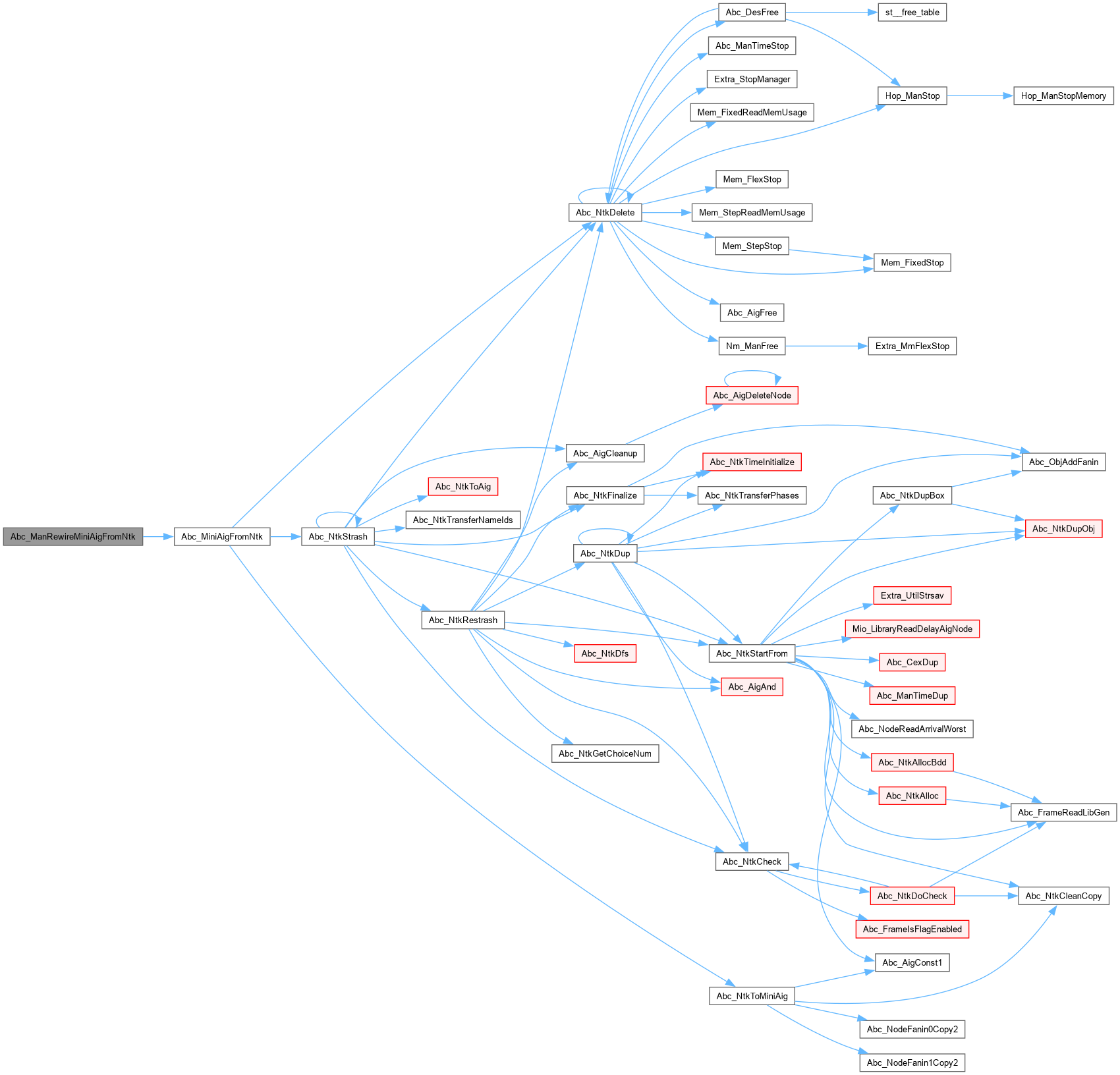

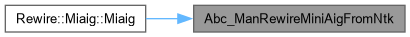

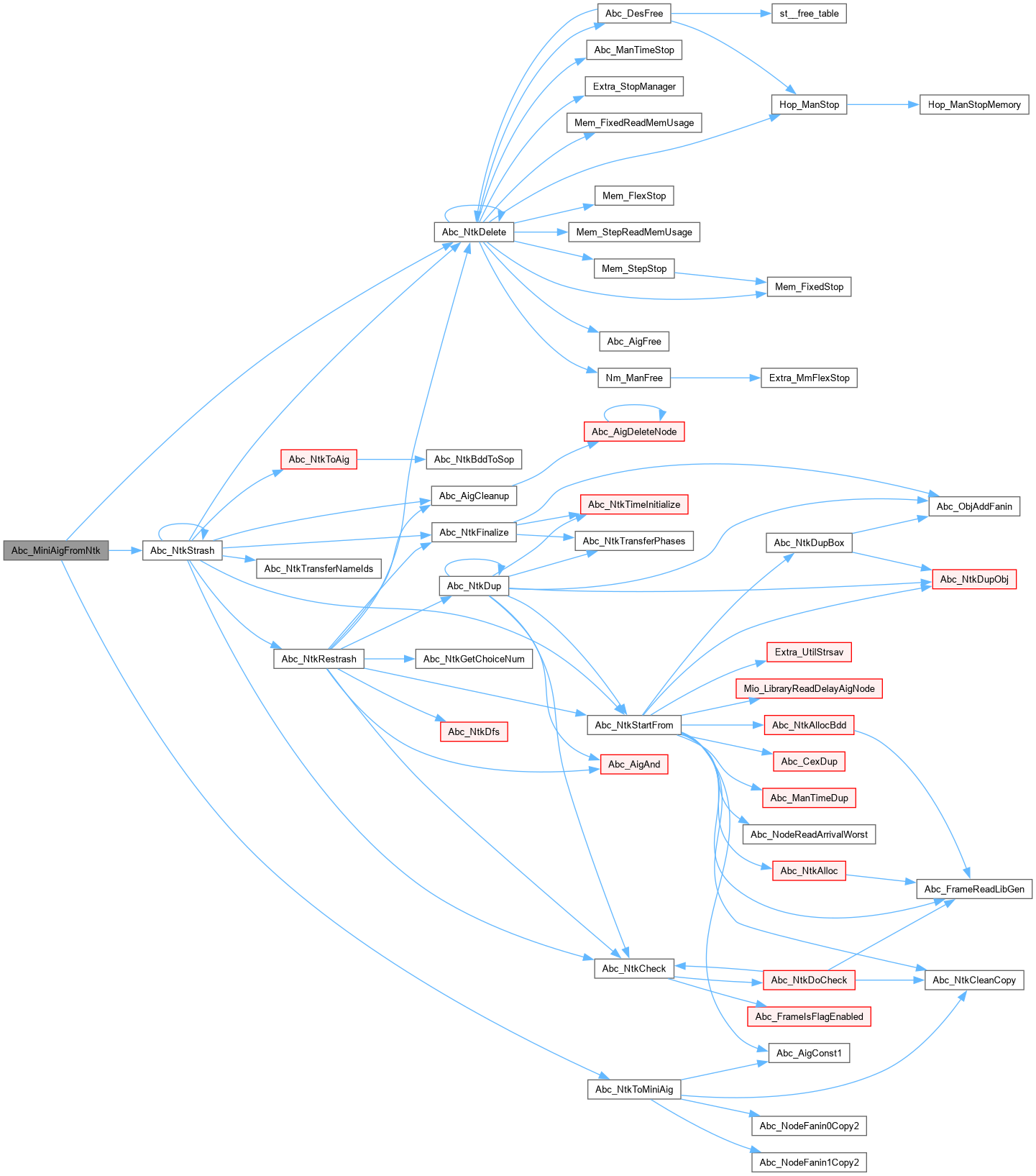

| Mini_Aig_t * Abc_ManRewireMiniAigFromNtk | ( | Abc_Ntk_t * | pNtk | ) |

Definition at line 86 of file rewire_map.c.

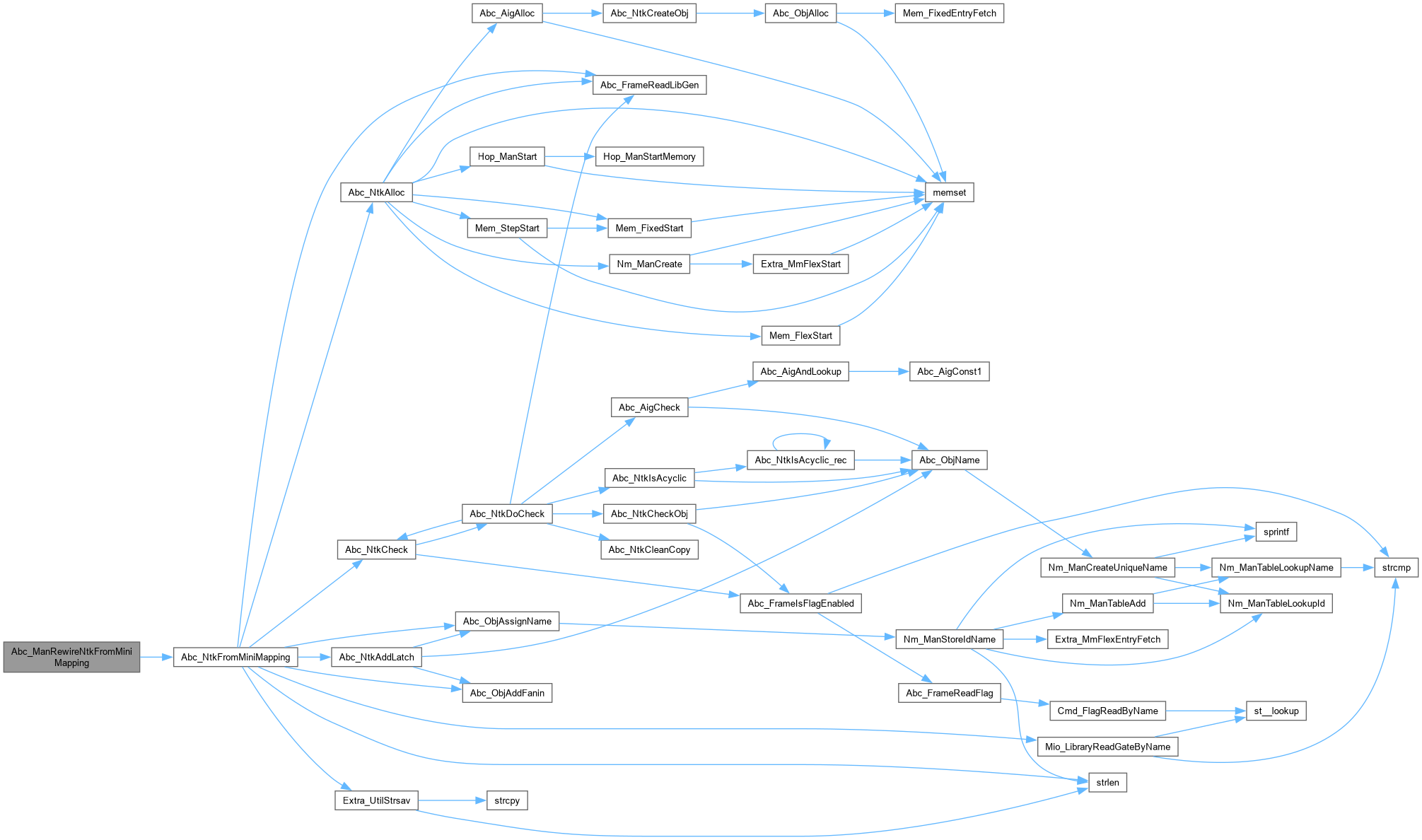

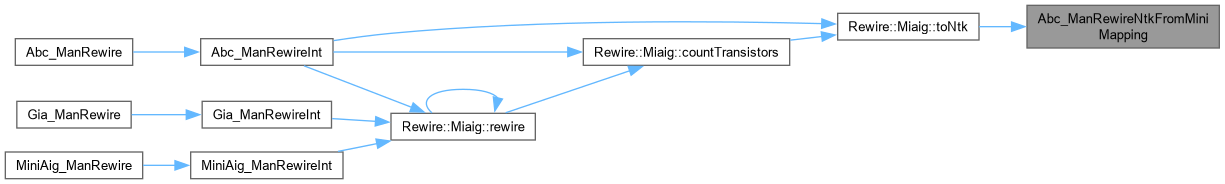

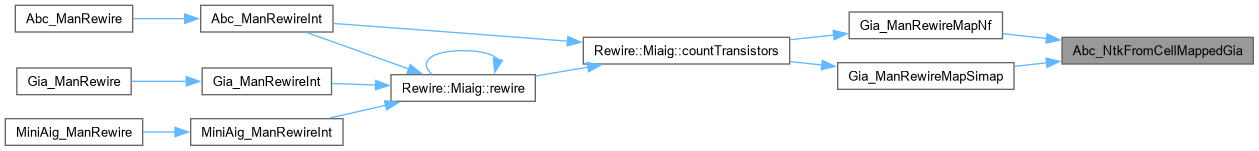

| Abc_Ntk_t * Abc_ManRewireNtkFromMiniMapping | ( | int * | vMapping | ) |

Definition at line 82 of file rewire_map.c.

Definition at line 78 of file rewire_map.c.

|

extern |

Definition at line 147 of file abcMini.c.

|

extern |

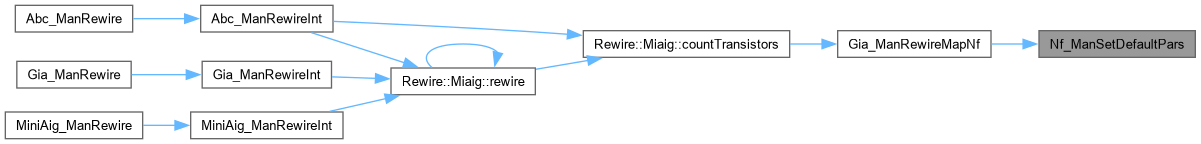

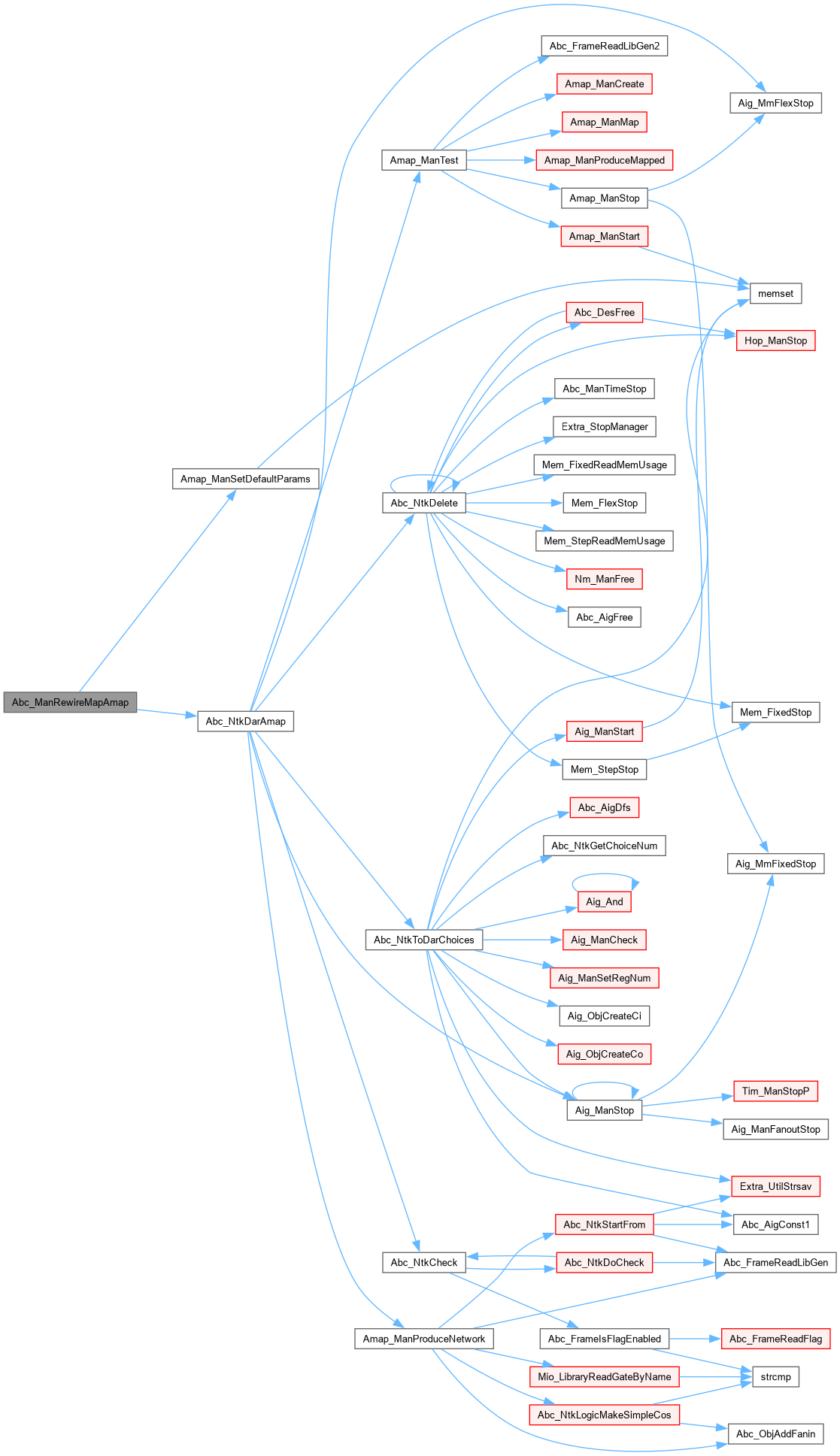

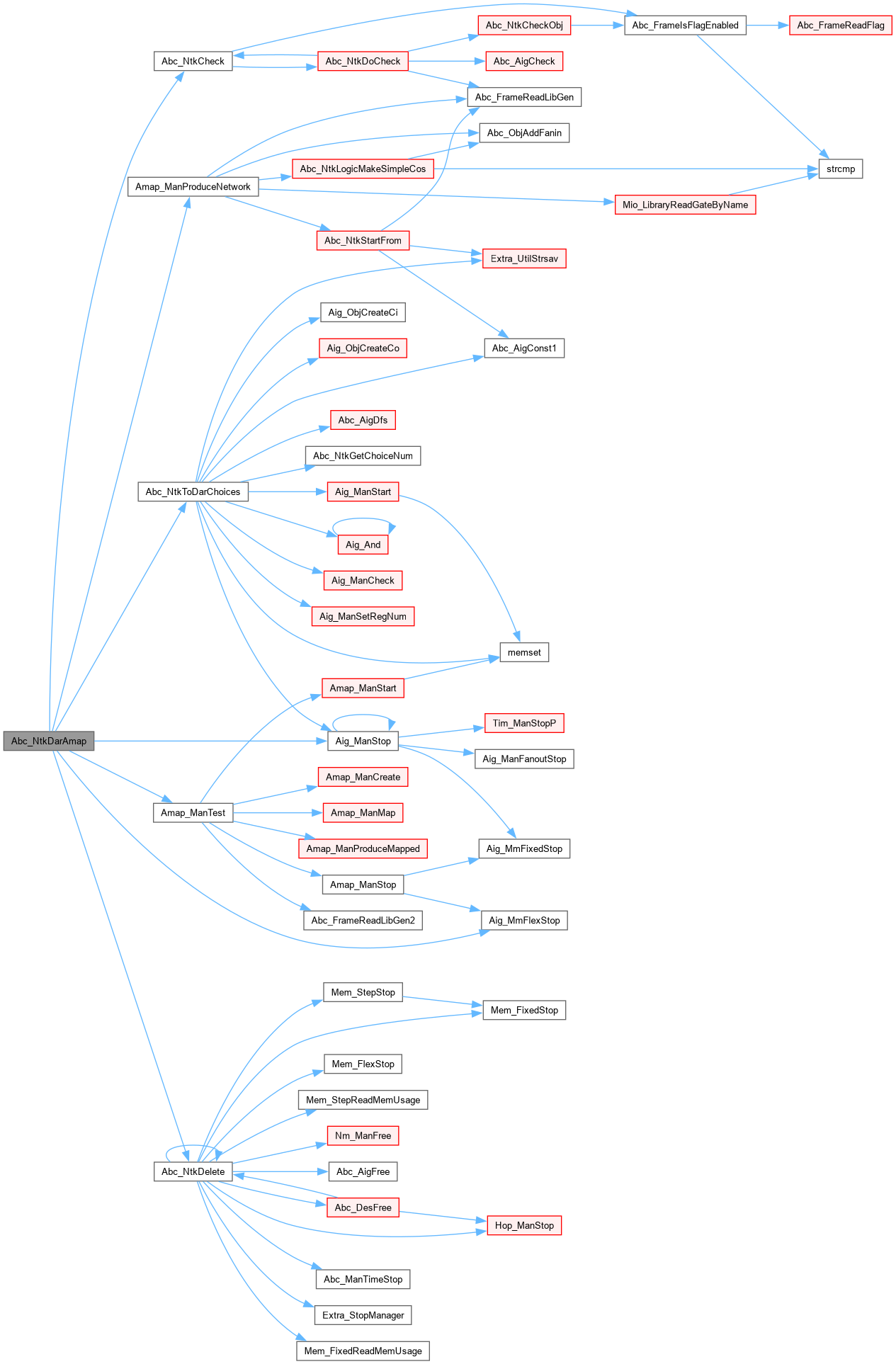

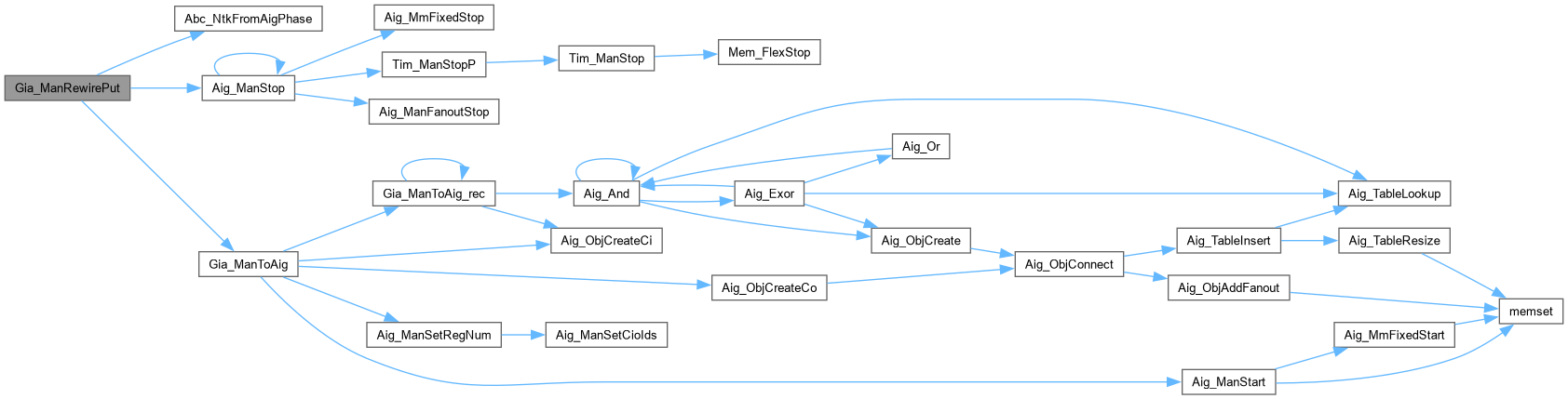

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 4558 of file abcDar.c.

|

extern |

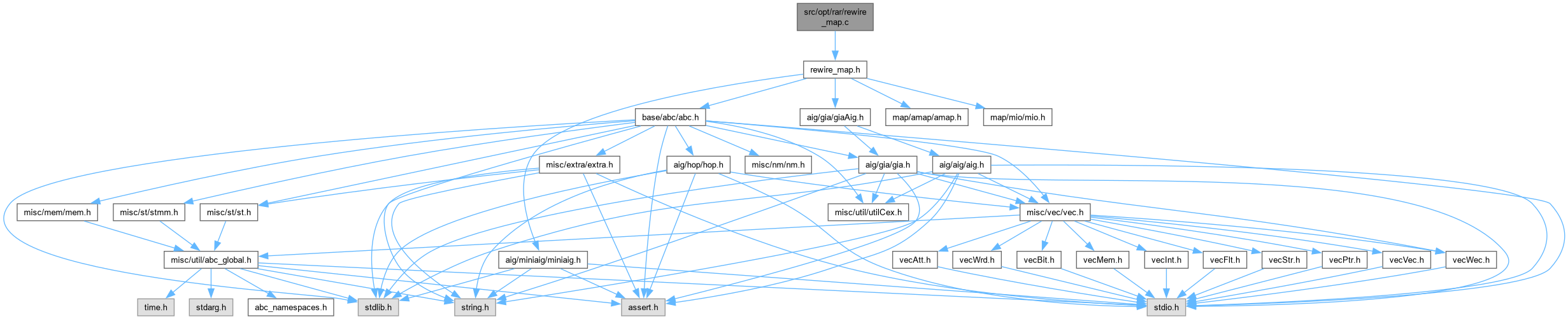

DECLARATIONS ///.

CFile****************************************************************

FileName [rewire_map.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Re-wiring.]

Synopsis []

Author [Jiun-Hao Chen]

Affiliation [National Taiwan University]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

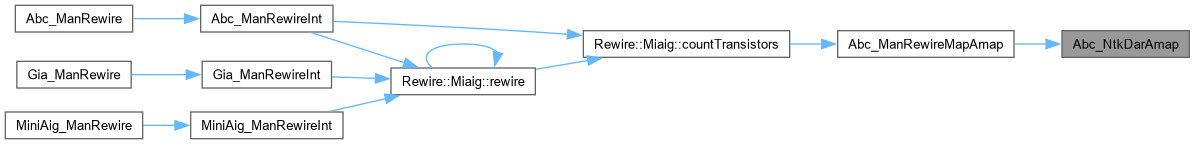

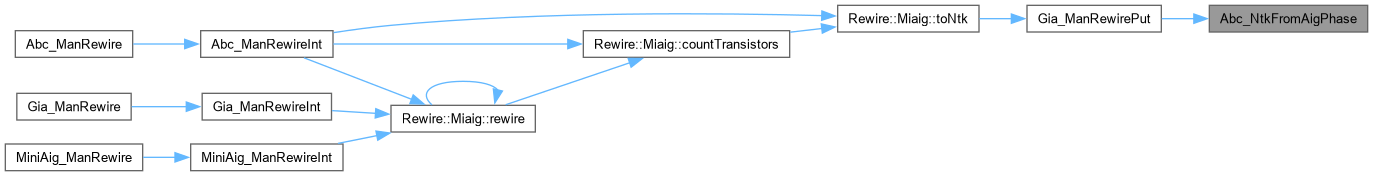

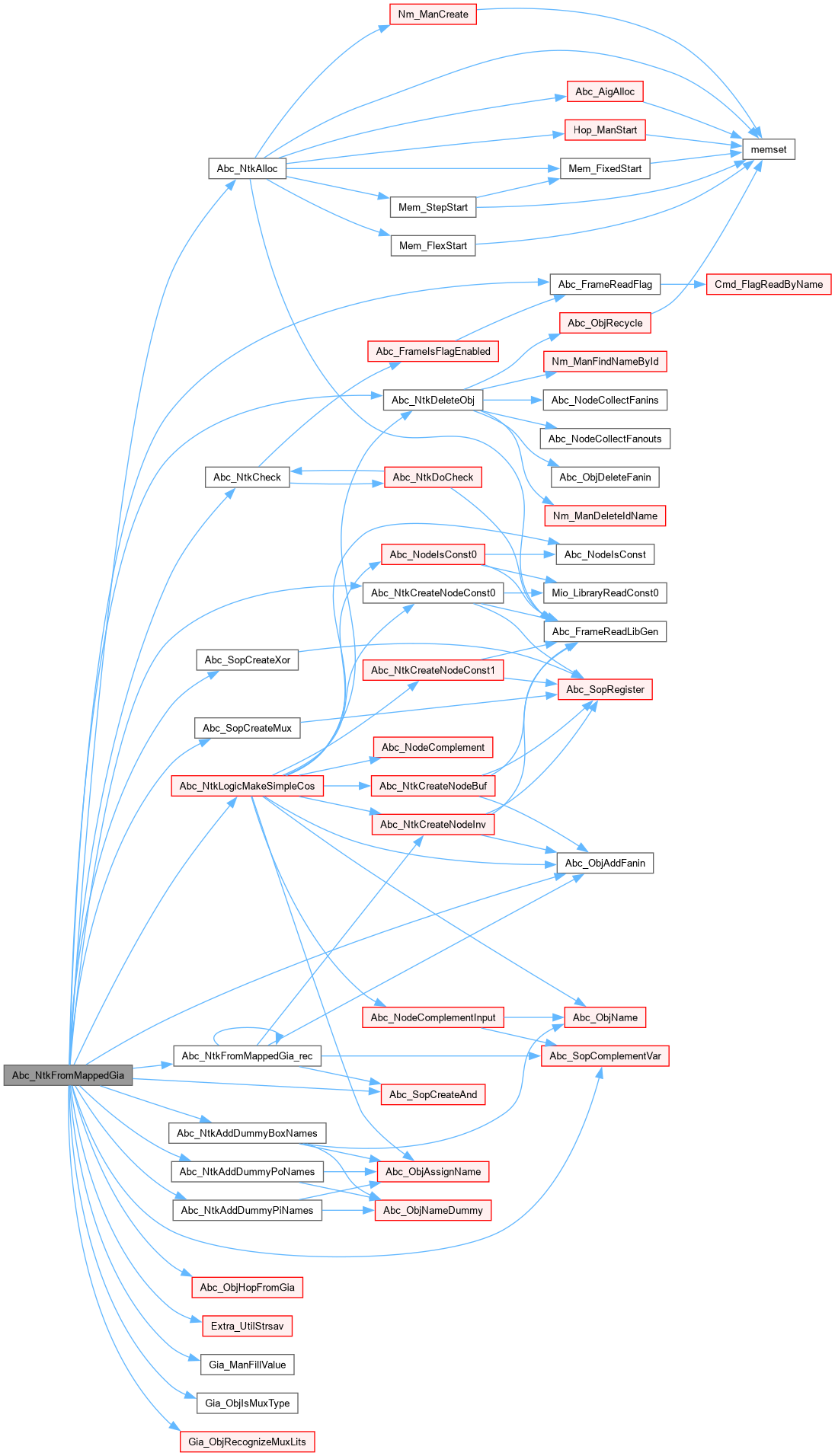

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [This procedure should be called after seq sweeping, which changes the number of registers.]

SideEffects []

SeeAlso []

Definition at line 595 of file abcDar.c.

Definition at line 967 of file abcDar.c.

Definition at line 768 of file abcDar.c.

|

extern |

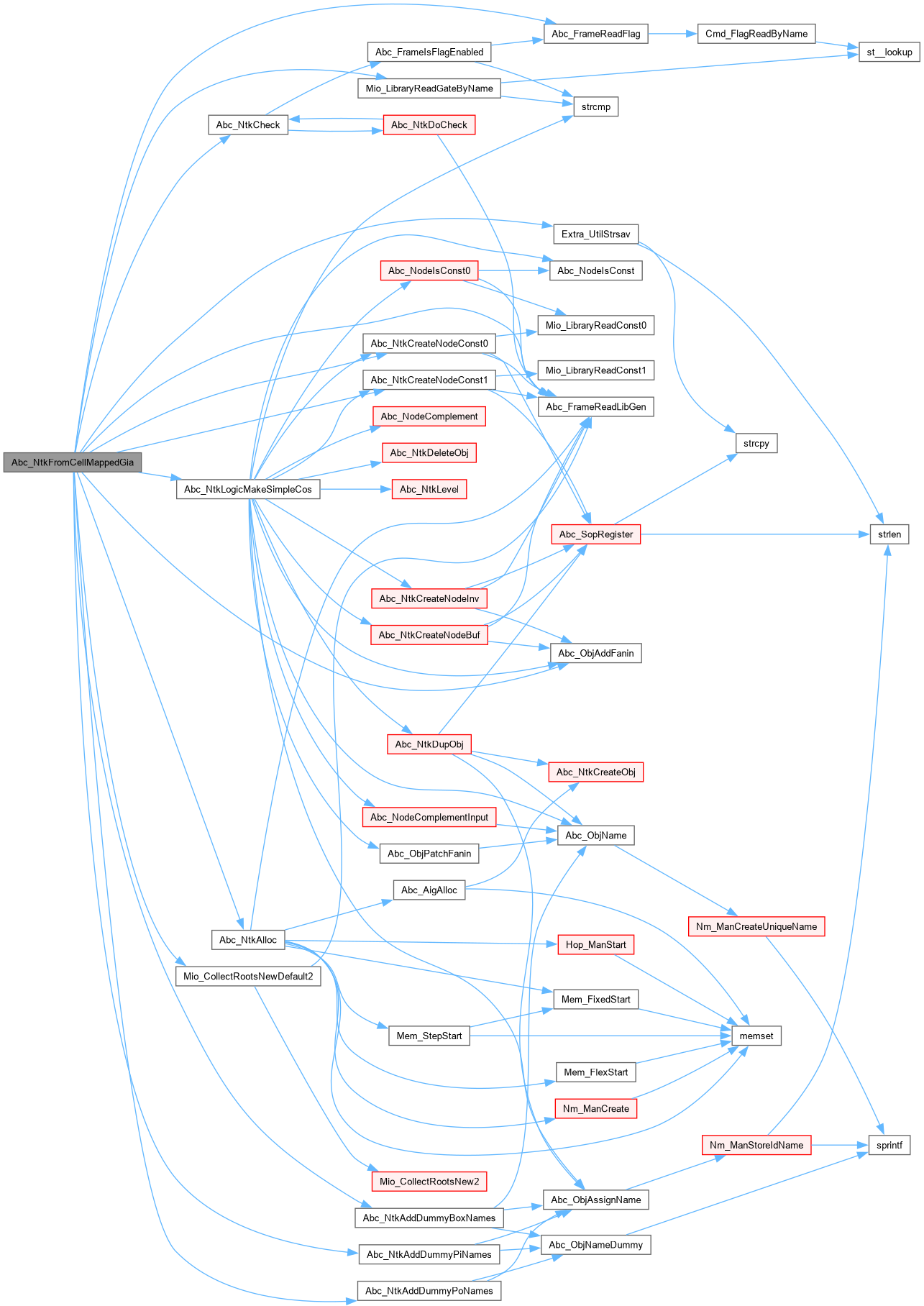

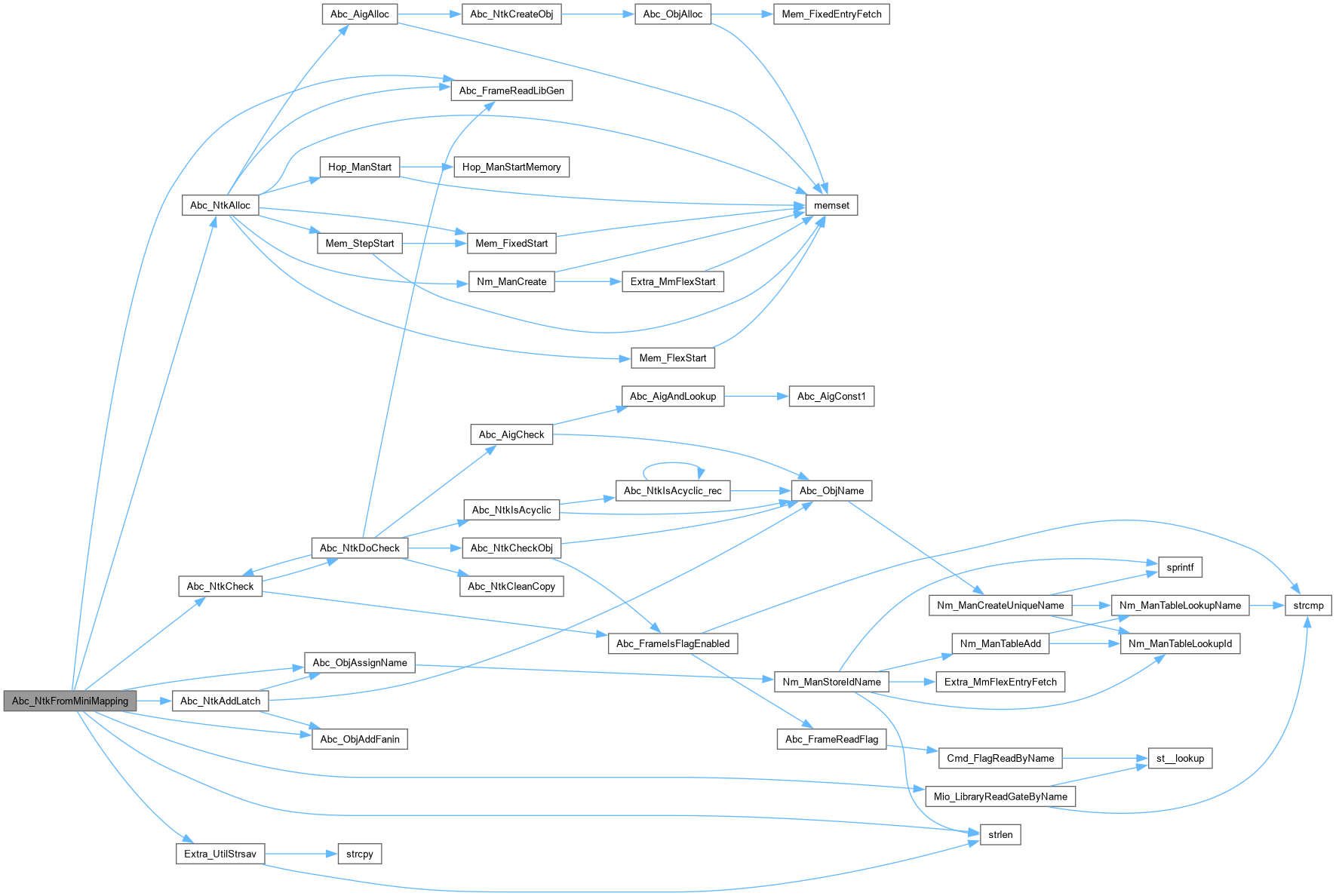

Function*************************************************************

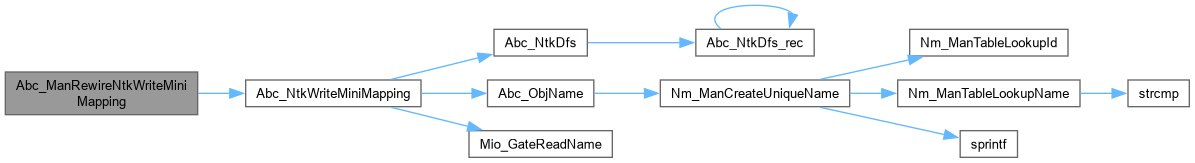

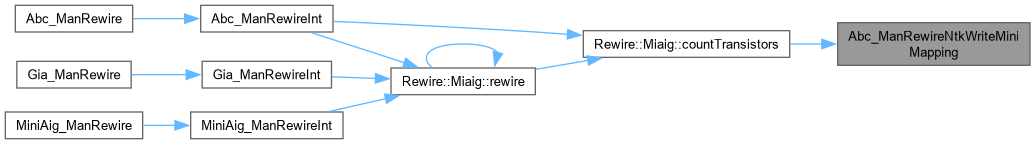

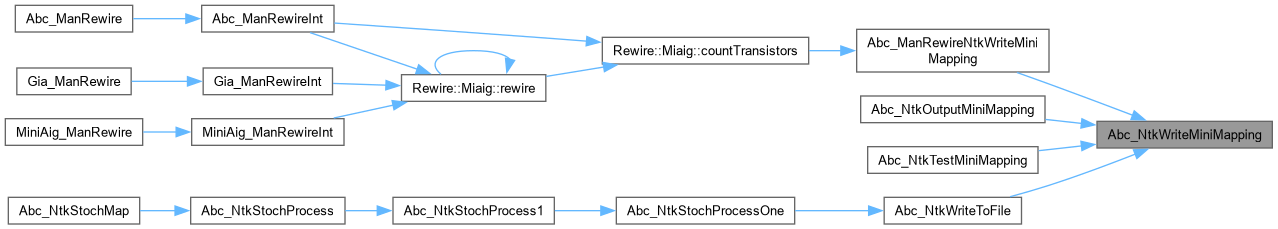

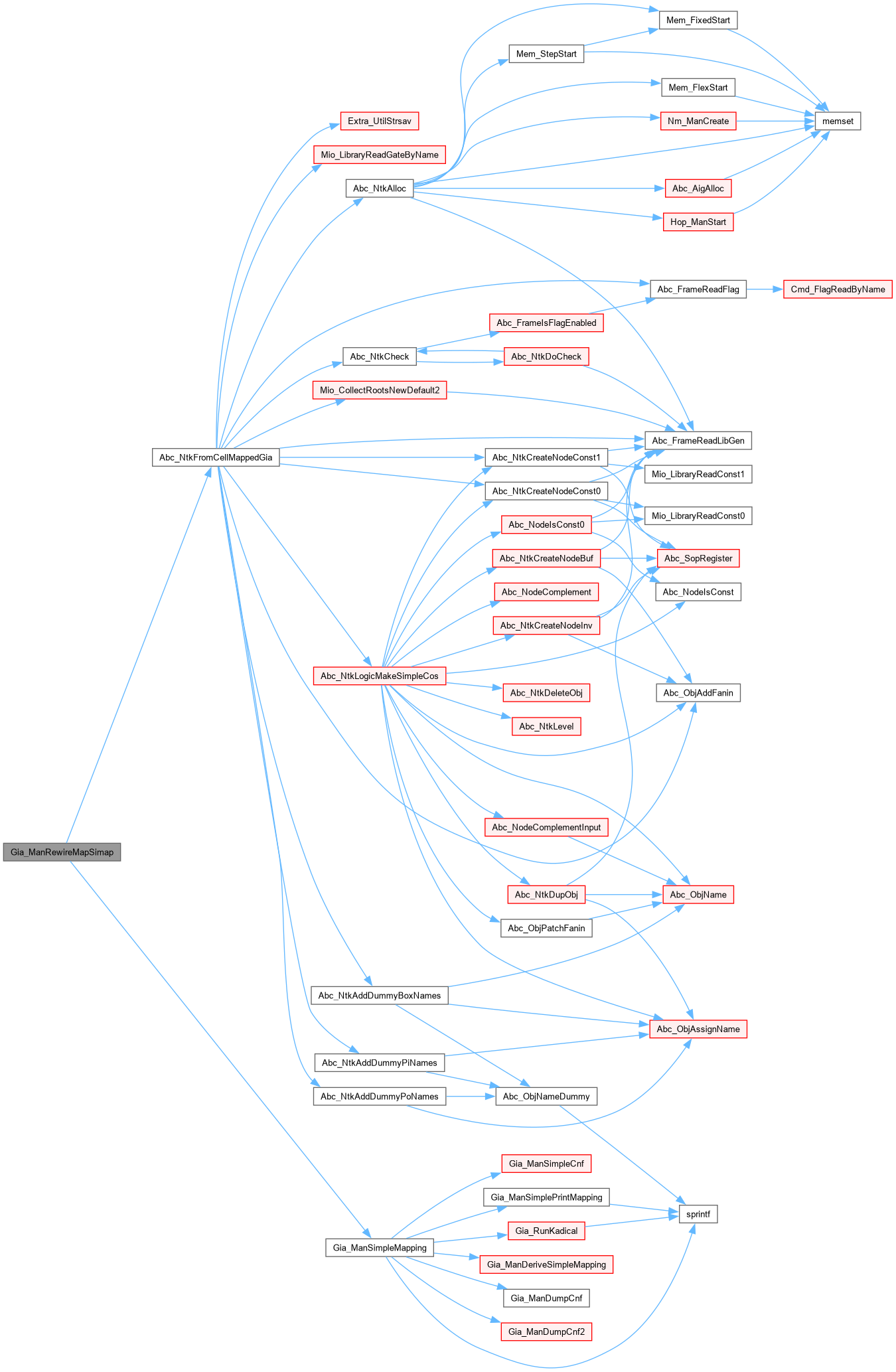

Synopsis [Build mapped network from the mini-mapped format.]

Description []

SideEffects []

SeeAlso []

Definition at line 907 of file abcMap.c.

|

extern |

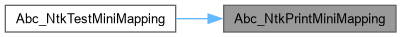

Function*************************************************************

Synopsis [Prints mapped network represented in mini-mapped format.]

Description []

SideEffects []

SeeAlso []

Definition at line 1030 of file abcMap.c.

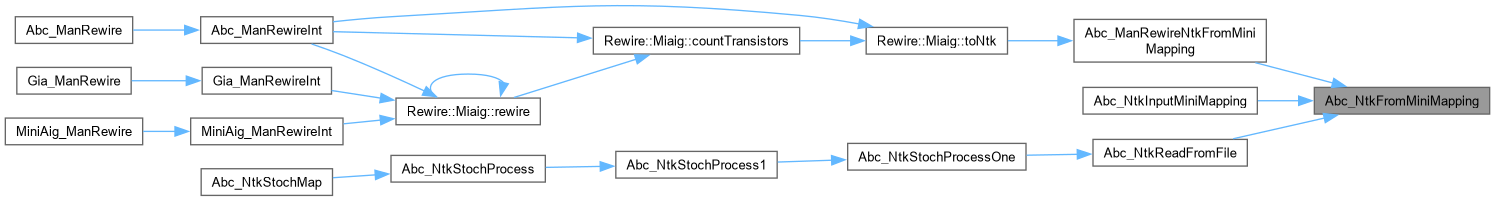

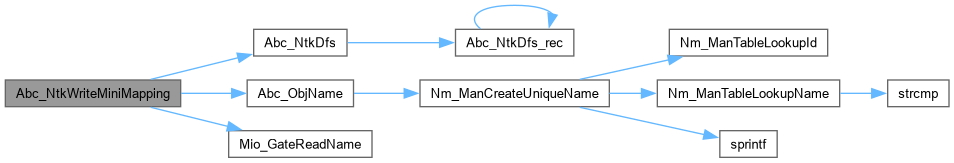

Function*************************************************************

Synopsis [Dumps mapped network in the mini-mapped format.]

Description []

SideEffects []

SeeAlso []

Definition at line 834 of file abcMap.c.

Definition at line 57 of file rewire_map.c.

Definition at line 69 of file rewire_map.c.

CFile****************************************************************

FileName [rewire_map.h]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Re-wiring.]

Synopsis []

Author [Jiun-Hao Chen]

Affiliation [National Taiwan University]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

]

Definition at line 38 of file rewire_map.c.

|

extern |

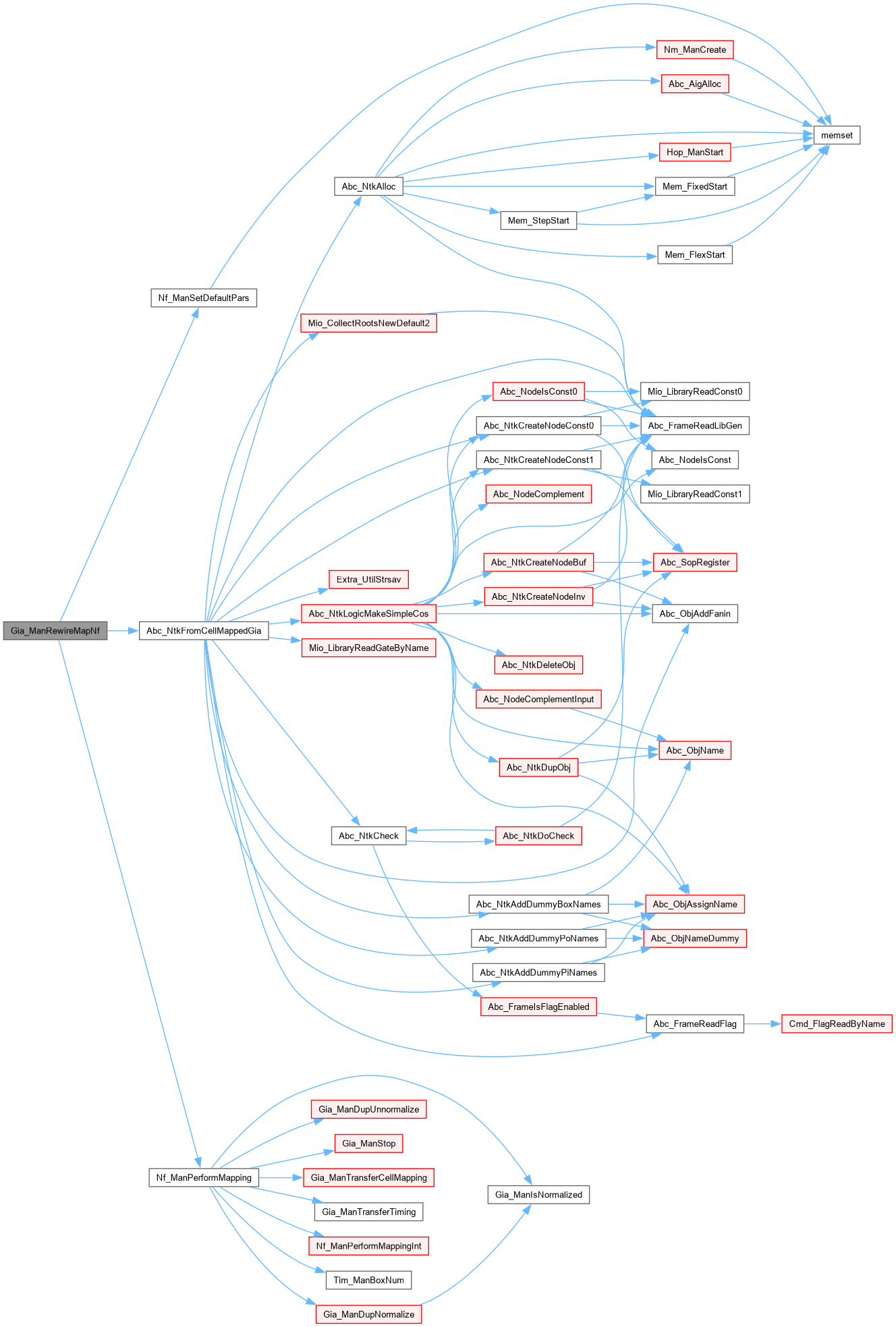

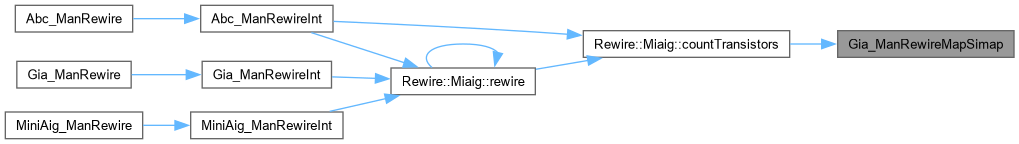

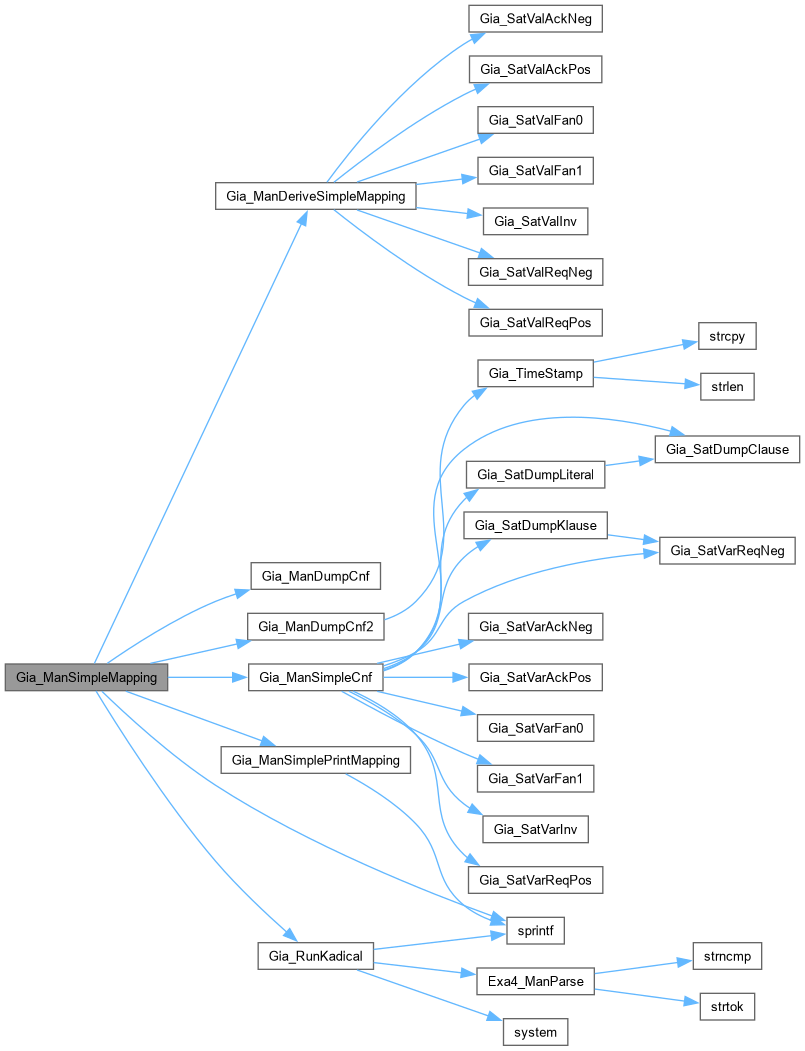

Definition at line 1572 of file giaSatLut.c.

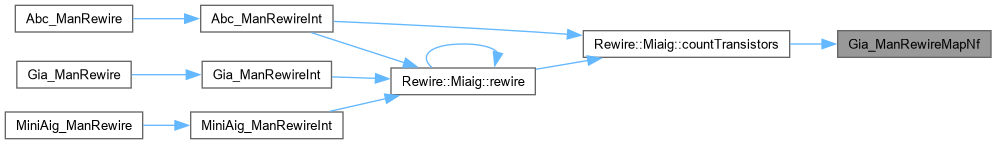

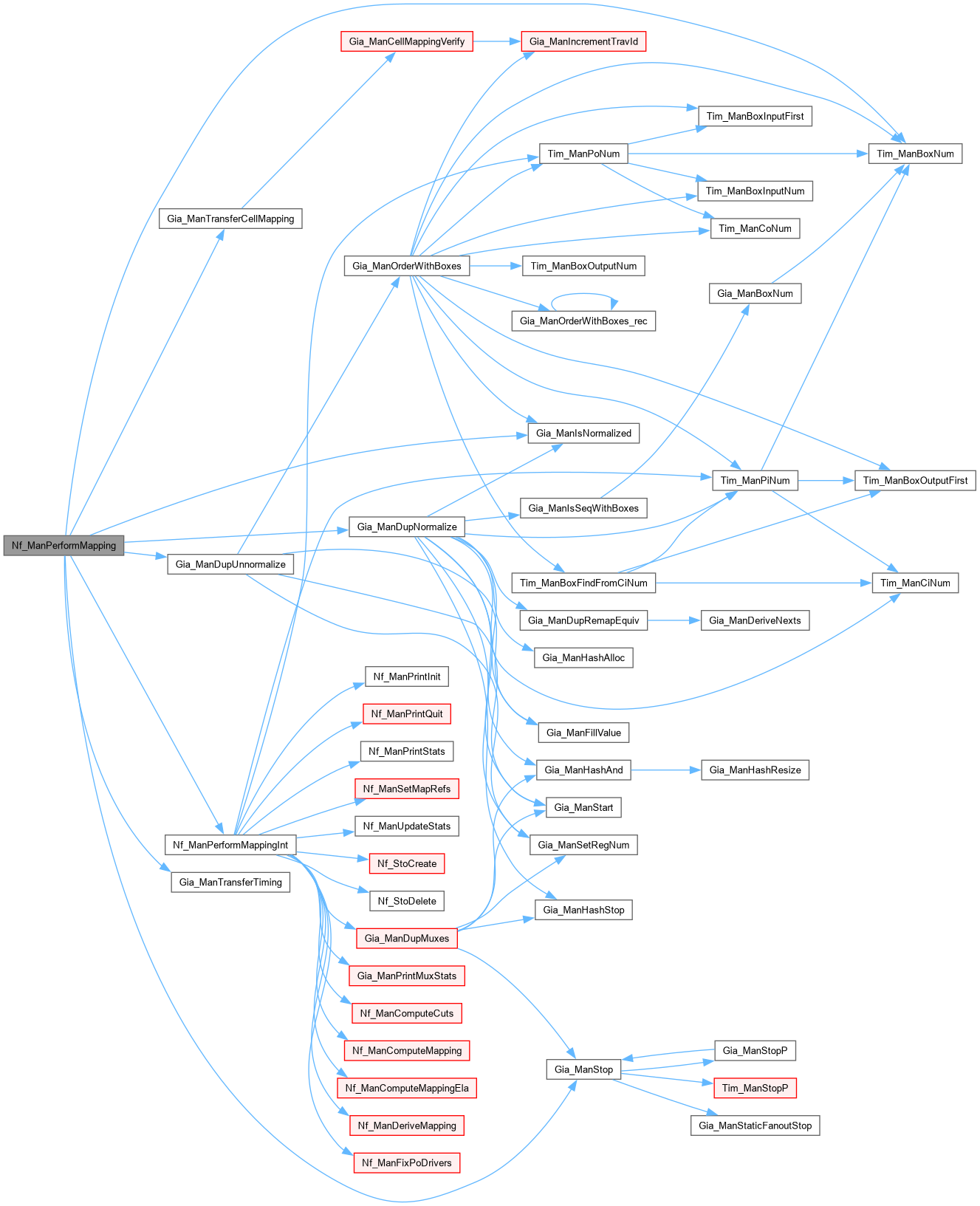

Definition at line 2734 of file giaNf.c.

|

extern |

Function*************************************************************

Synopsis [Technology mappping.]

Description []

SideEffects []

SeeAlso []

Definition at line 2527 of file giaNf.c.