#include "base/abc/abc.h"#include "base/main/main.h"#include "aig/gia/giaAig.h"#include "opt/dar/dar.h"#include "sat/cnf/cnf.h"#include "proof/fra/fra.h"#include "proof/fraig/fraig.h"#include "proof/int/int.h"#include "proof/dch/dch.h"#include "proof/ssw/ssw.h"#include "opt/cgt/cgt.h"#include "bdd/bbr/bbr.h"#include "aig/gia/gia.h"#include "proof/cec/cec.h"#include "opt/csw/csw.h"#include "proof/pdr/pdr.h"#include "sat/bmc/bmc.h"#include "map/mio/mio.h"#include "misc/vec/vecMem.h"#include "map/amap/amap.h"#include "abcDarUnfold2.c"

Go to the source code of this file.

Functions | |

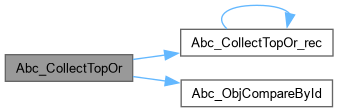

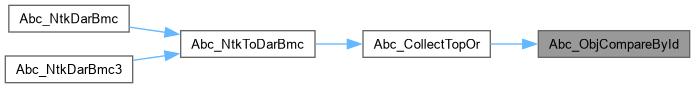

| ABC_NAMESPACE_IMPL_START int | Abc_ObjCompareById (Abc_Obj_t **pp1, Abc_Obj_t **pp2) |

| DECLARATIONS ///. | |

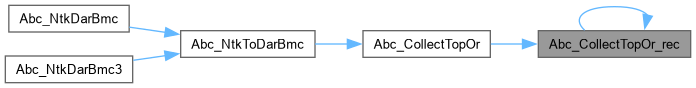

| void | Abc_CollectTopOr_rec (Abc_Obj_t *pObj, Vec_Ptr_t *vSuper) |

| void | Abc_CollectTopOr (Abc_Obj_t *pObj, Vec_Ptr_t *vSuper) |

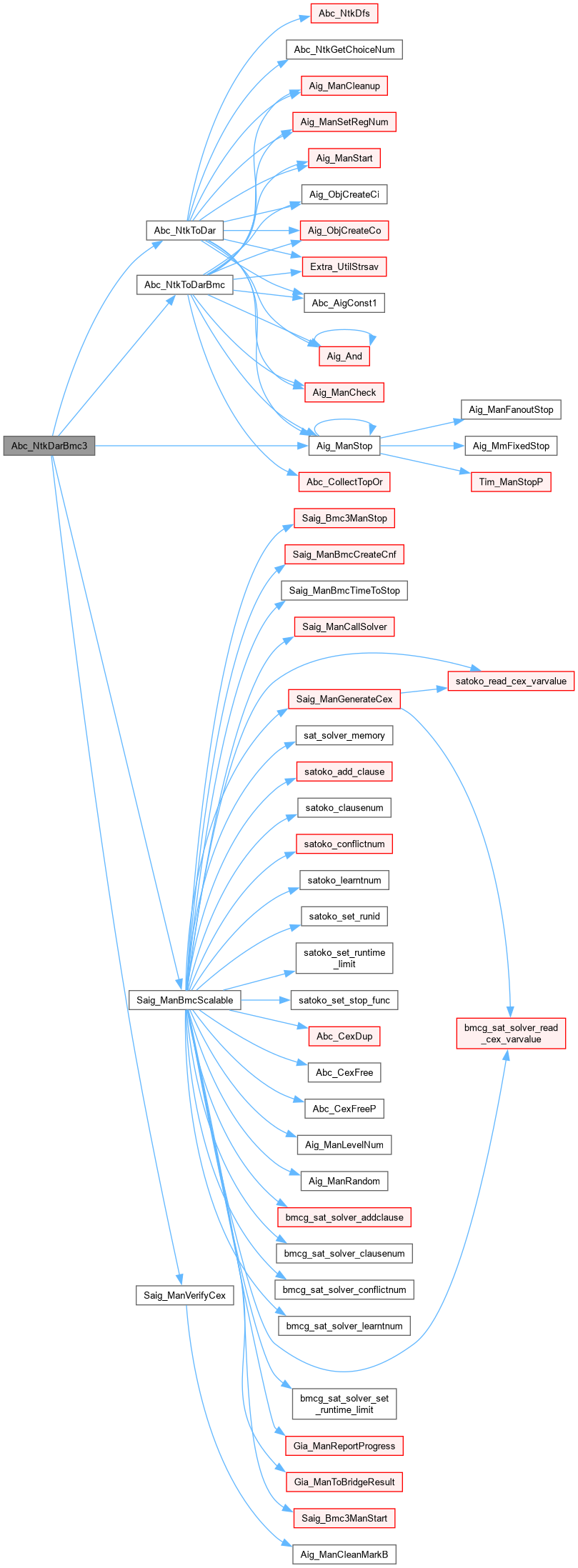

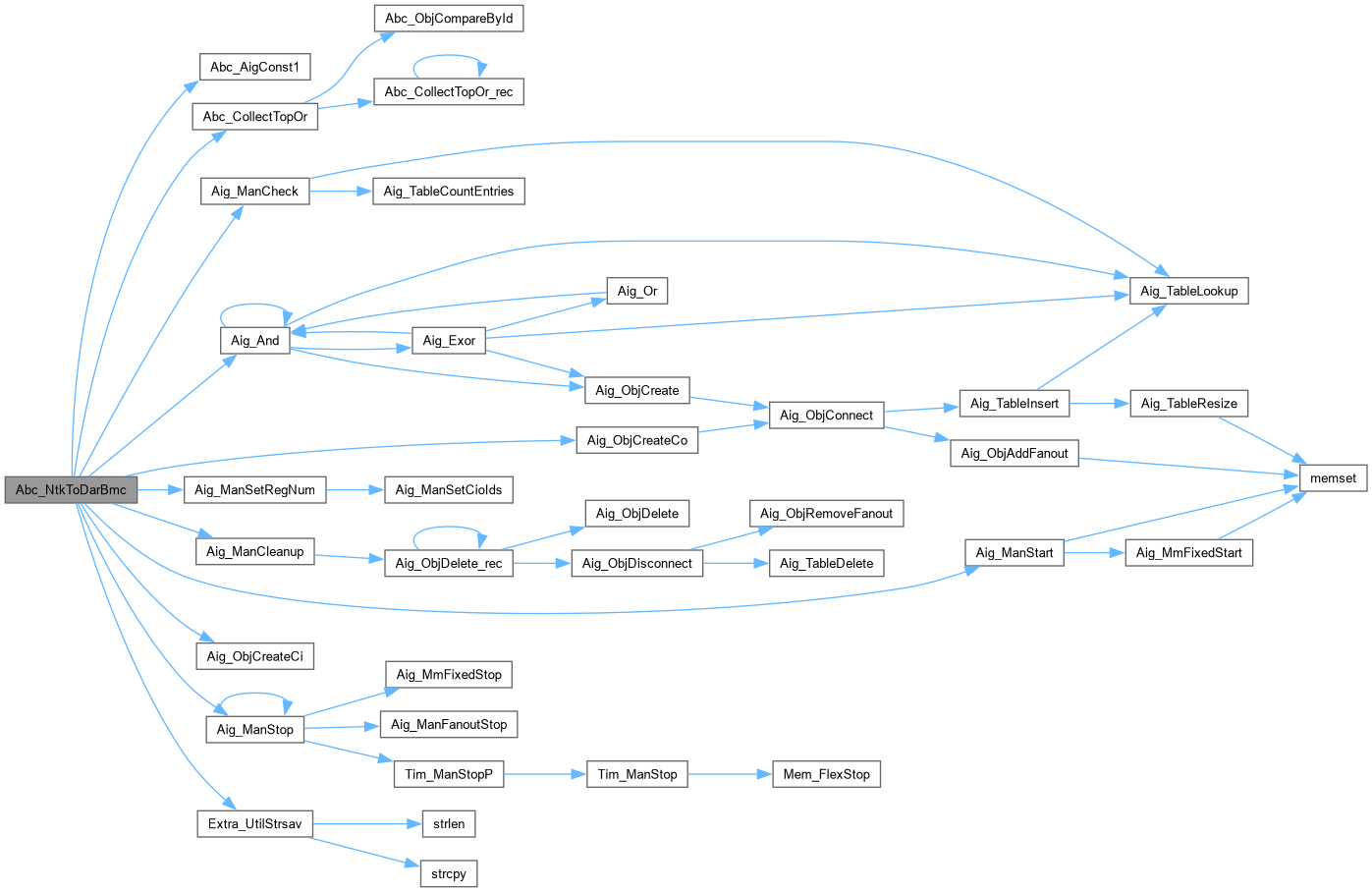

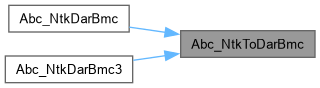

| Aig_Man_t * | Abc_NtkToDarBmc (Abc_Ntk_t *pNtk, Vec_Int_t **pvMap) |

| Vec_Int_t * | Abc_NtkFindDcLatches (Abc_Ntk_t *pNtk) |

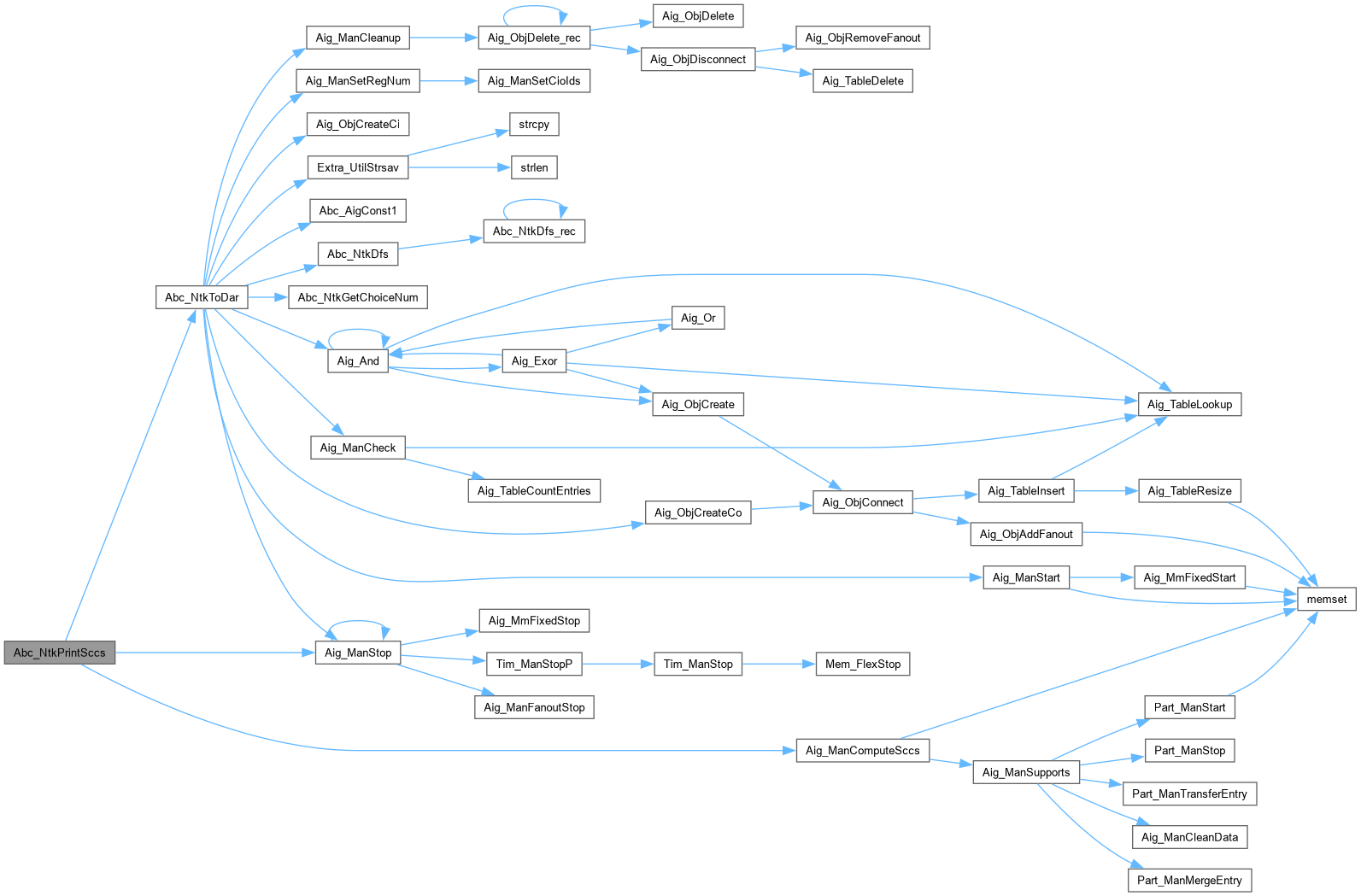

| Aig_Man_t * | Abc_NtkToDar (Abc_Ntk_t *pNtk, int fExors, int fRegisters) |

| DECLARATIONS ///. | |

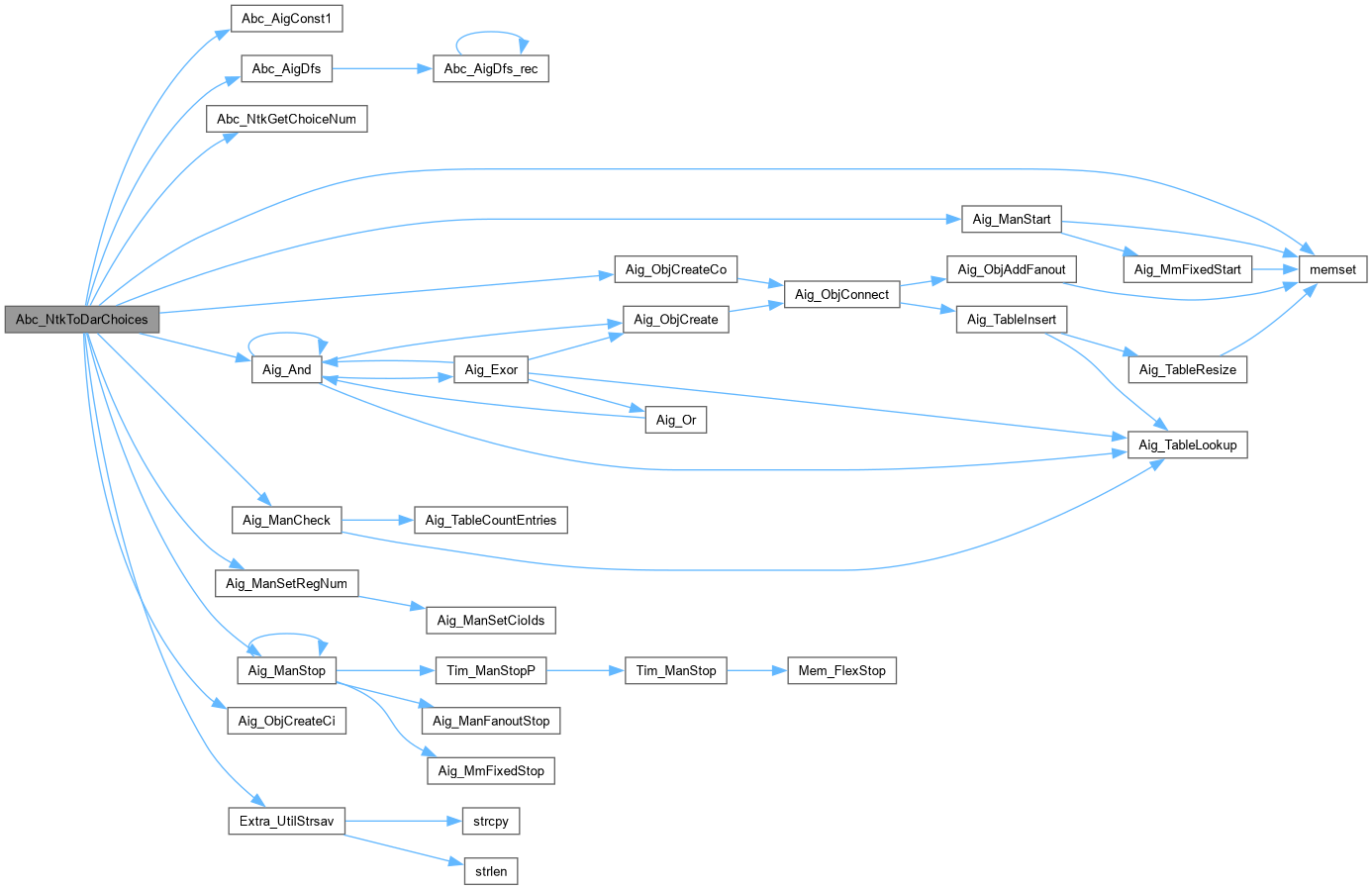

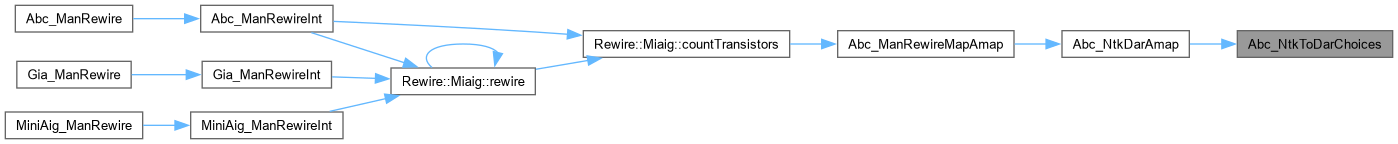

| Aig_Man_t * | Abc_NtkToDarChoices (Abc_Ntk_t *pNtk) |

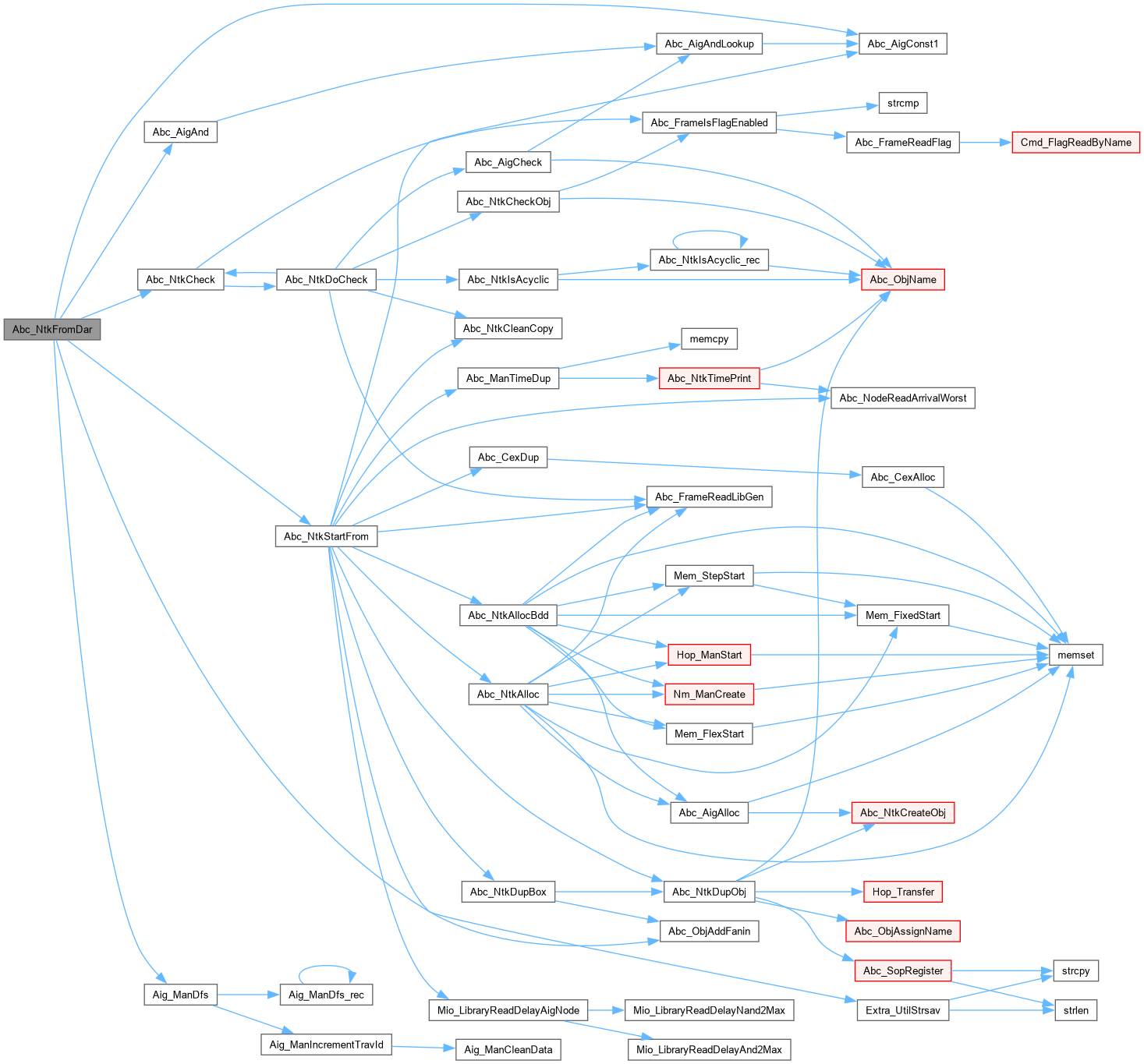

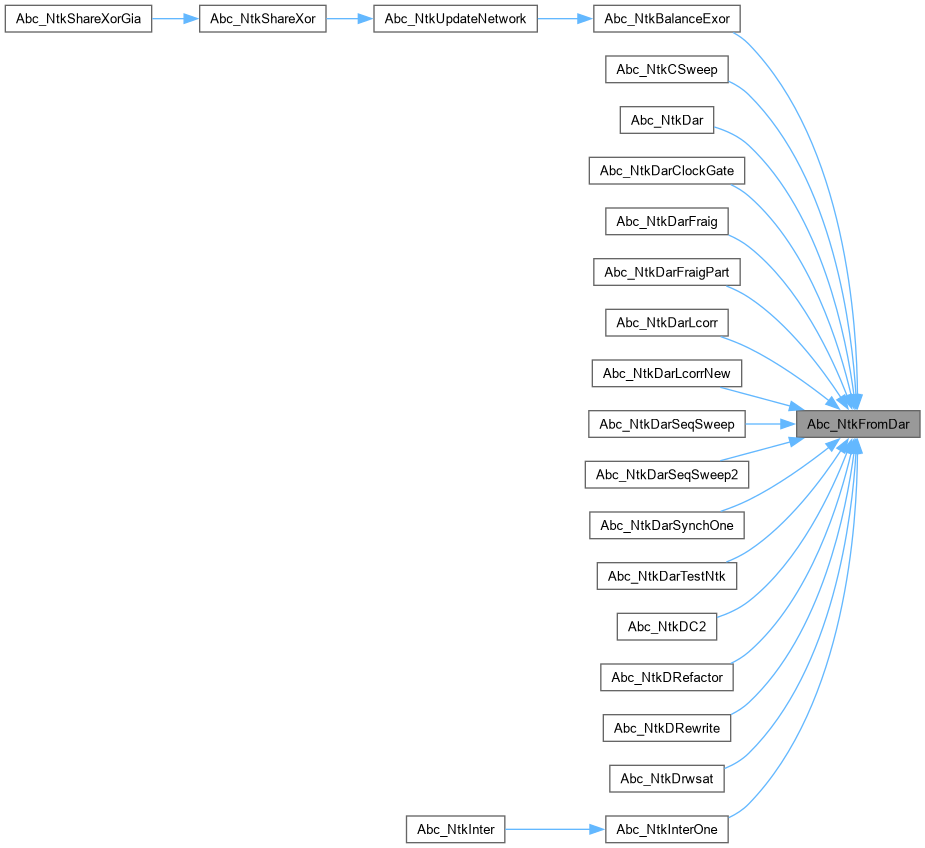

| Abc_Ntk_t * | Abc_NtkFromDar (Abc_Ntk_t *pNtkOld, Aig_Man_t *pMan) |

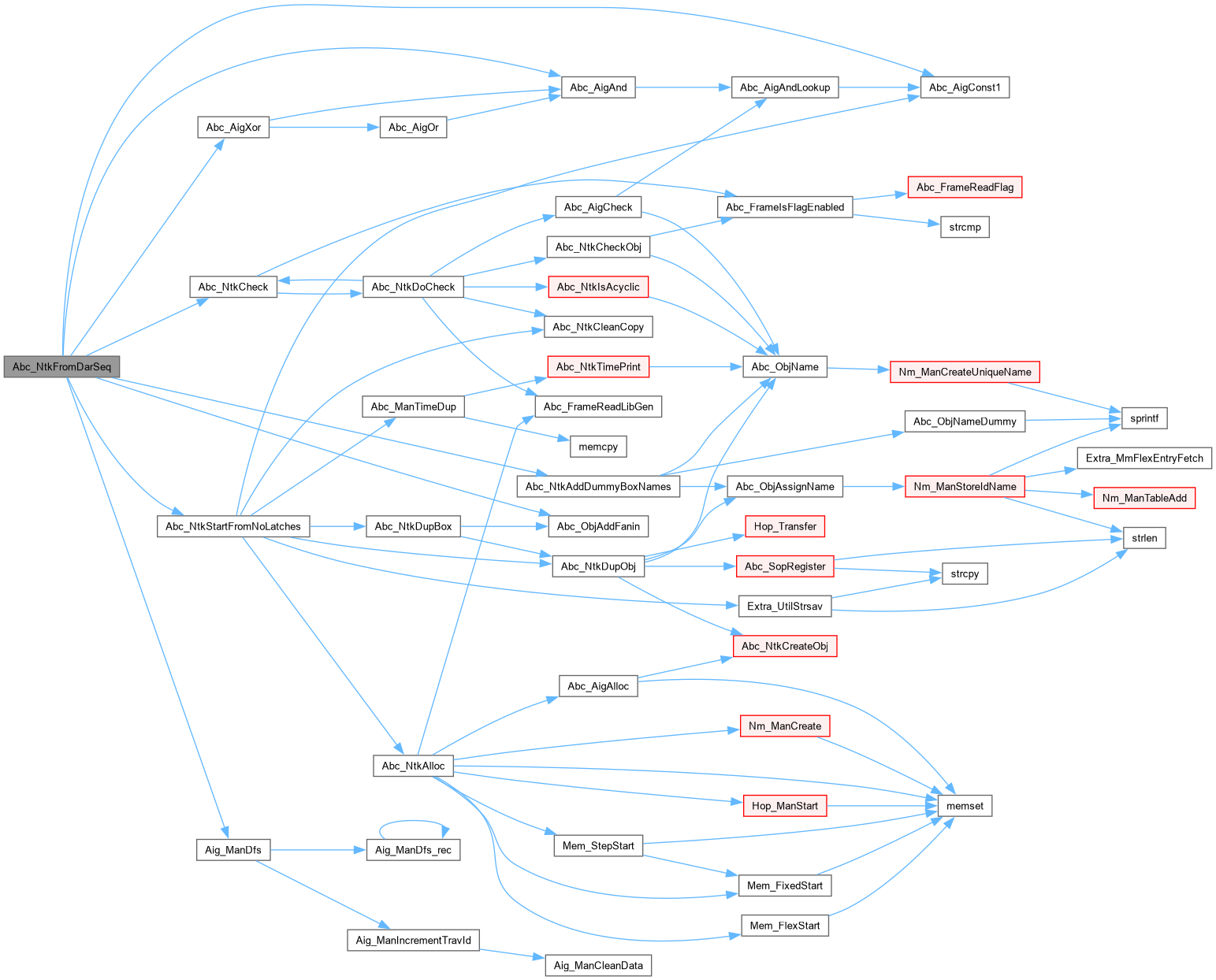

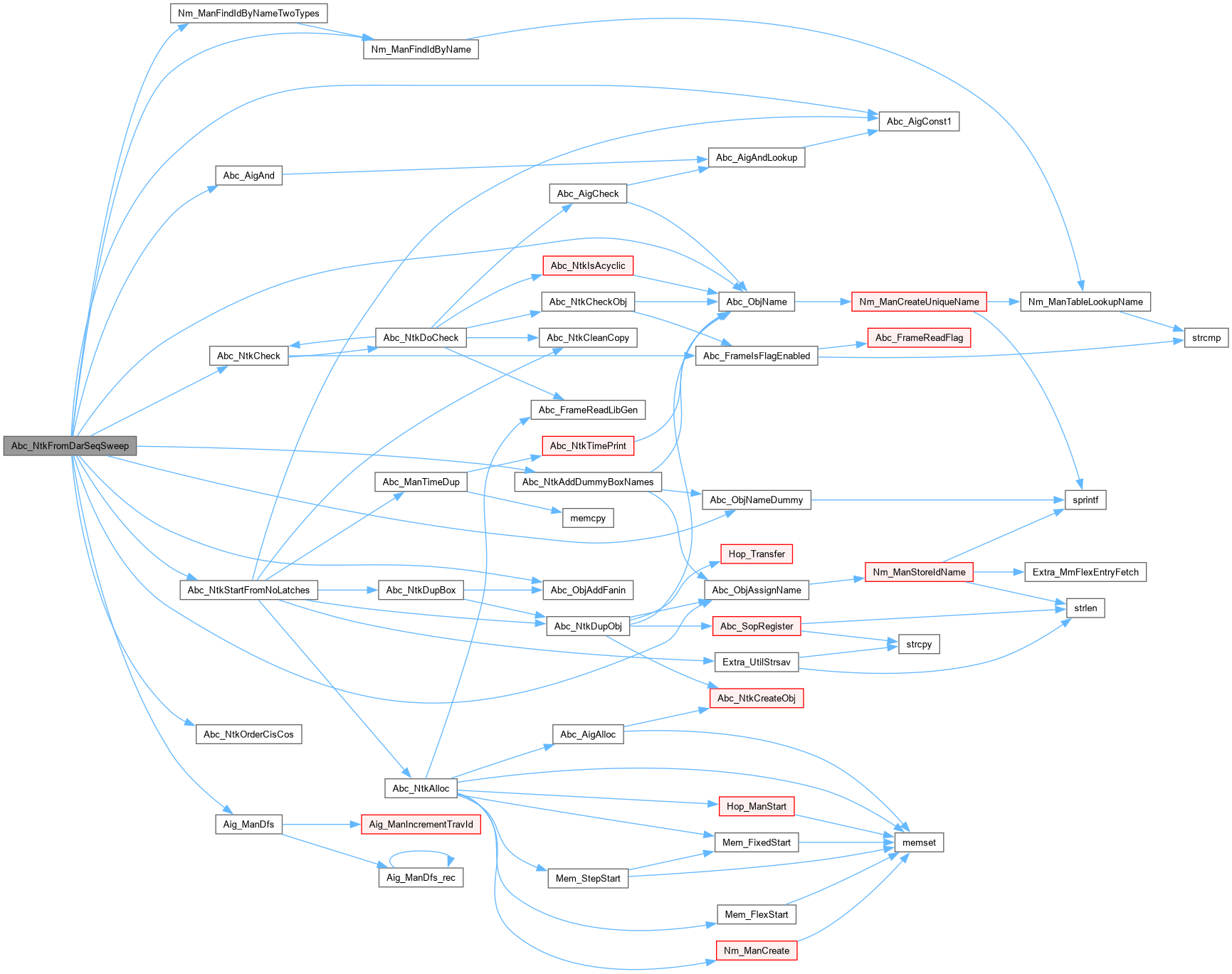

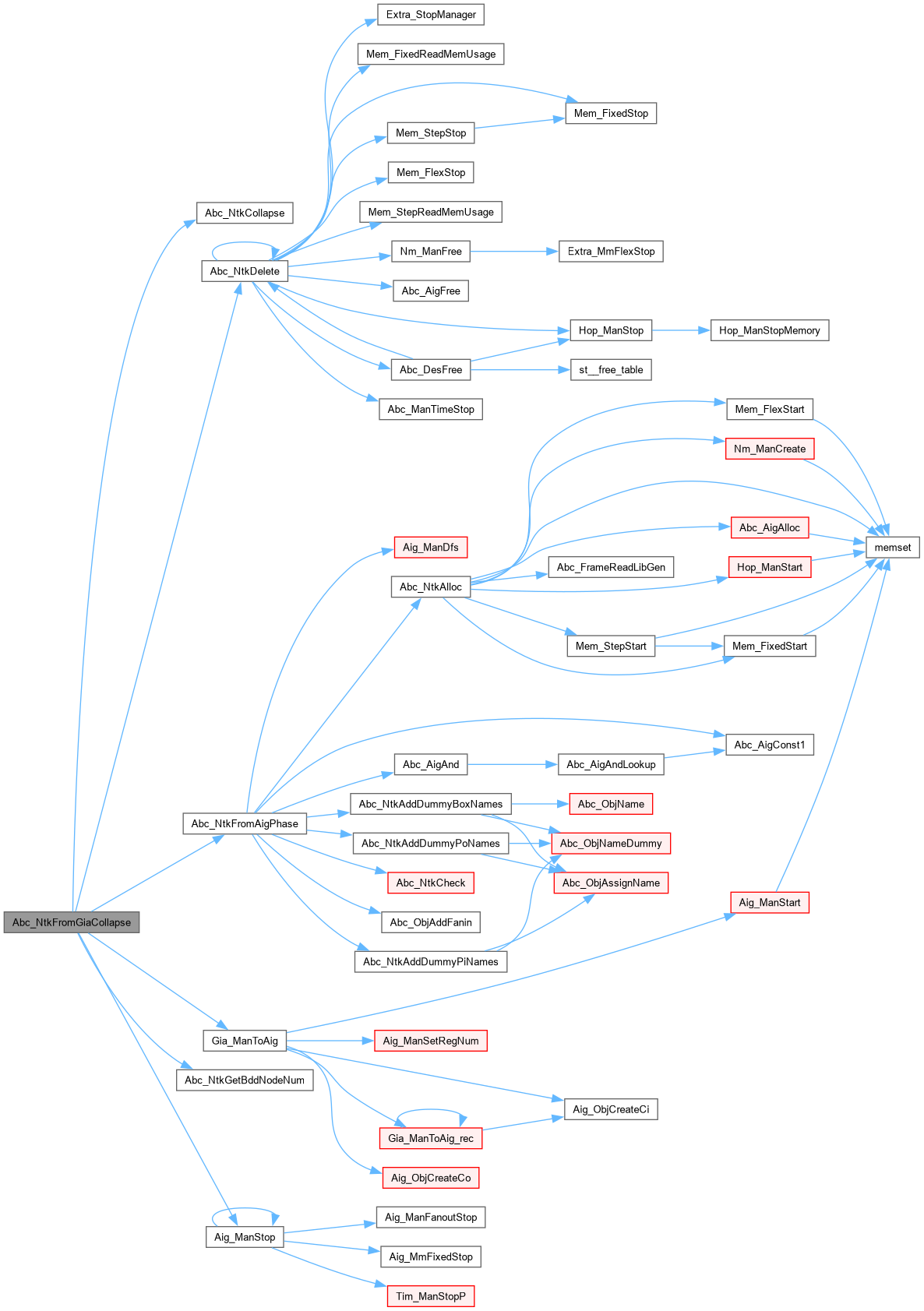

| Abc_Ntk_t * | Abc_NtkFromDarSeqSweep (Abc_Ntk_t *pNtkOld, Aig_Man_t *pMan) |

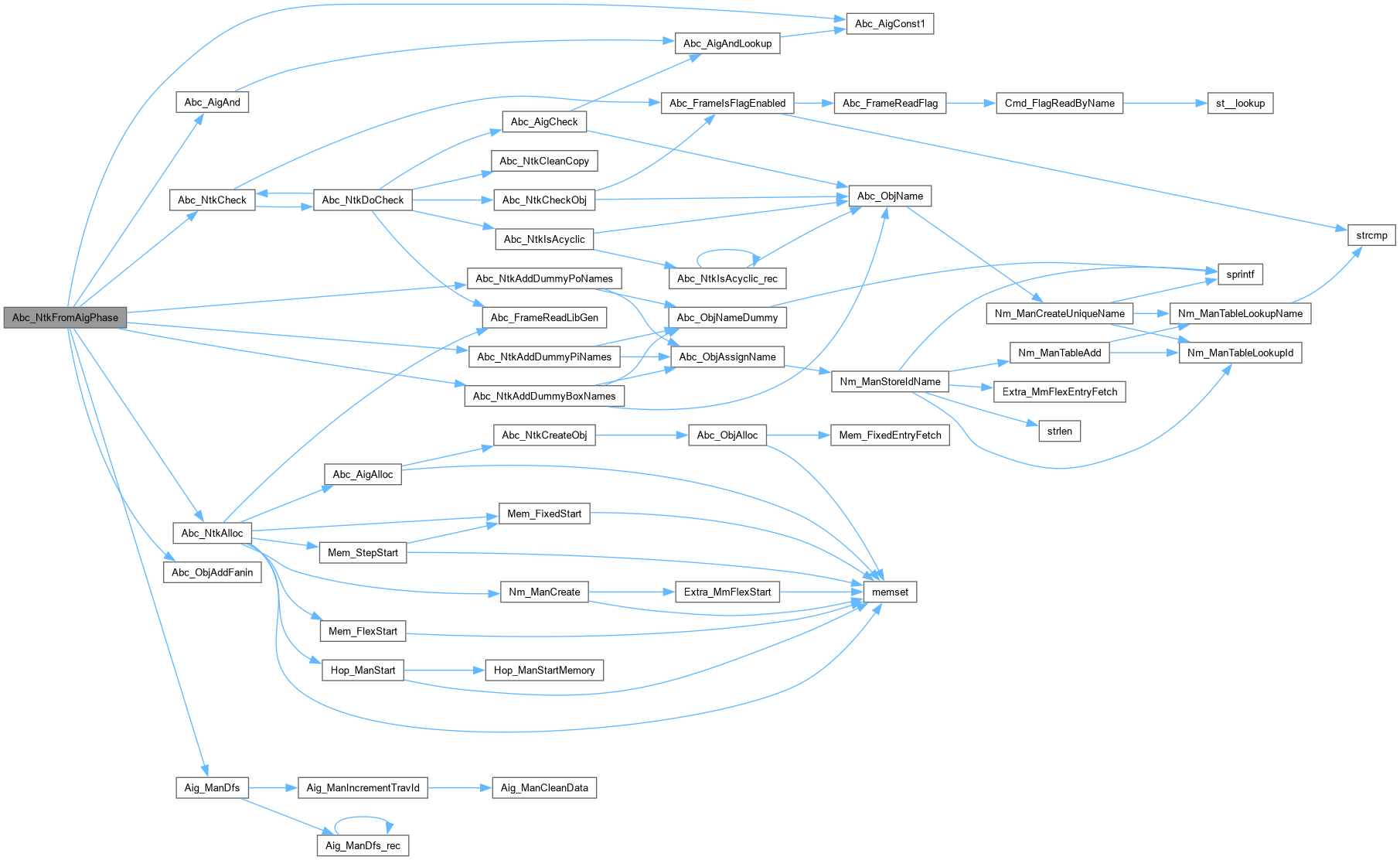

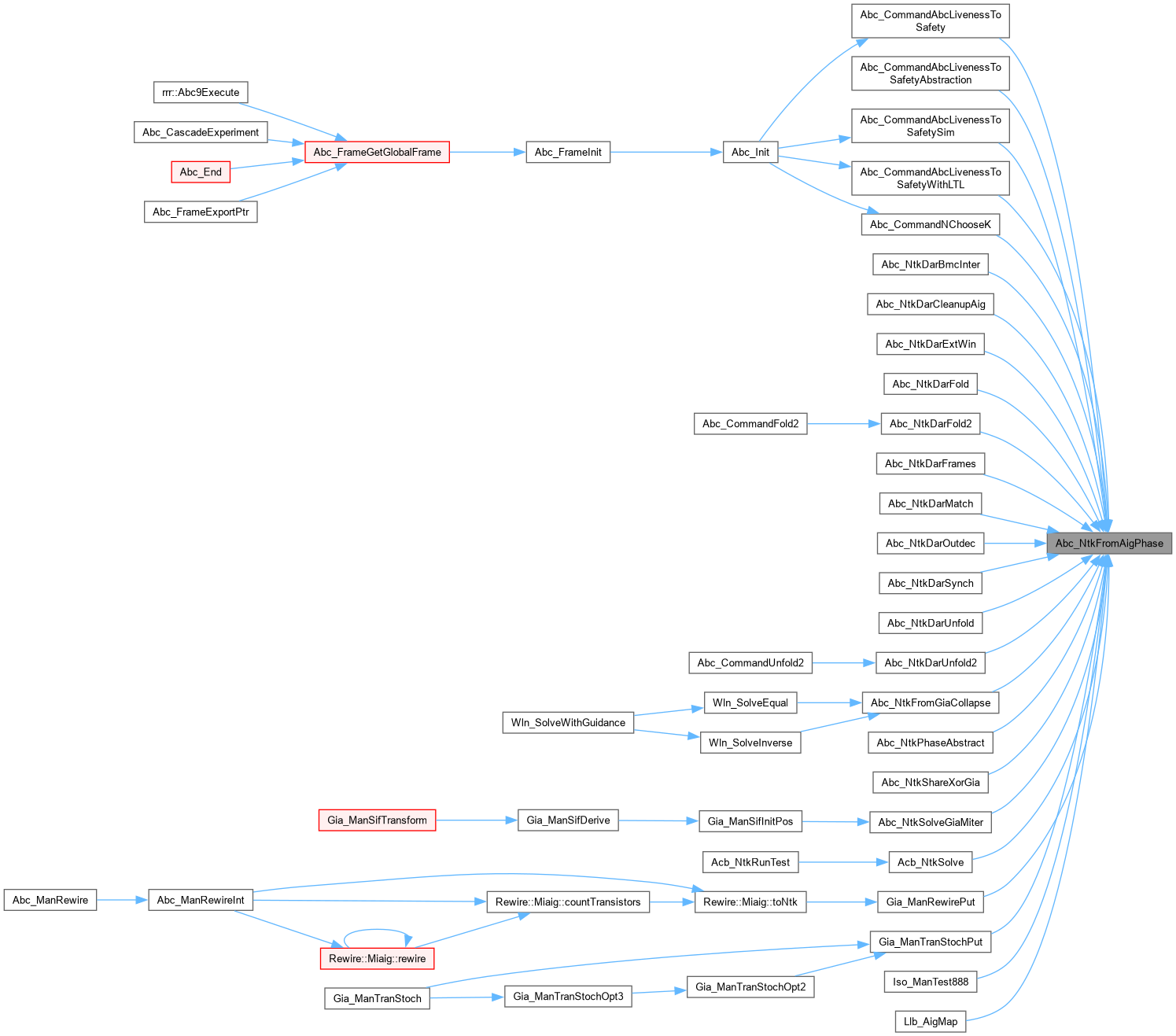

| Abc_Ntk_t * | Abc_NtkFromAigPhase (Aig_Man_t *pMan) |

| DECLARATIONS ///. | |

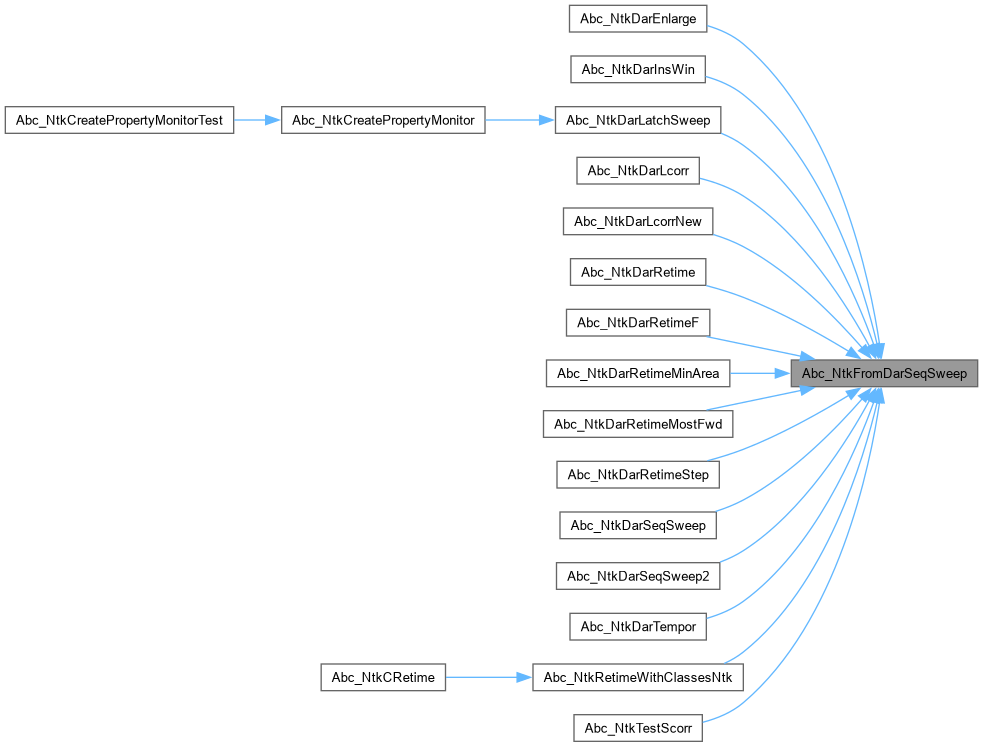

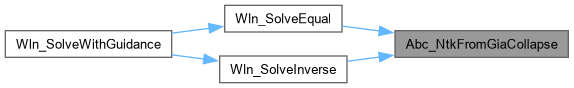

| int | Abc_NtkFromGiaCollapse (Gia_Man_t *pGia) |

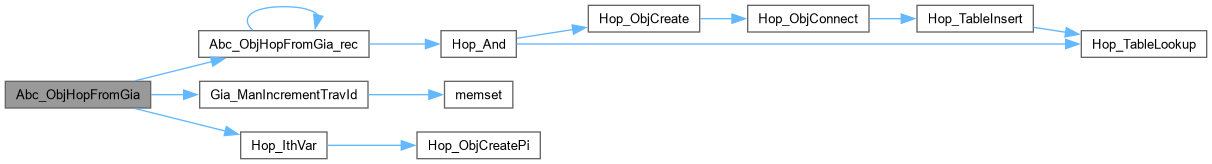

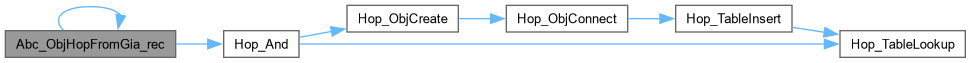

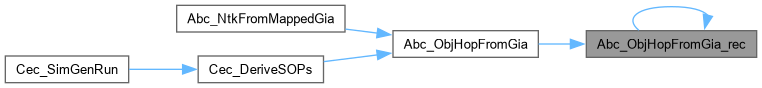

| Hop_Obj_t * | Abc_ObjHopFromGia_rec (Hop_Man_t *pHopMan, Gia_Man_t *p, int Id, Vec_Ptr_t *vCopies) |

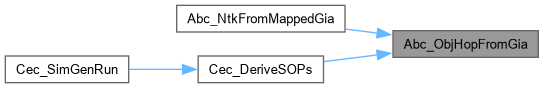

| Hop_Obj_t * | Abc_ObjHopFromGia (Hop_Man_t *pHopMan, Gia_Man_t *p, int GiaId, Vec_Ptr_t *vCopies) |

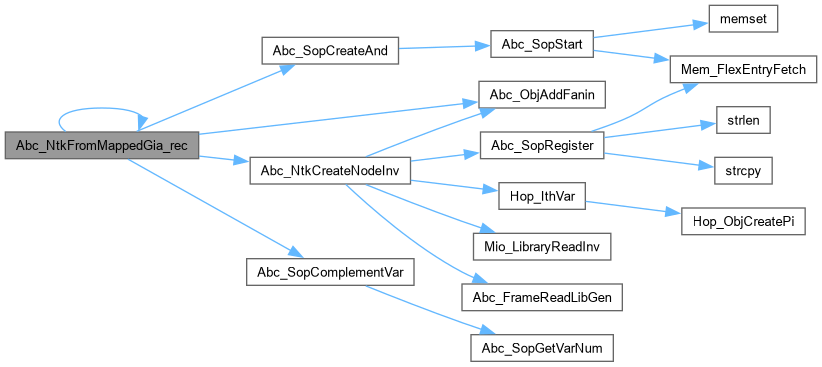

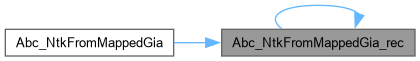

| Abc_Obj_t * | Abc_NtkFromMappedGia_rec (Abc_Ntk_t *pNtkNew, Gia_Man_t *p, int iObj, int fAddInv) |

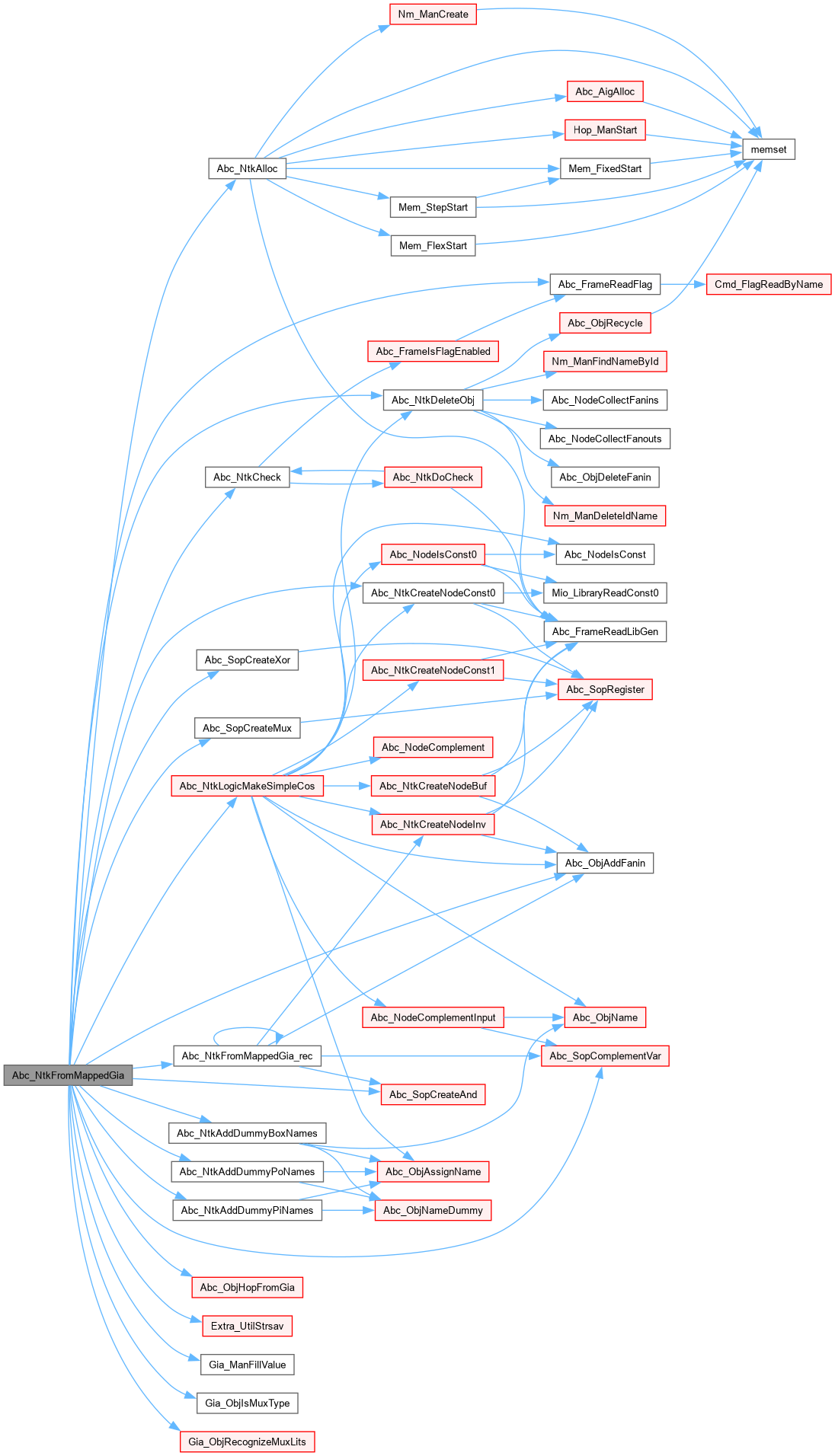

| Abc_Ntk_t * | Abc_NtkFromMappedGia (Gia_Man_t *p, int fFindEnables, int fUseBuffs) |

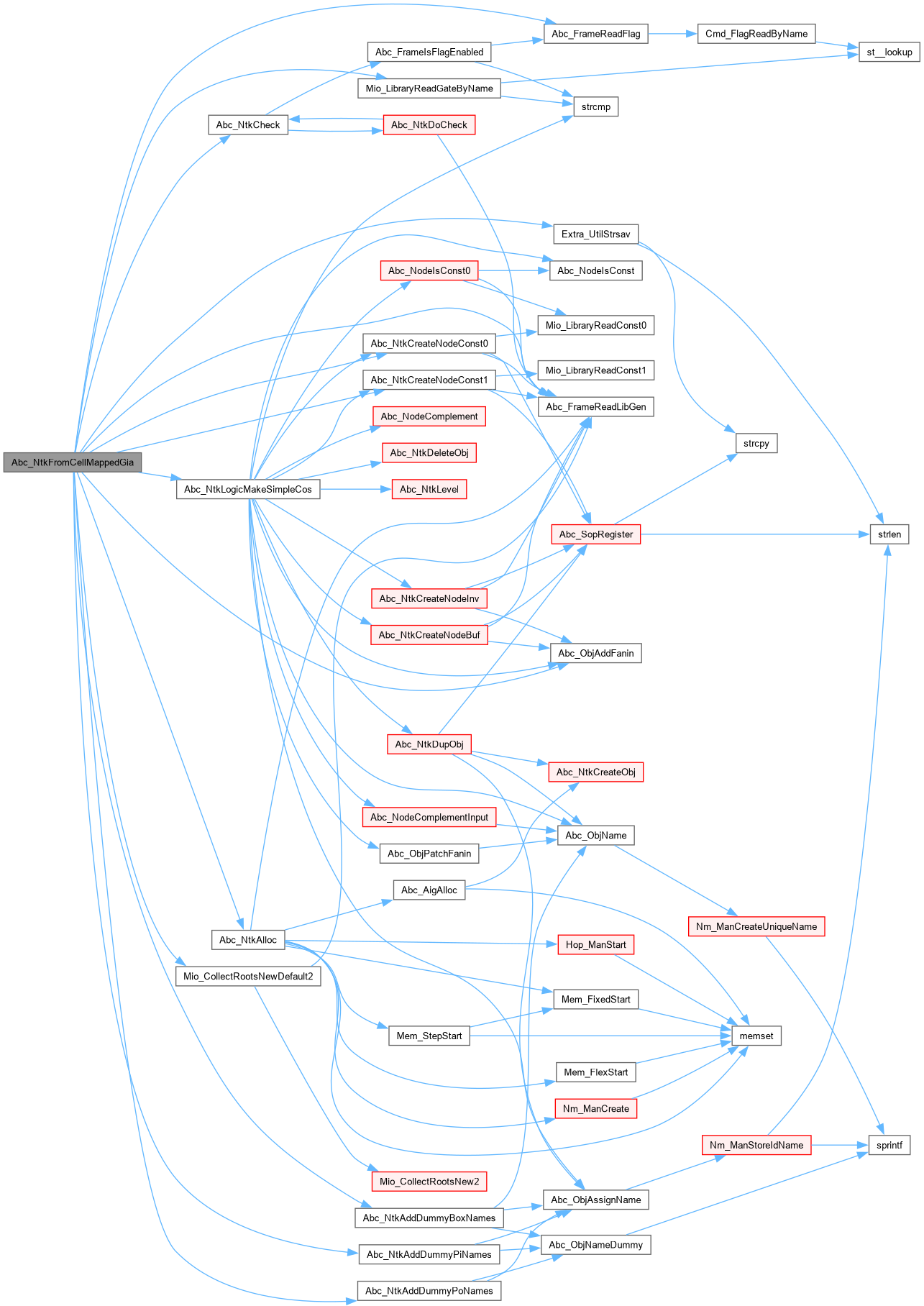

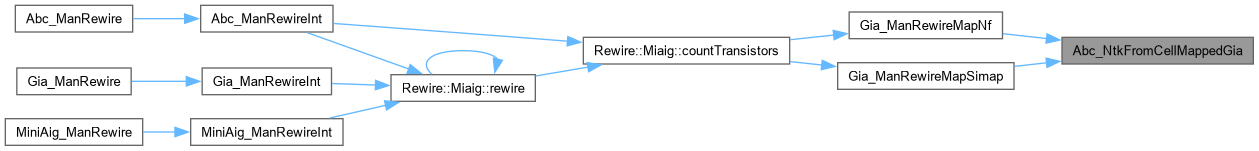

| Abc_Ntk_t * | Abc_NtkFromCellMappedGia (Gia_Man_t *p, int fUseBuffs) |

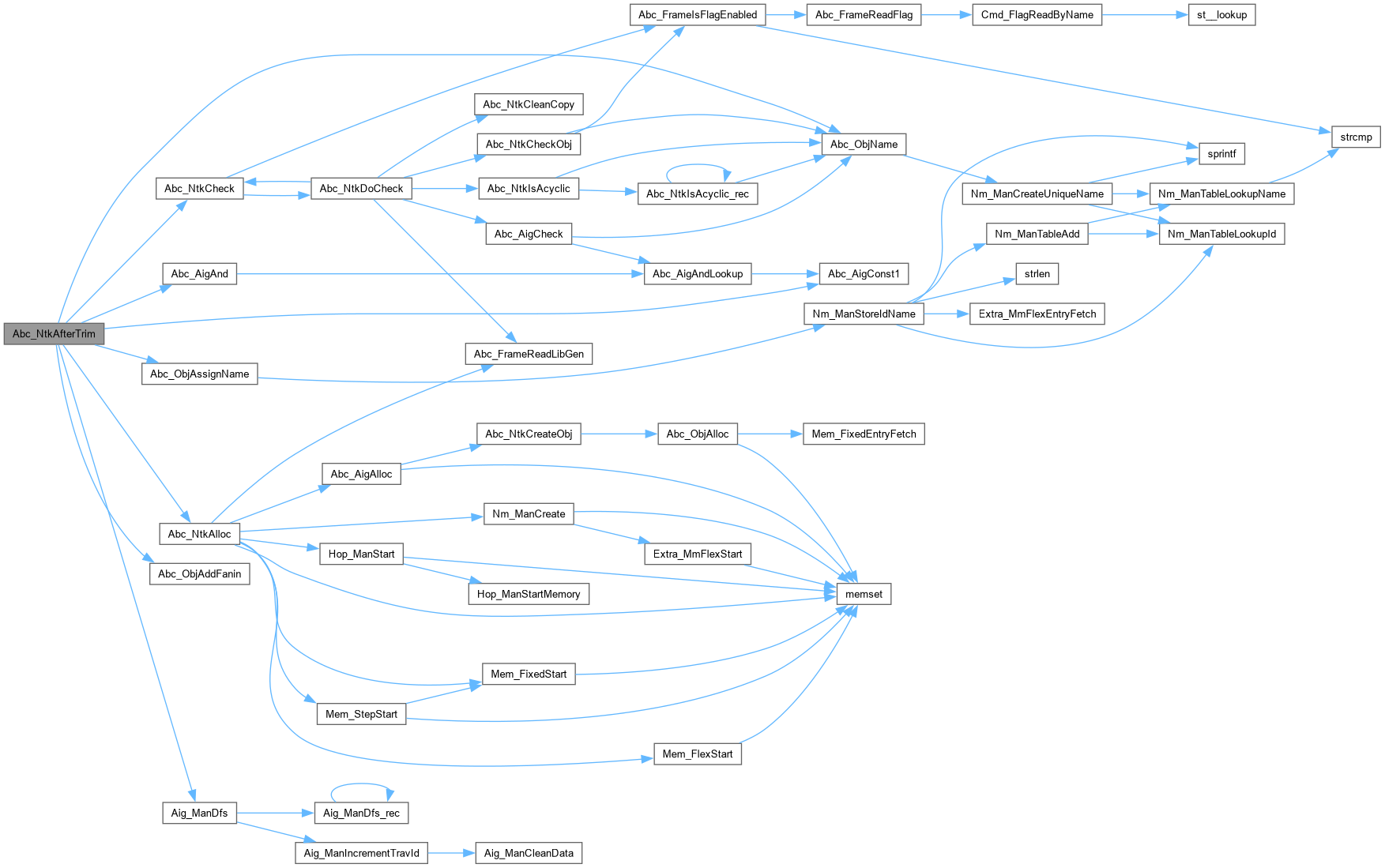

| Abc_Ntk_t * | Abc_NtkAfterTrim (Aig_Man_t *pMan, Abc_Ntk_t *pNtkOld) |

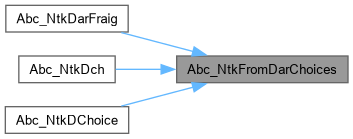

| Abc_Ntk_t * | Abc_NtkFromDarChoices (Abc_Ntk_t *pNtkOld, Aig_Man_t *pMan) |

| Abc_Ntk_t * | Abc_NtkFromDarSeq (Abc_Ntk_t *pNtkOld, Aig_Man_t *pMan) |

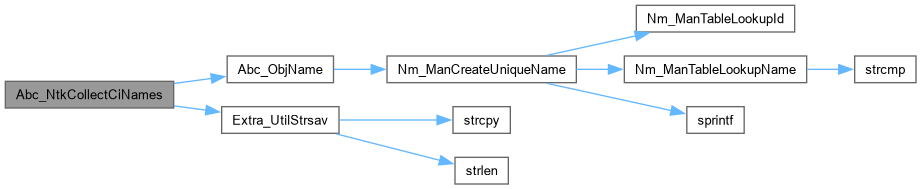

| Vec_Ptr_t * | Abc_NtkCollectCiNames (Abc_Ntk_t *pNtk) |

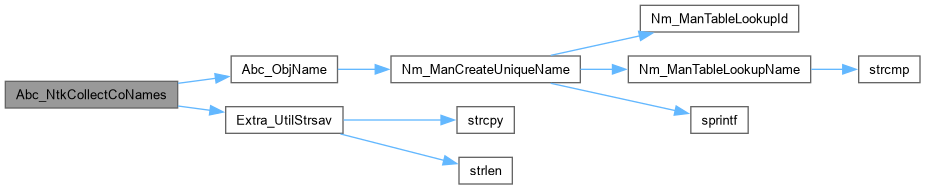

| Vec_Ptr_t * | Abc_NtkCollectCoNames (Abc_Ntk_t *pNtk) |

| Vec_Int_t * | Abc_NtkGetLatchValues (Abc_Ntk_t *pNtk) |

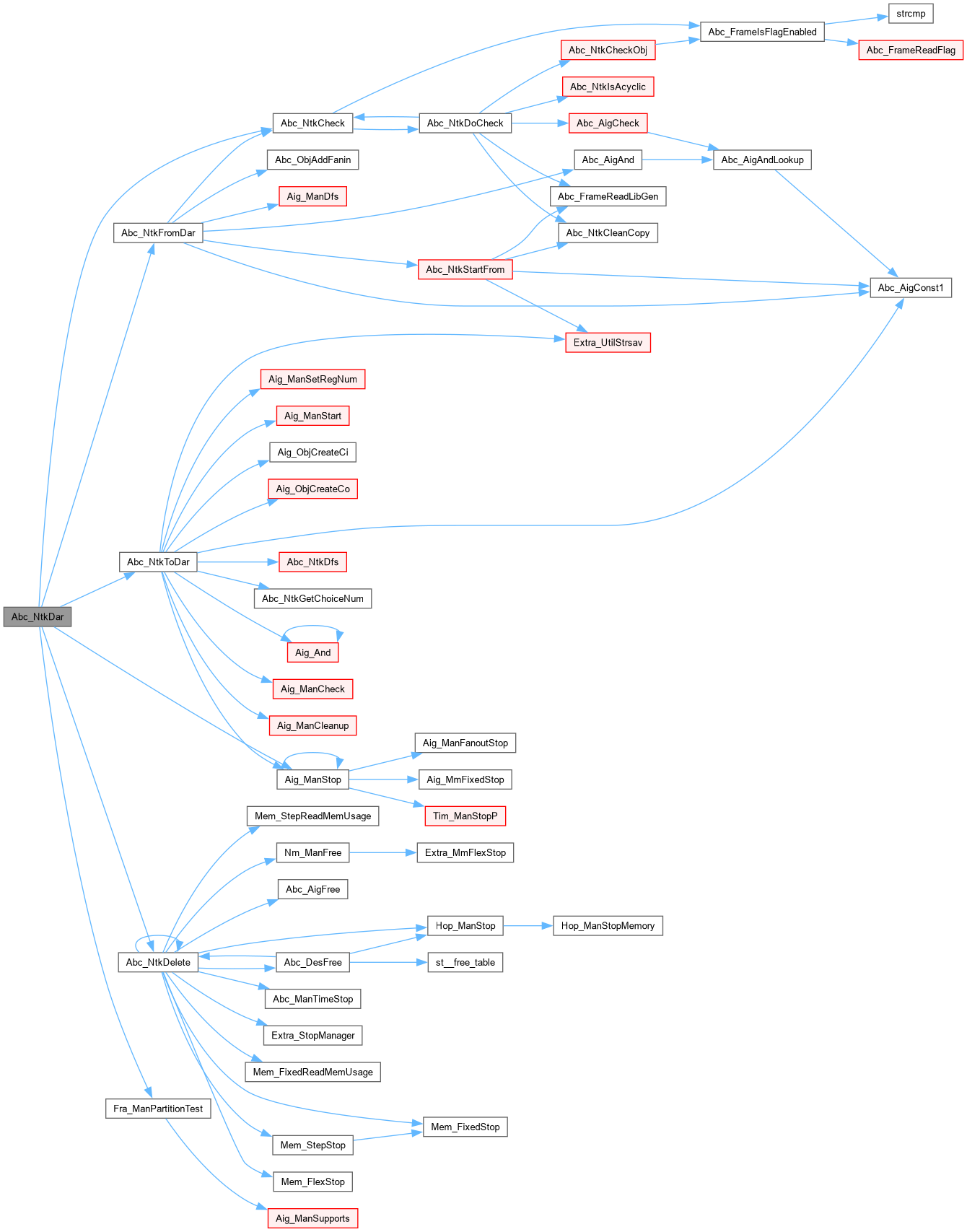

| Abc_Ntk_t * | Abc_NtkDar (Abc_Ntk_t *pNtk) |

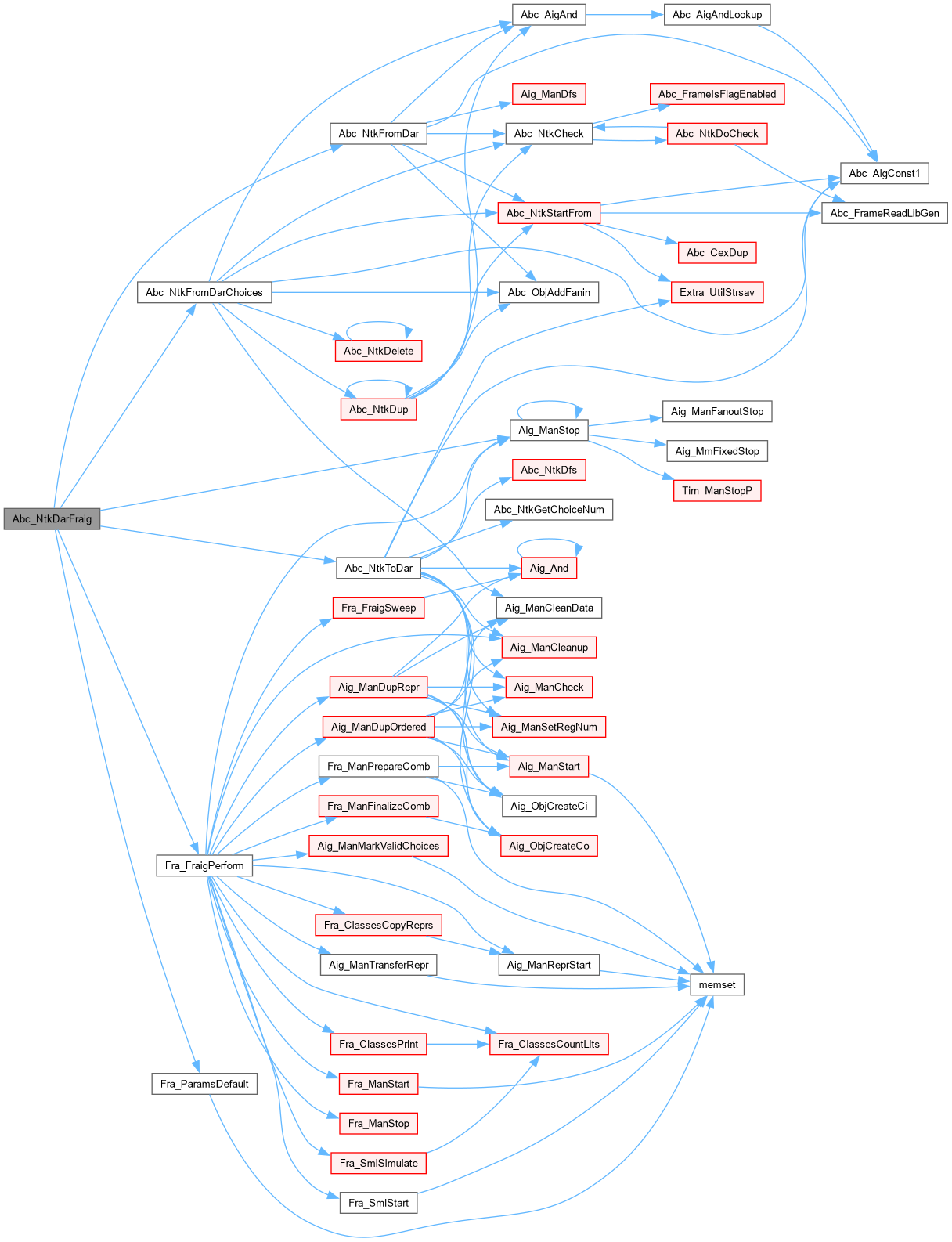

| Abc_Ntk_t * | Abc_NtkDarFraig (Abc_Ntk_t *pNtk, int nConfLimit, int fDoSparse, int fProve, int fTransfer, int fSpeculate, int fChoicing, int fVerbose) |

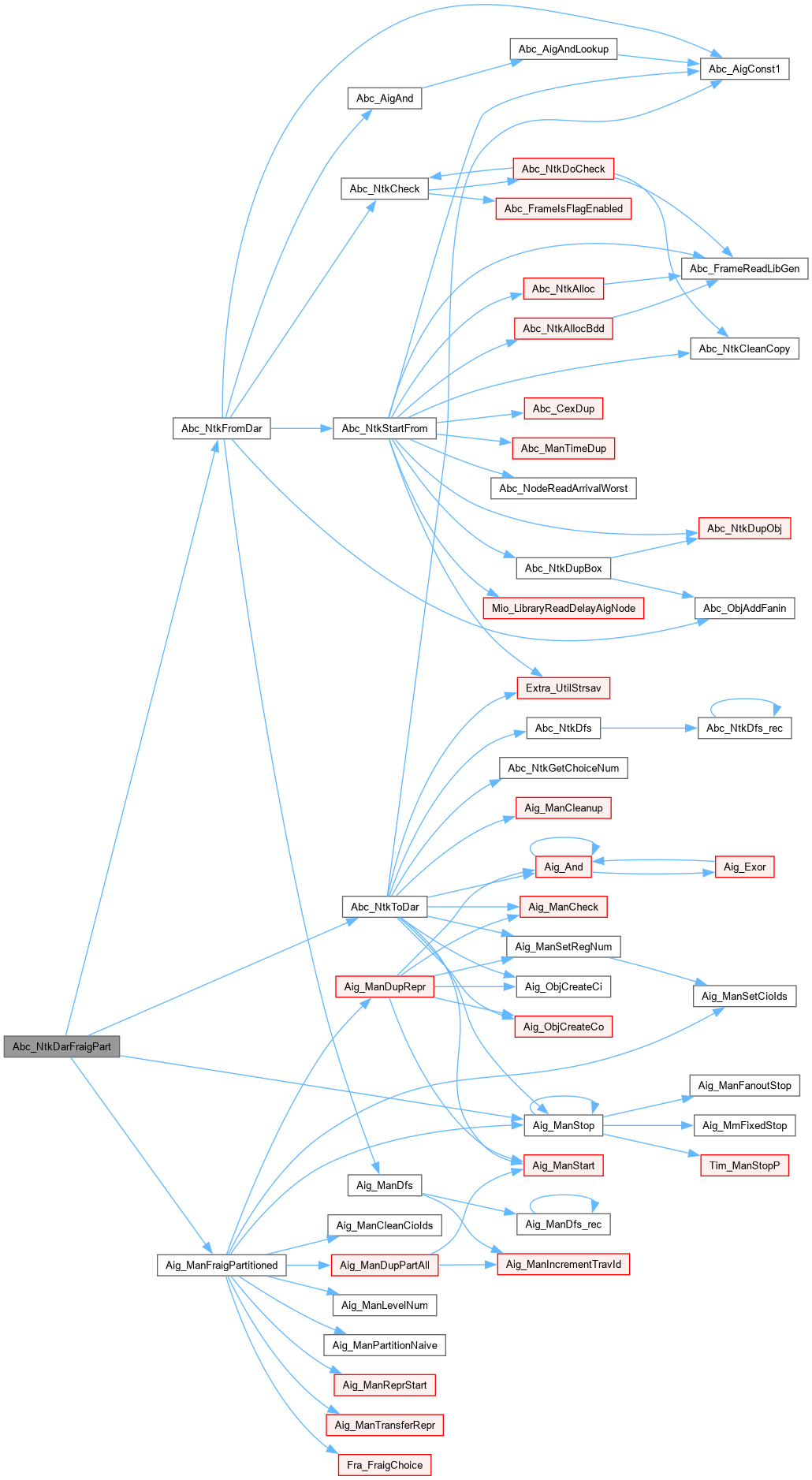

| Abc_Ntk_t * | Abc_NtkDarFraigPart (Abc_Ntk_t *pNtk, int nPartSize, int nConfLimit, int nLevelMax, int fVerbose) |

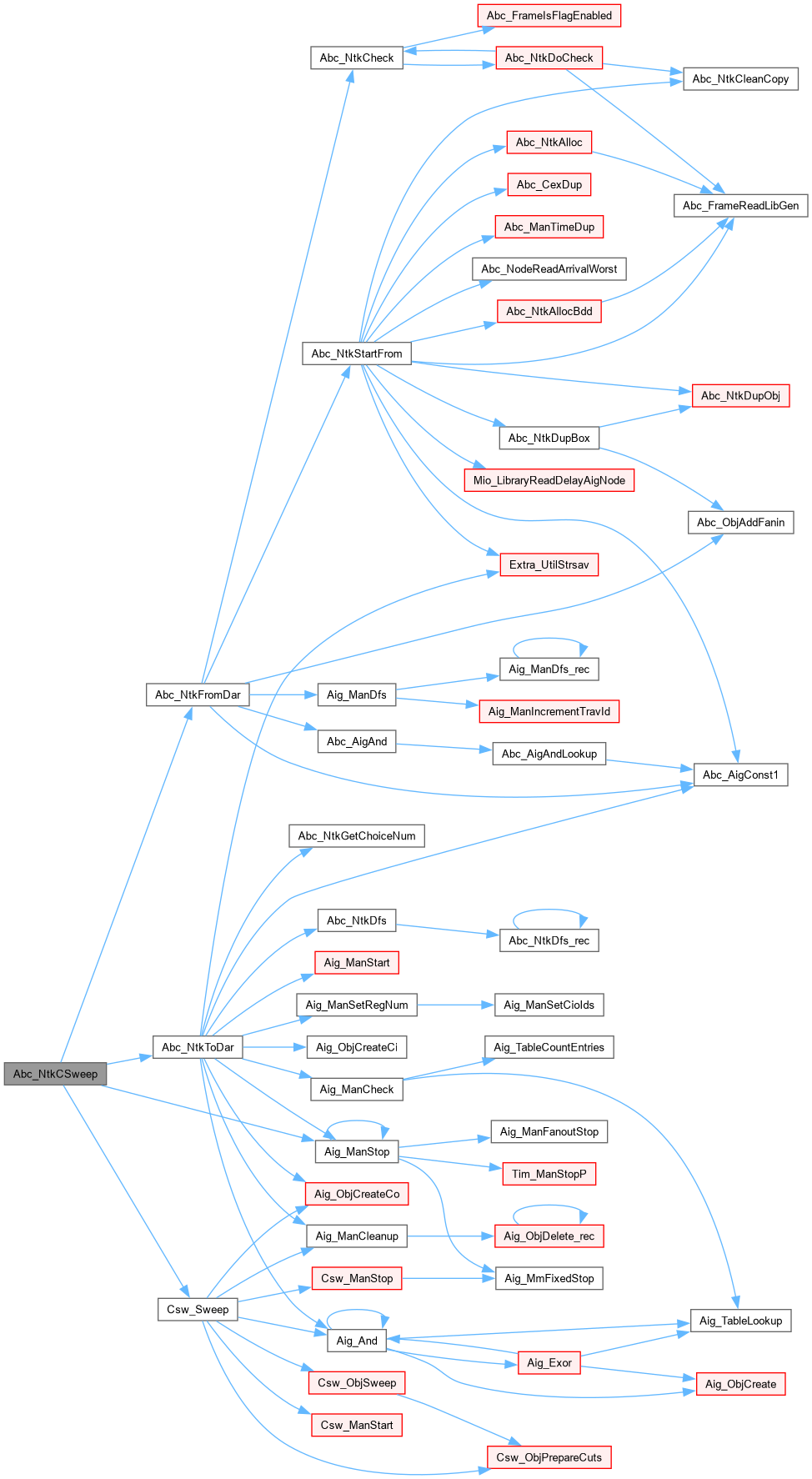

| Abc_Ntk_t * | Abc_NtkCSweep (Abc_Ntk_t *pNtk, int nCutsMax, int nLeafMax, int fVerbose) |

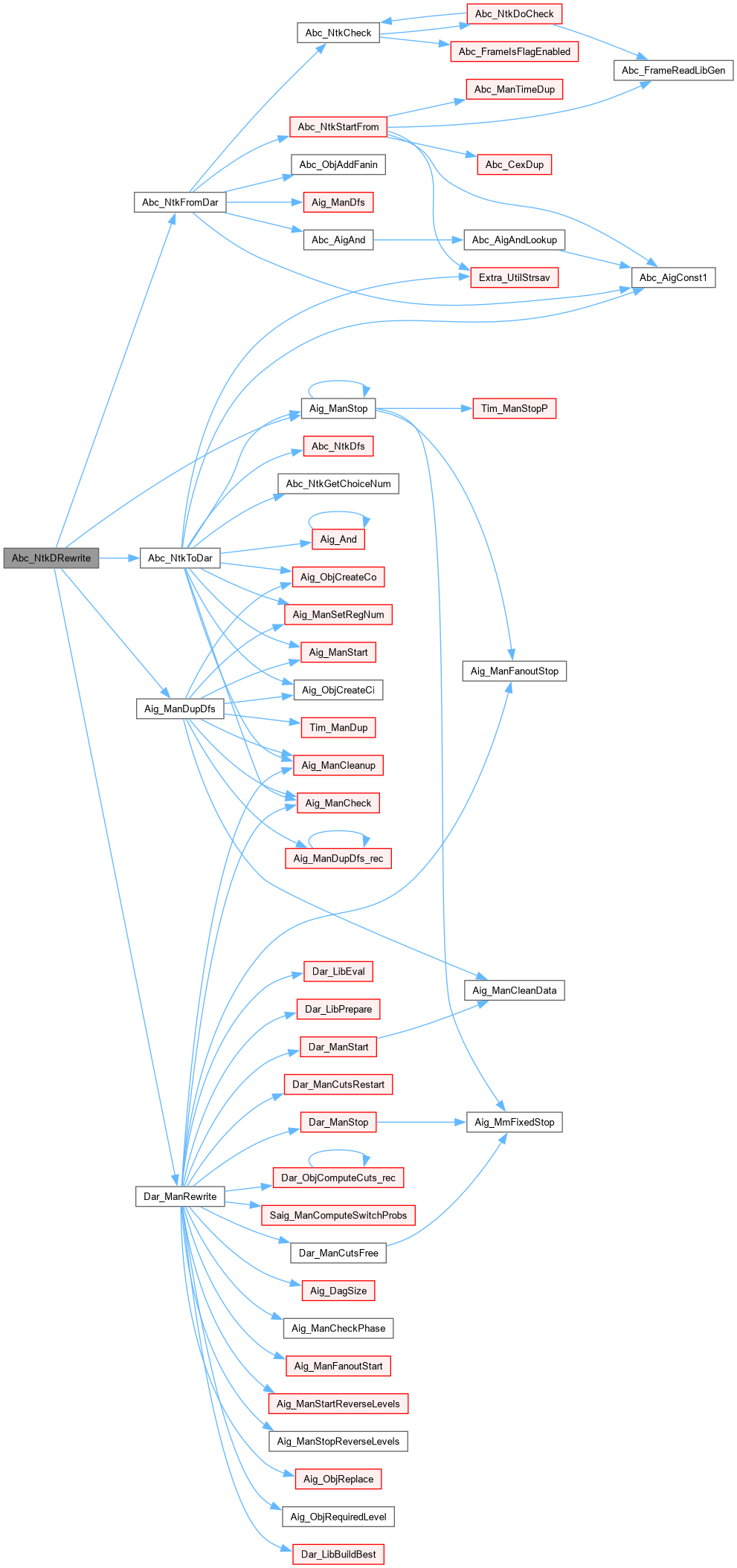

| Abc_Ntk_t * | Abc_NtkDRewrite (Abc_Ntk_t *pNtk, Dar_RwrPar_t *pPars) |

| Abc_Ntk_t * | Abc_NtkDRefactor (Abc_Ntk_t *pNtk, Dar_RefPar_t *pPars) |

| Abc_Ntk_t * | Abc_NtkDC2 (Abc_Ntk_t *pNtk, int fBalance, int fUpdateLevel, int fFanout, int fPower, int fVerbose) |

| Abc_Ntk_t * | Abc_NtkDChoice (Abc_Ntk_t *pNtk, int fBalance, int fUpdateLevel, int fConstruct, int nConfMax, int nLevelMax, int fVerbose) |

| Abc_Ntk_t * | Abc_NtkDch (Abc_Ntk_t *pNtk, Dch_Pars_t *pPars) |

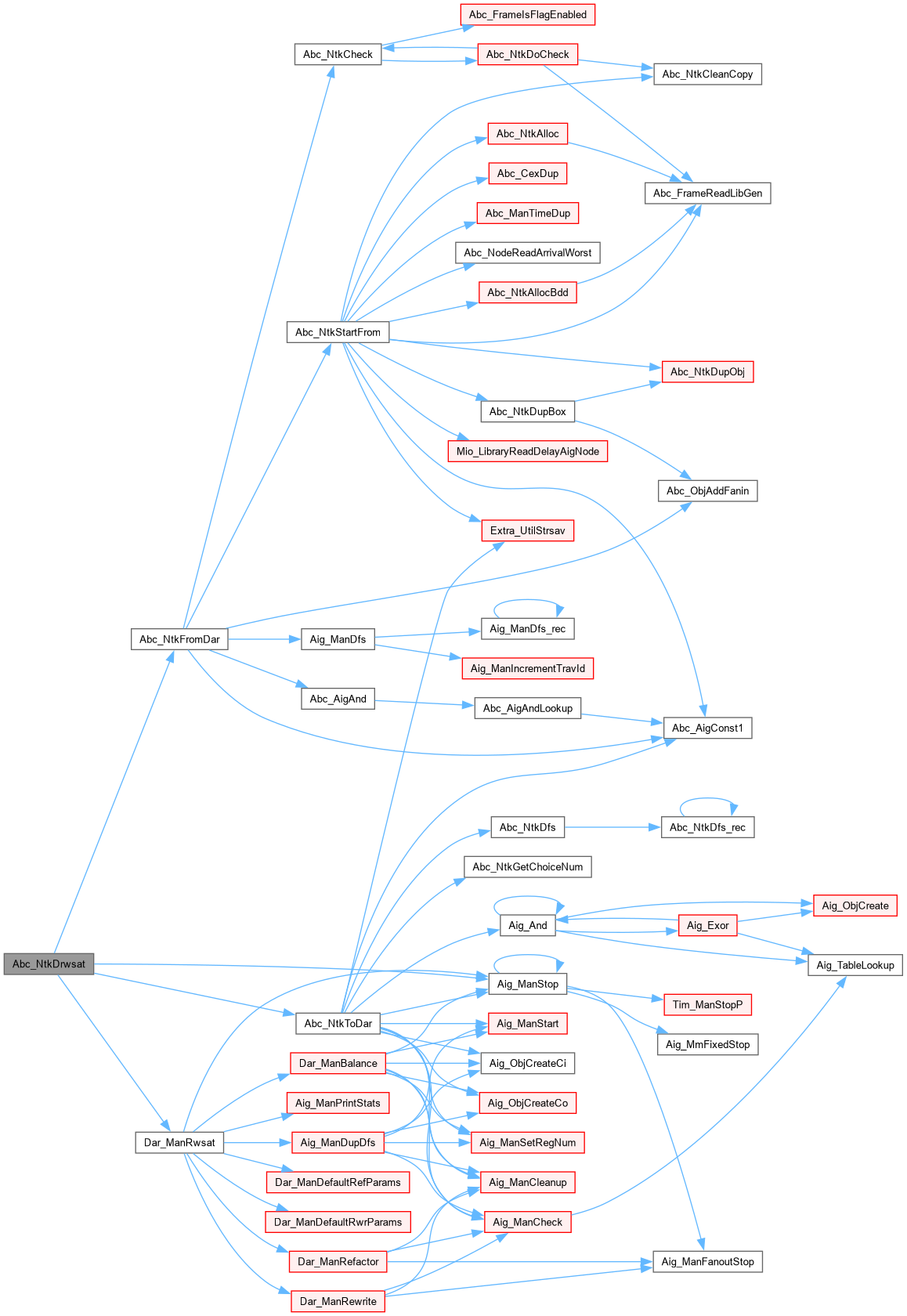

| Abc_Ntk_t * | Abc_NtkDrwsat (Abc_Ntk_t *pNtk, int fBalance, int fVerbose) |

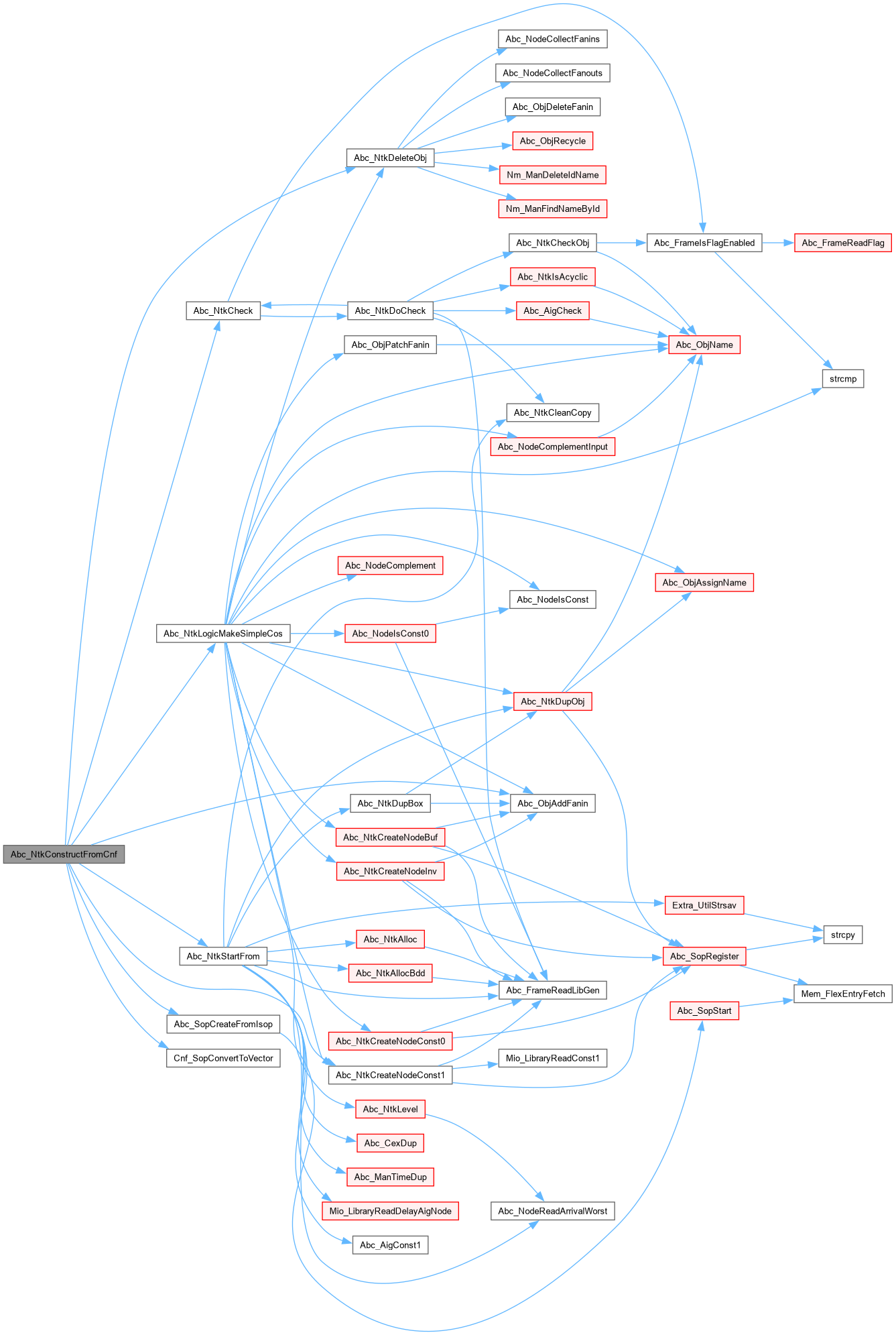

| Abc_Ntk_t * | Abc_NtkConstructFromCnf (Abc_Ntk_t *pNtk, Cnf_Man_t *p, Vec_Ptr_t *vMapped) |

| Abc_Ntk_t * | Abc_NtkDarToCnf (Abc_Ntk_t *pNtk, char *pFileName, int fFastAlgo, int fChangePol, int fVerbose) |

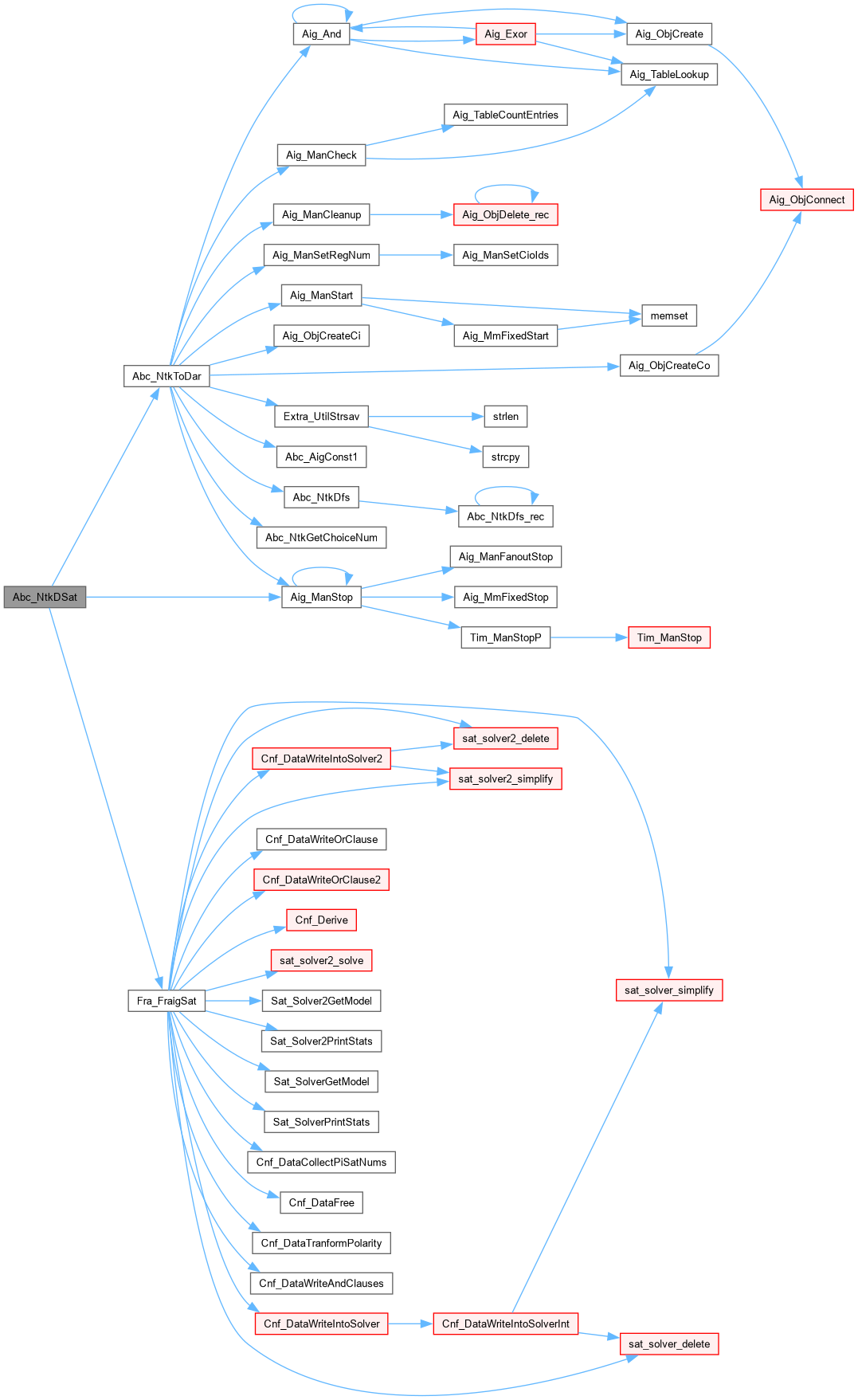

| int | Abc_NtkDSat (Abc_Ntk_t *pNtk, ABC_INT64_T nConfLimit, ABC_INT64_T nInsLimit, int nLearnedStart, int nLearnedDelta, int nLearnedPerce, int fAlignPol, int fAndOuts, int fNewSolver, int fVerbose) |

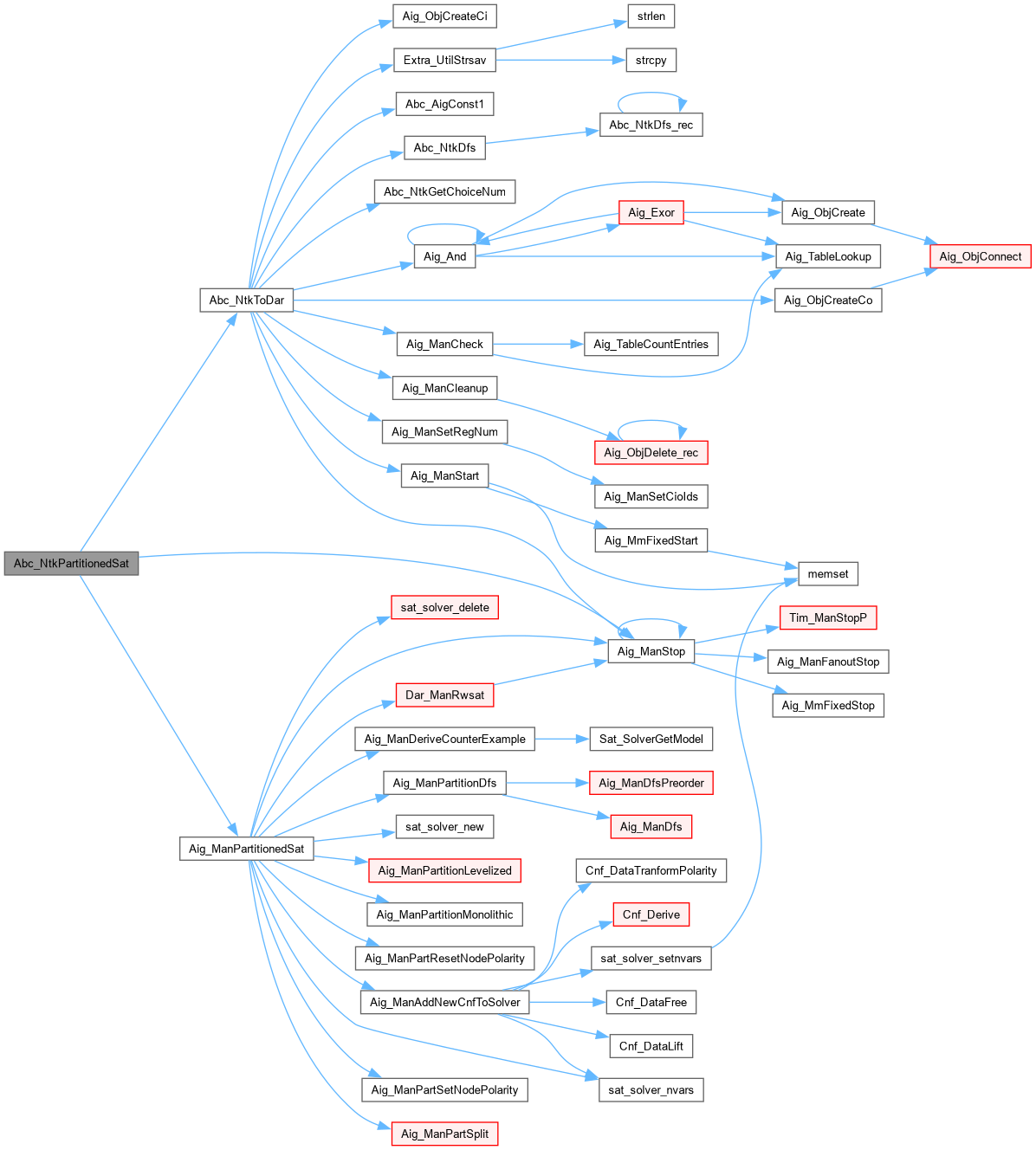

| int | Abc_NtkPartitionedSat (Abc_Ntk_t *pNtk, int nAlgo, int nPartSize, int nConfPart, int nConfTotal, int fAlignPol, int fSynthesize, int fVerbose) |

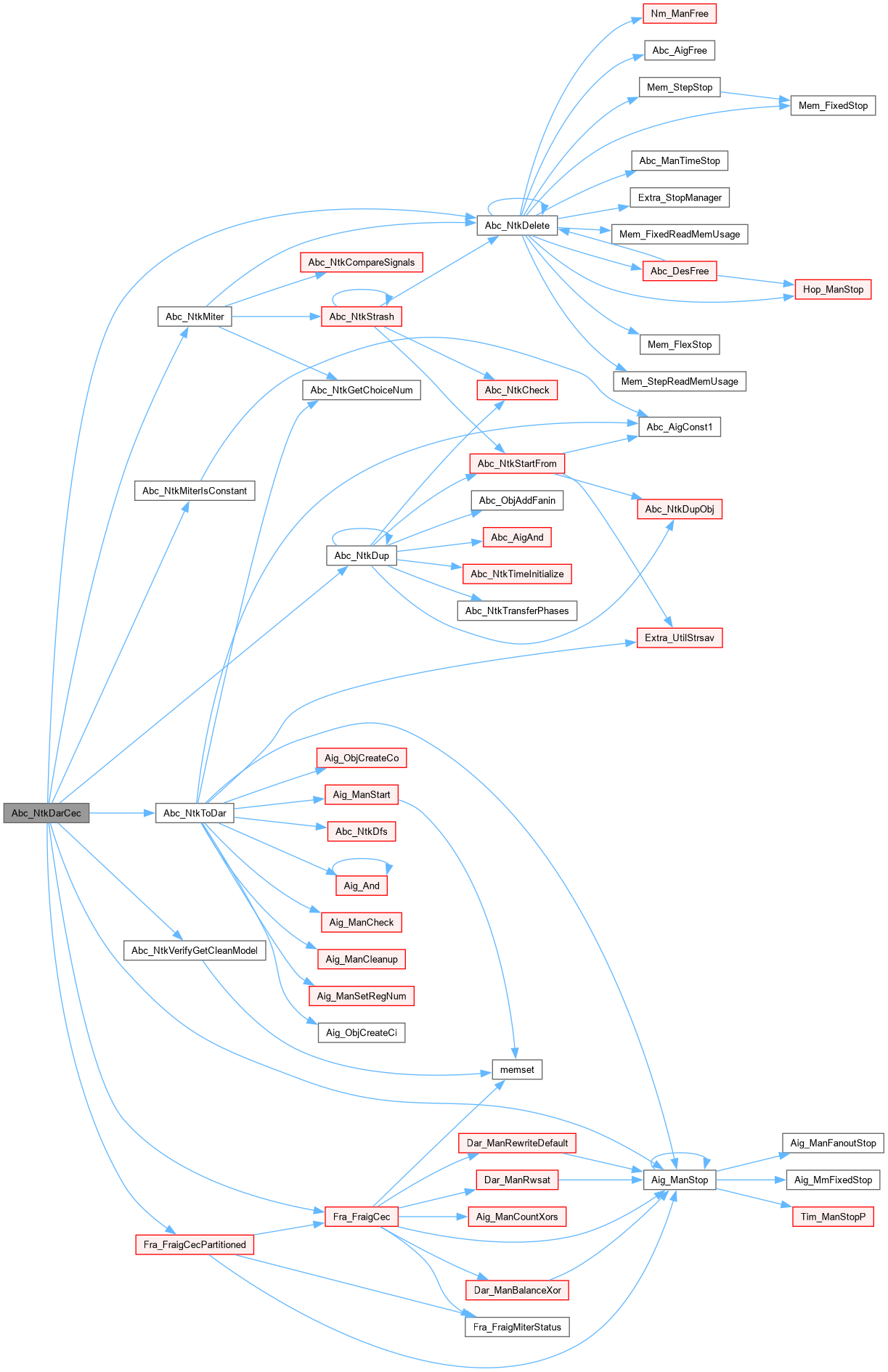

| int | Abc_NtkDarCec (Abc_Ntk_t *pNtk1, Abc_Ntk_t *pNtk2, int nConfLimit, int fPartition, int fVerbose) |

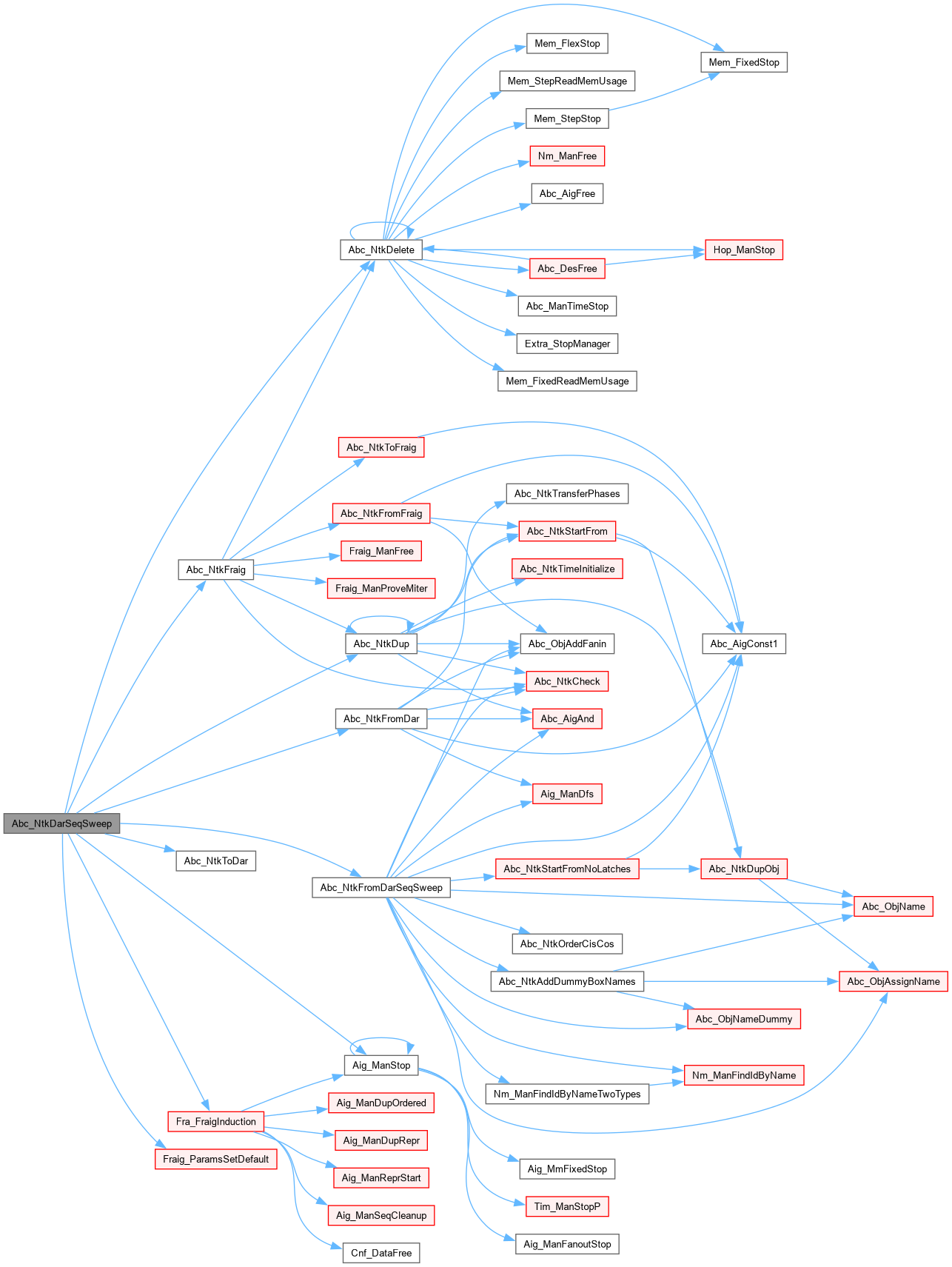

| Abc_Ntk_t * | Abc_NtkDarSeqSweep (Abc_Ntk_t *pNtk, Fra_Ssw_t *pPars) |

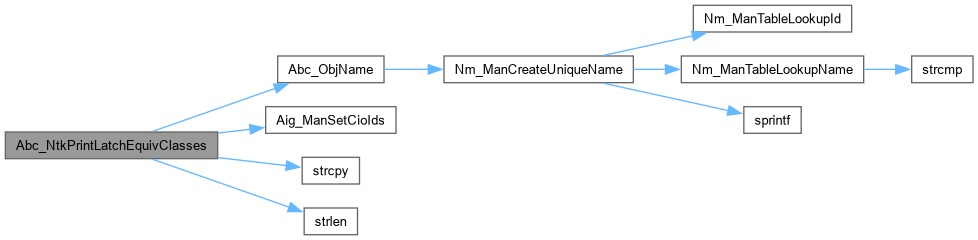

| void | Abc_NtkPrintLatchEquivClasses (Abc_Ntk_t *pNtk, Aig_Man_t *pAig) |

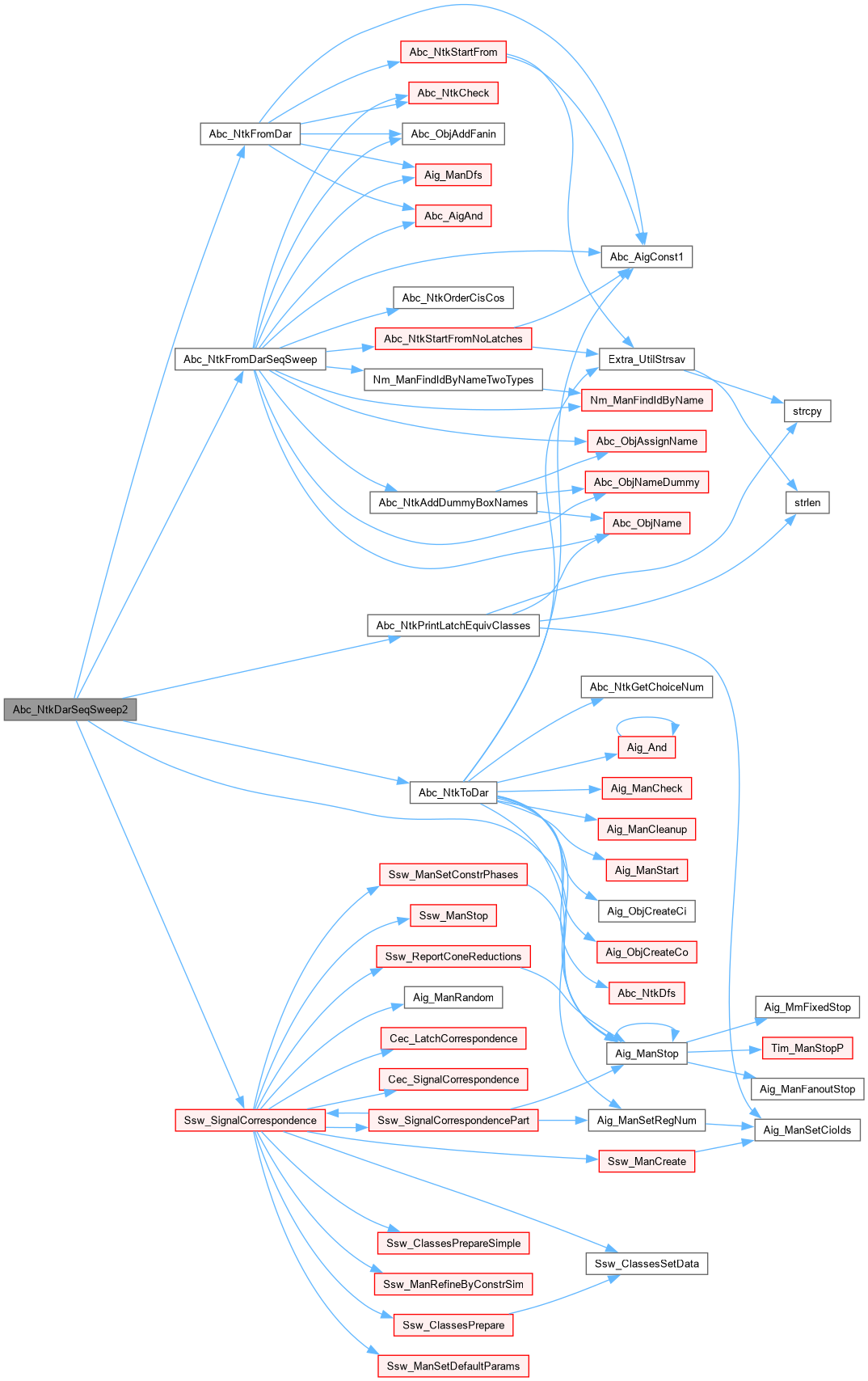

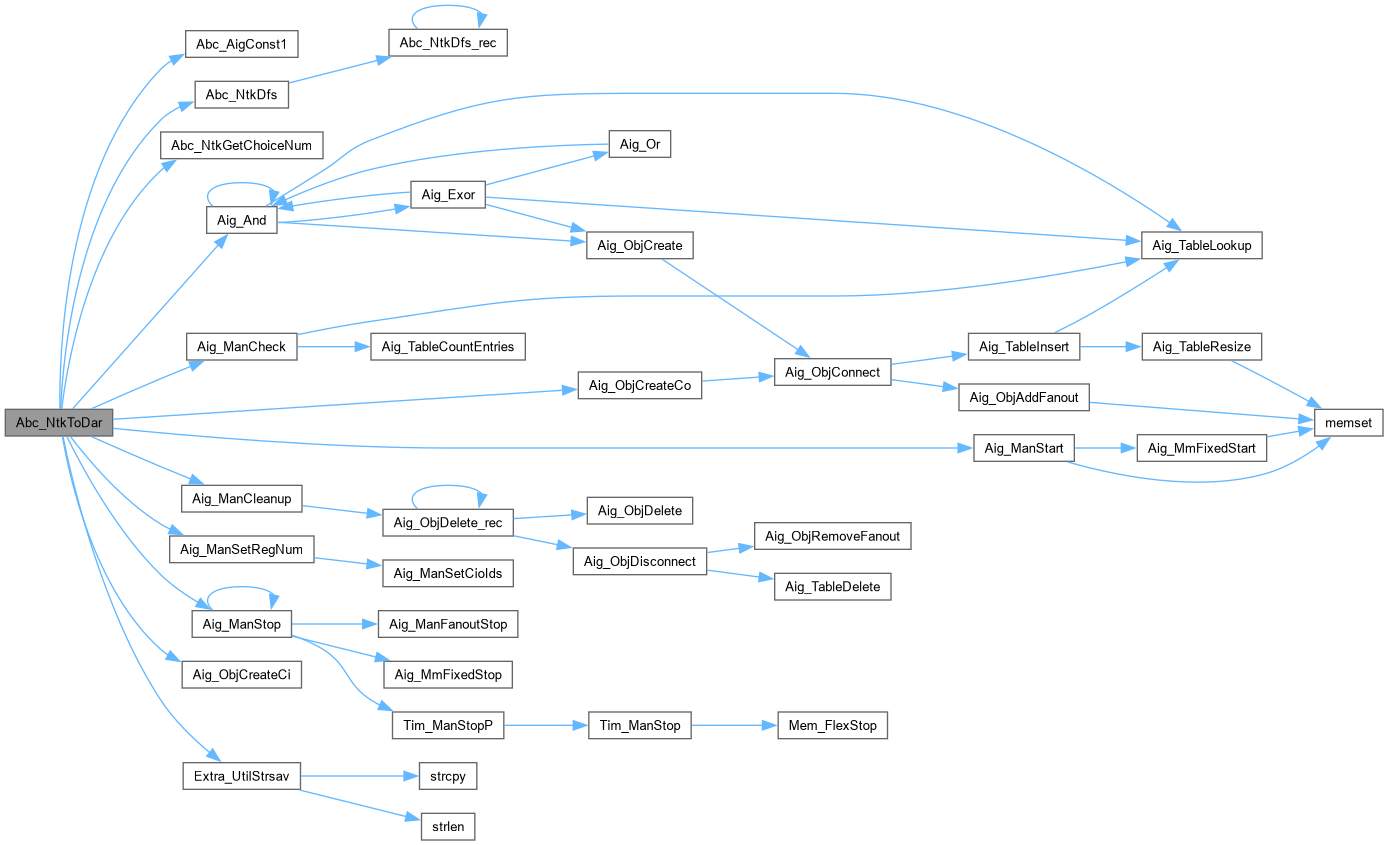

| Abc_Ntk_t * | Abc_NtkDarSeqSweep2 (Abc_Ntk_t *pNtk, Ssw_Pars_t *pPars) |

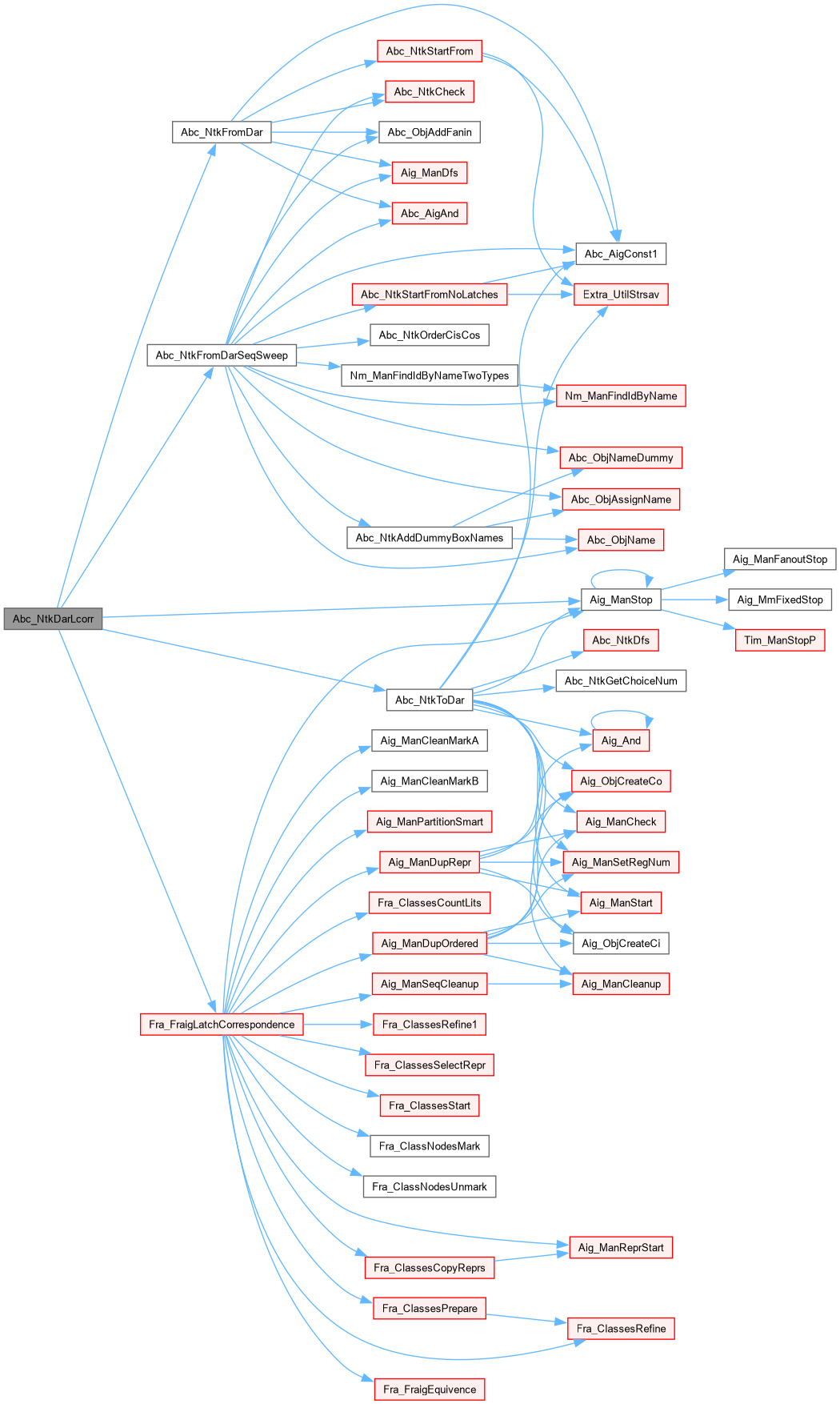

| Abc_Ntk_t * | Abc_NtkDarLcorr (Abc_Ntk_t *pNtk, int nFramesP, int nConfMax, int fVerbose) |

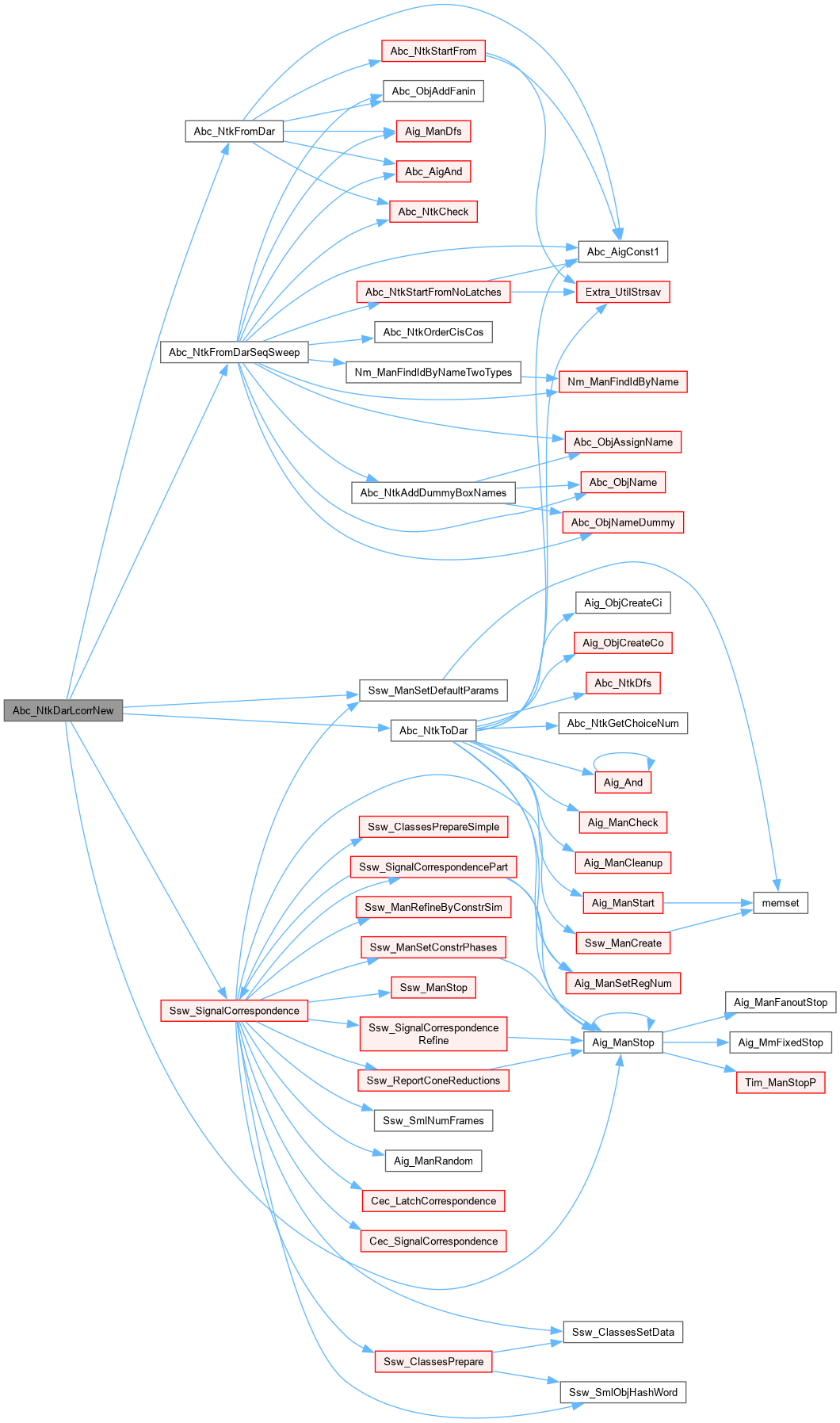

| Abc_Ntk_t * | Abc_NtkDarLcorrNew (Abc_Ntk_t *pNtk, int nVarsMax, int nConfMax, int nLimitMax, int fVerbose) |

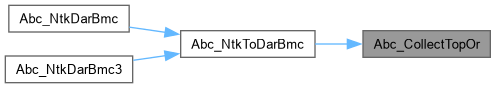

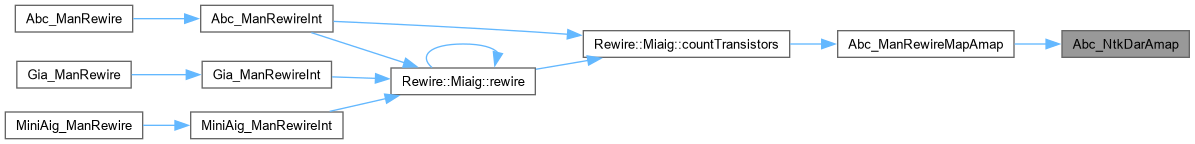

| int | Abc_NtkDarBmc (Abc_Ntk_t *pNtk, int nStart, int nFrames, int nSizeMax, int nNodeDelta, int nTimeOut, int nBTLimit, int nBTLimitAll, int fRewrite, int fNewAlgo, int fOrDecomp, int nCofFanLit, int fVerbose, int *piFrames, int fUseSatoko) |

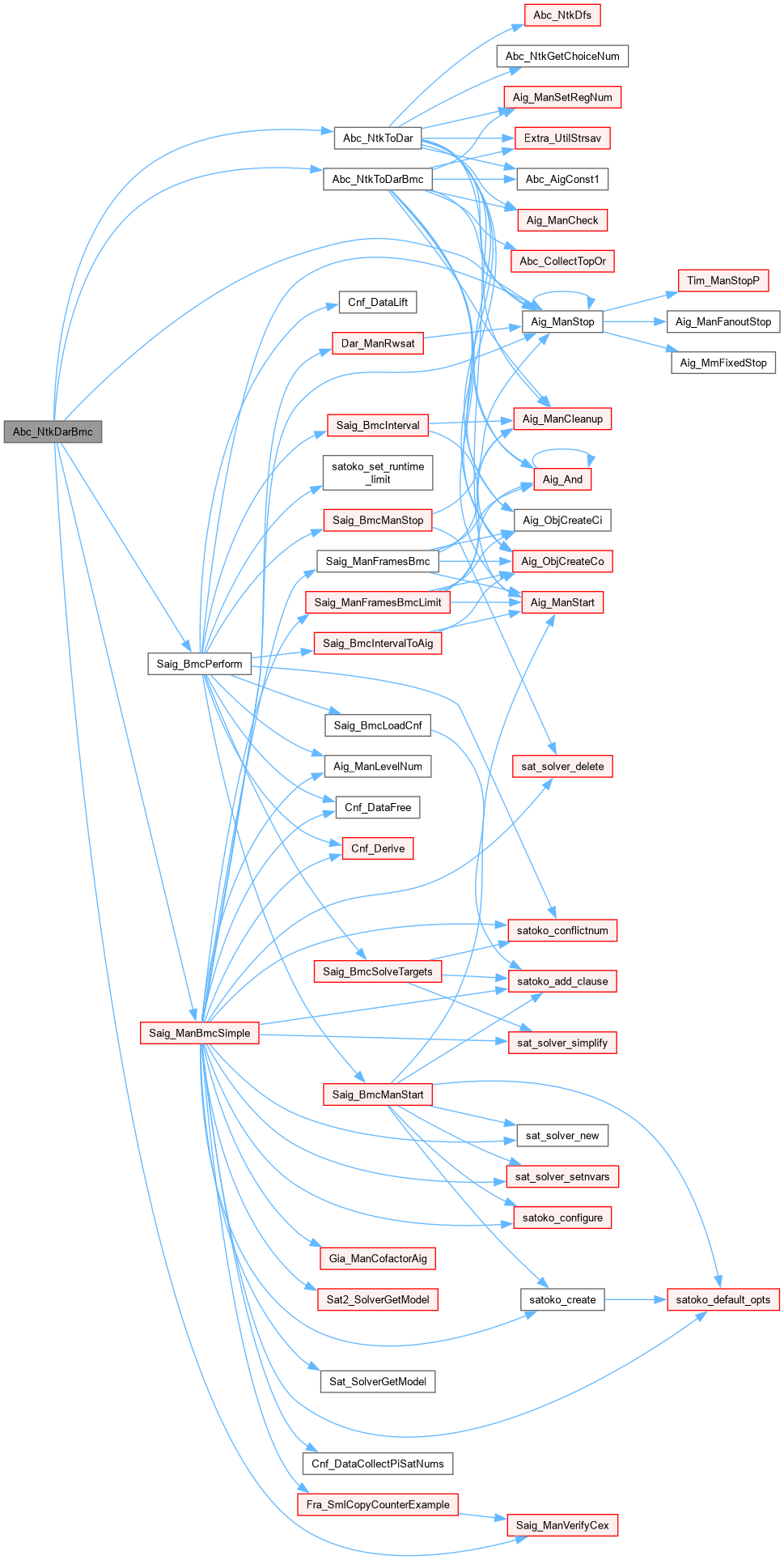

| int | Abc_NtkDarBmc3 (Abc_Ntk_t *pNtk, Saig_ParBmc_t *pPars, int fOrDecomp) |

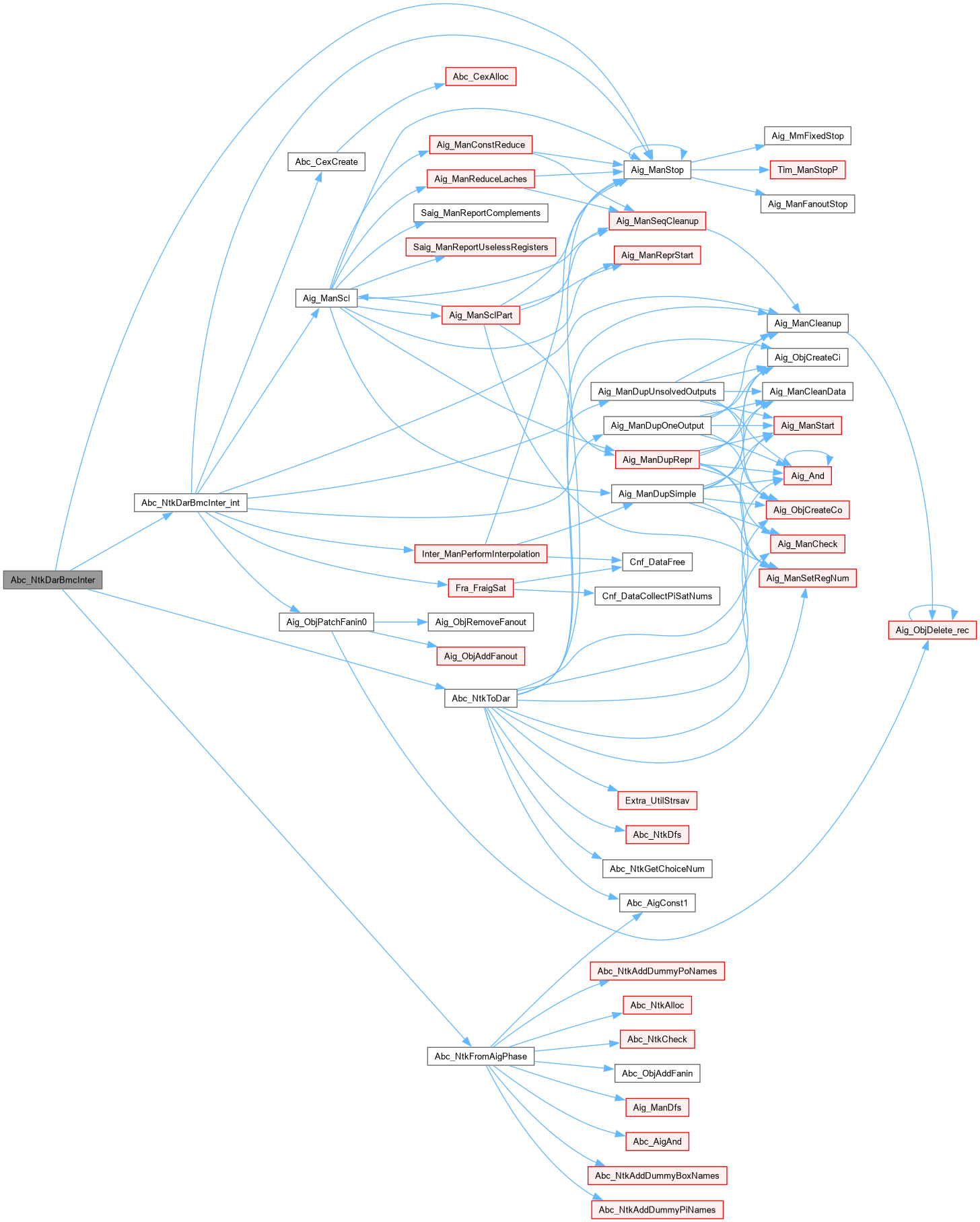

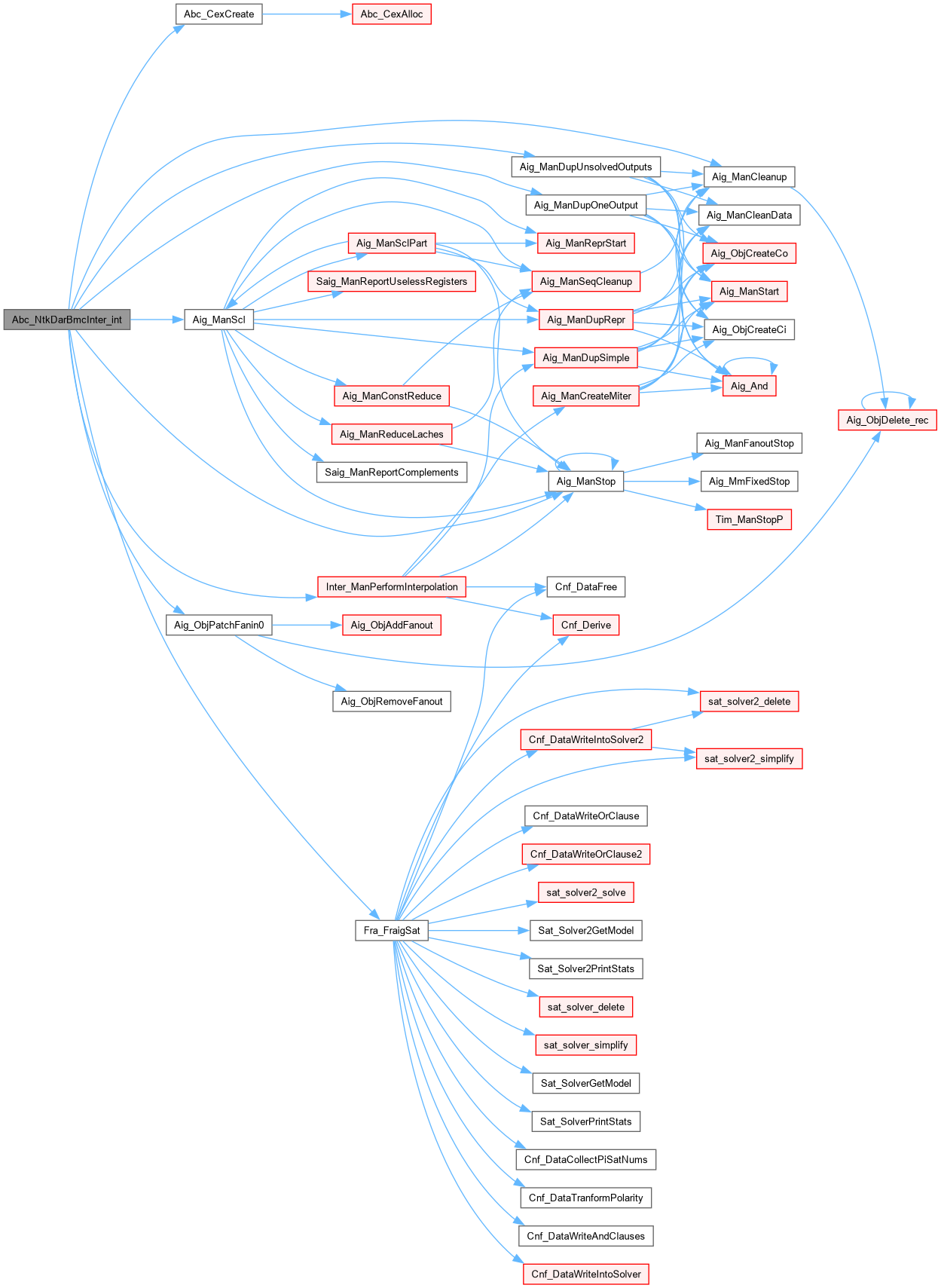

| int | Abc_NtkDarBmcInter_int (Aig_Man_t *pMan, Inter_ManParams_t *pPars, Aig_Man_t **ppNtkRes) |

| int | Abc_NtkDarBmcInter (Abc_Ntk_t *pNtk, Inter_ManParams_t *pPars, Abc_Ntk_t **ppNtkRes) |

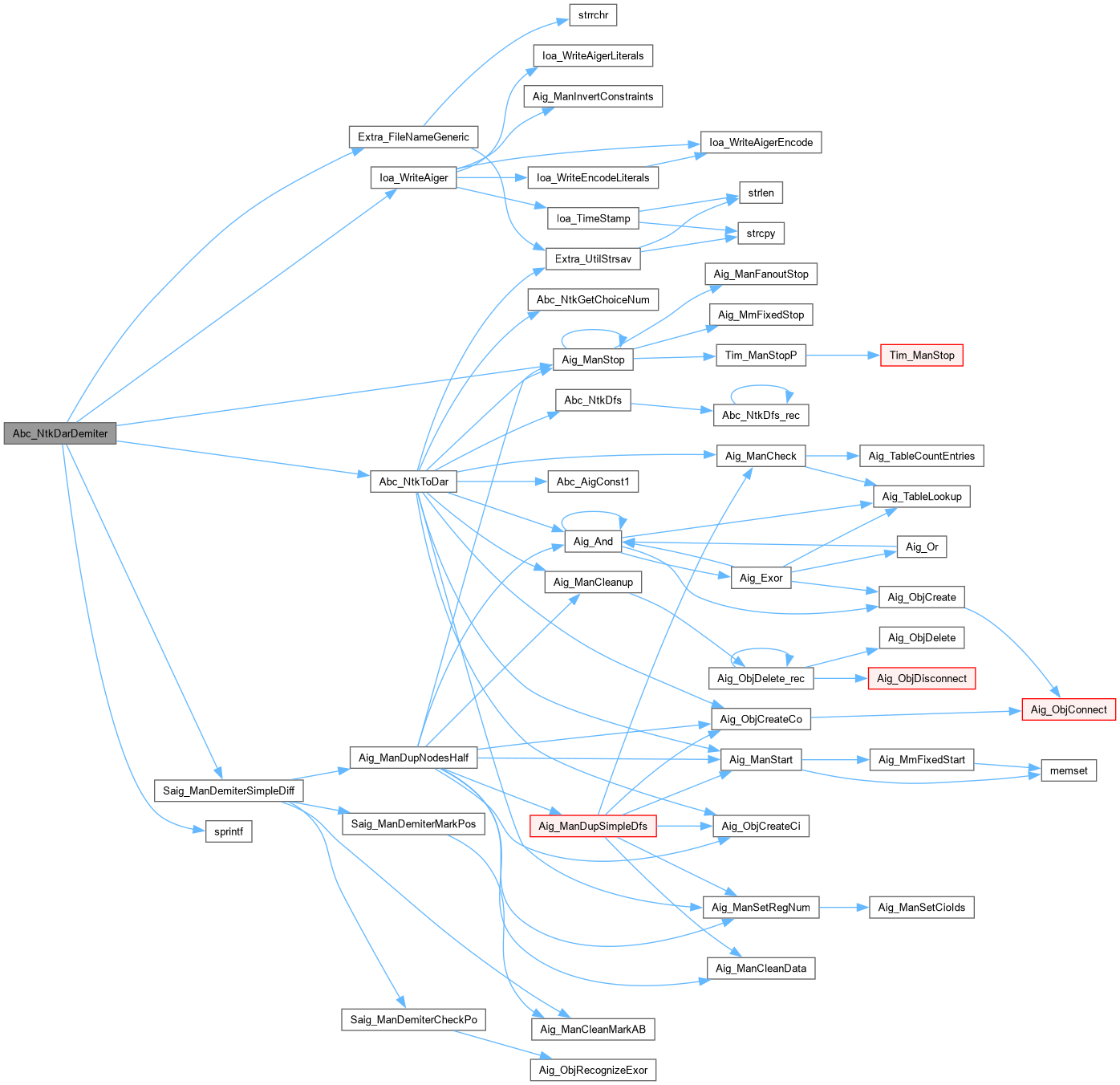

| int | Abc_NtkDarDemiter (Abc_Ntk_t *pNtk) |

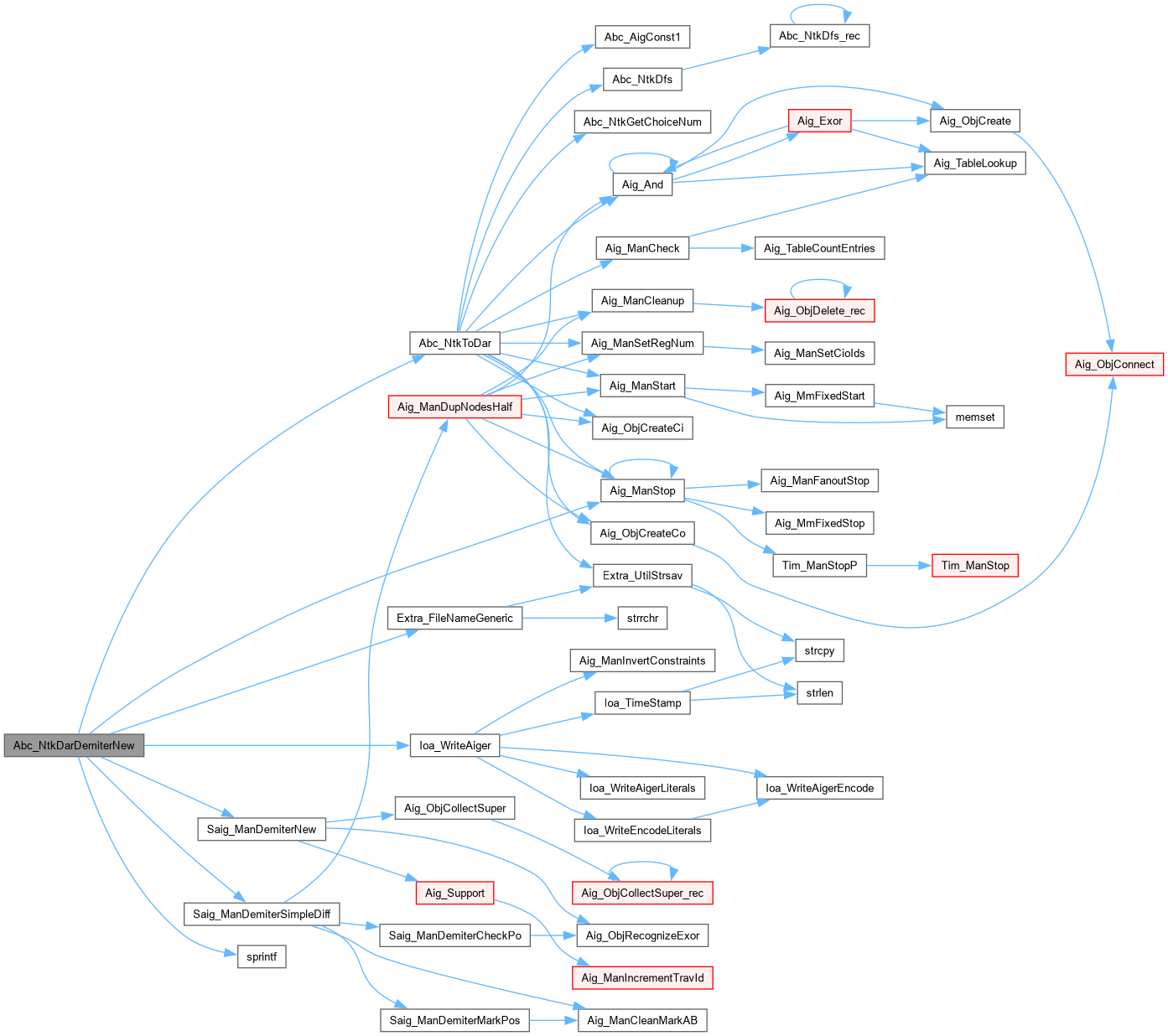

| int | Abc_NtkDarDemiterNew (Abc_Ntk_t *pNtk) |

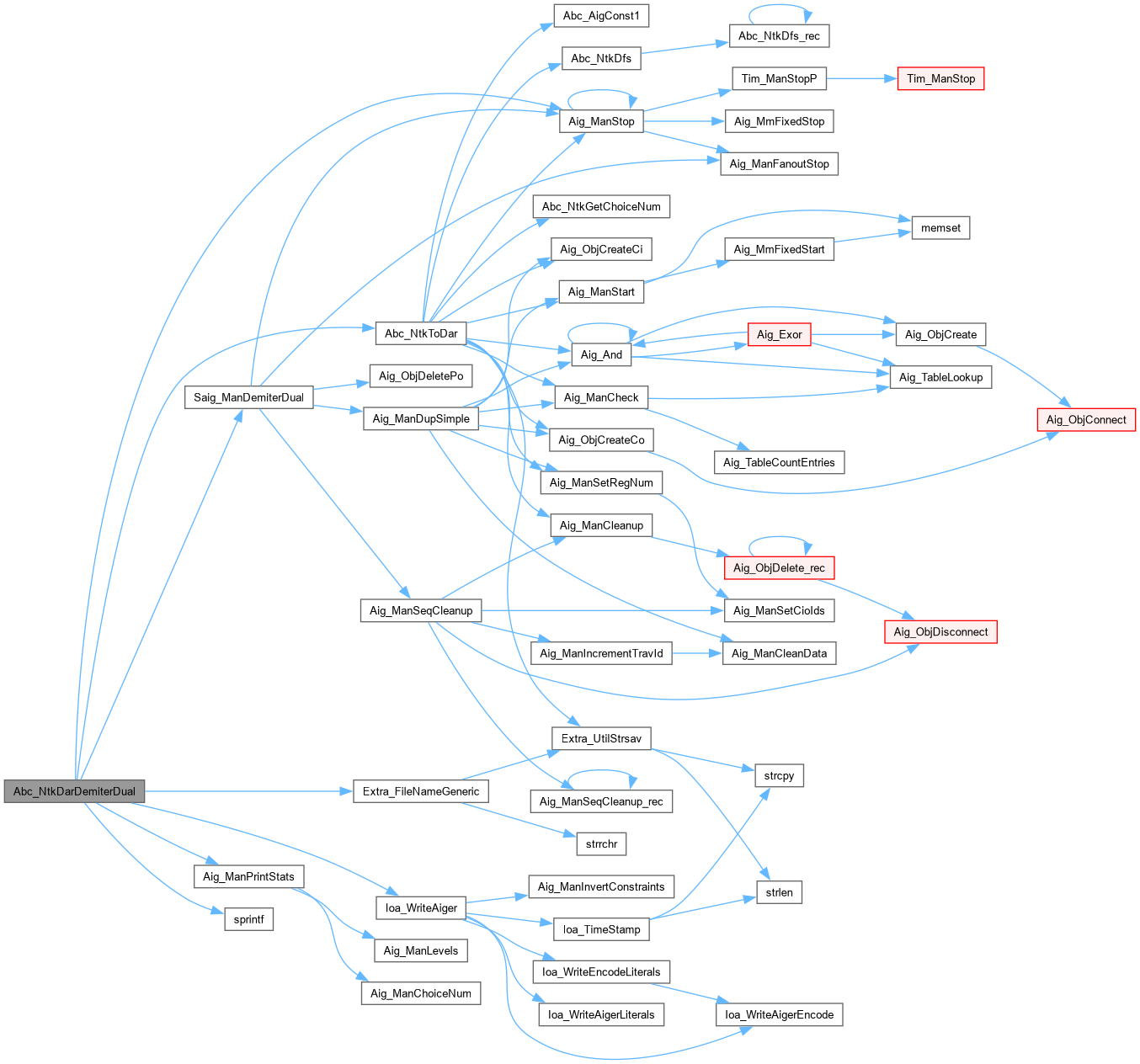

| int | Abc_NtkDarDemiterDual (Abc_Ntk_t *pNtk, int fVerbose) |

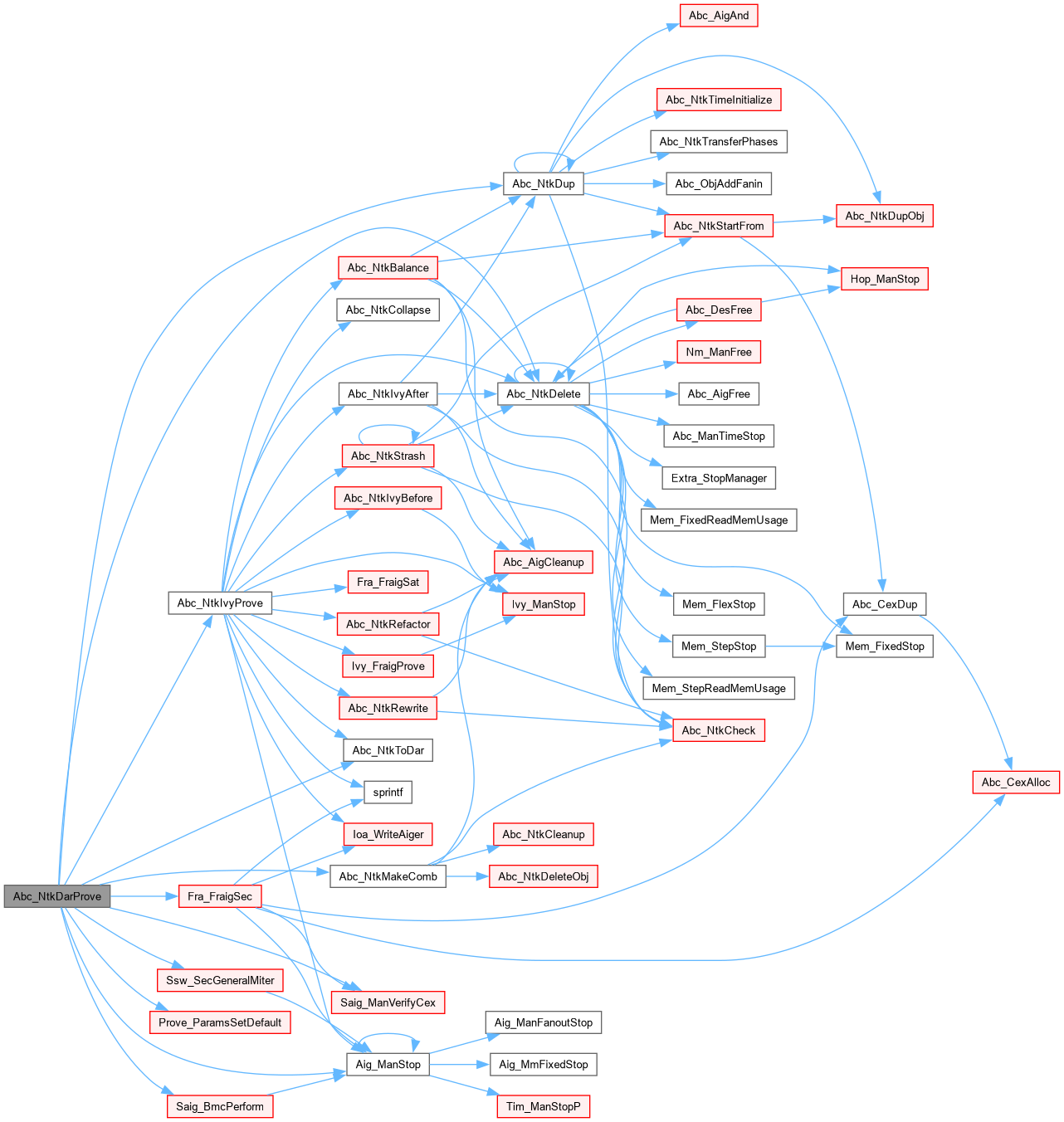

| int | Abc_NtkDarProve (Abc_Ntk_t *pNtk, Fra_Sec_t *pSecPar, int nBmcFramesMax, int nBmcConfMax) |

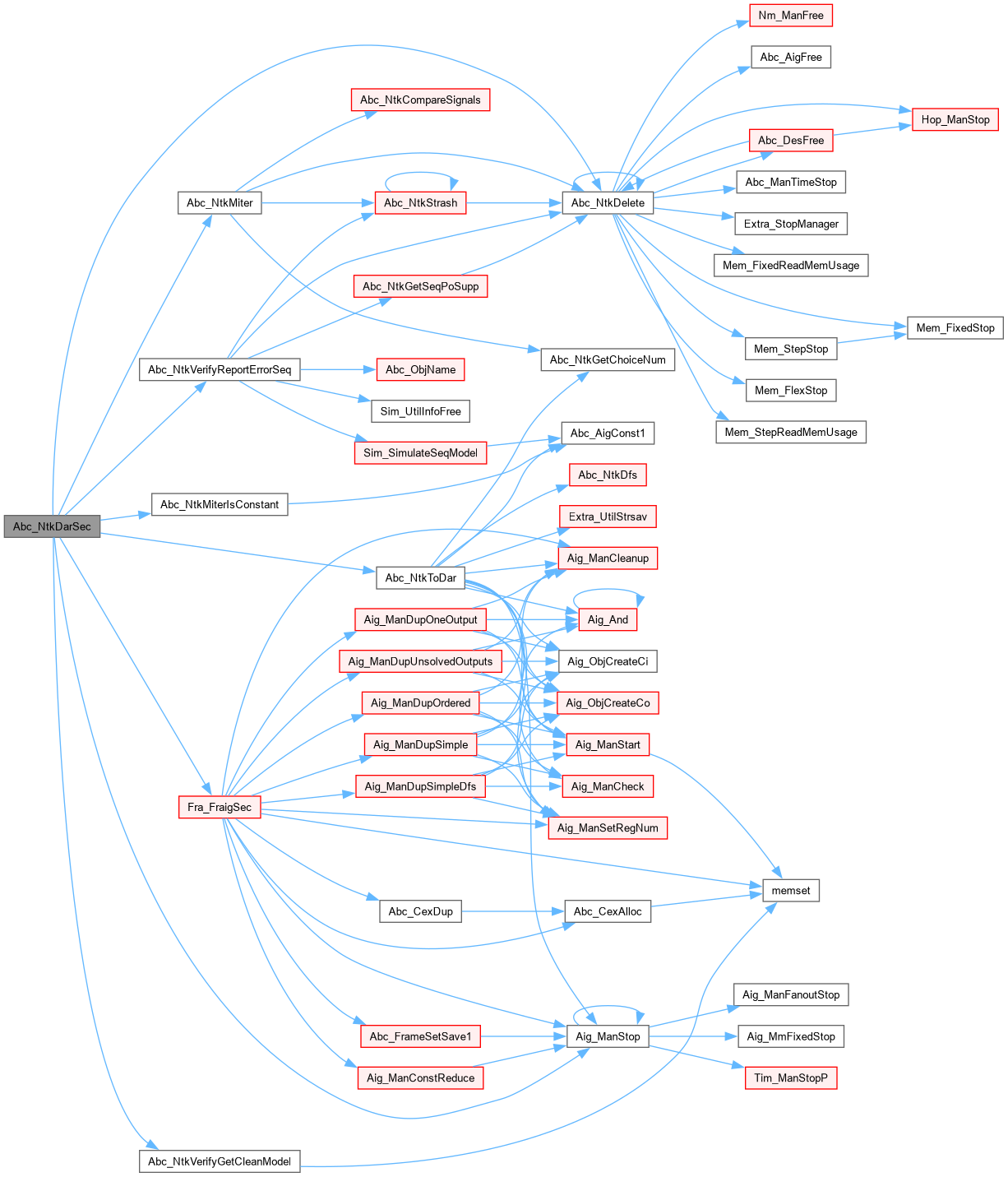

| int | Abc_NtkDarSec (Abc_Ntk_t *pNtk1, Abc_Ntk_t *pNtk2, Fra_Sec_t *pSecPar) |

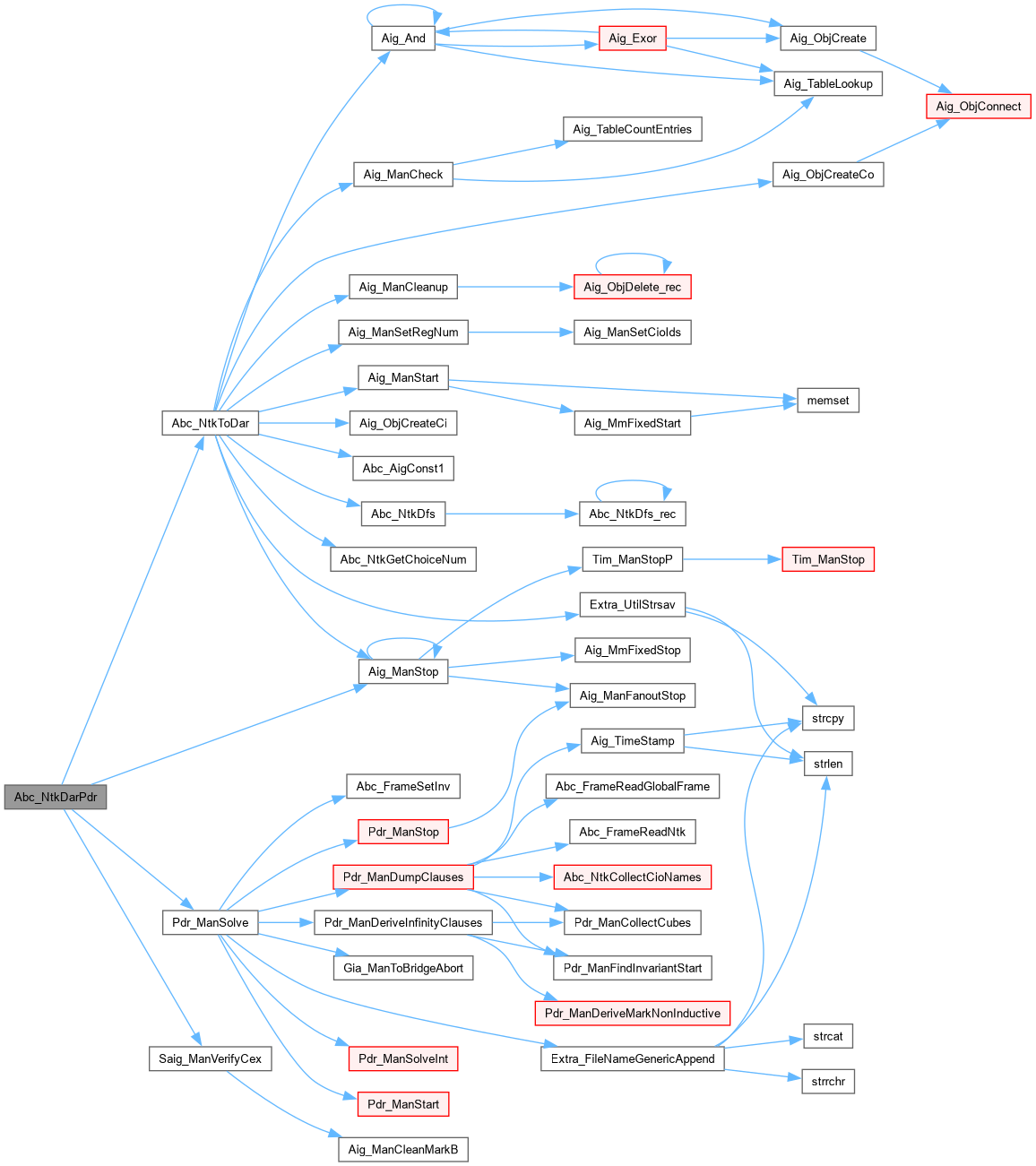

| int | Abc_NtkDarPdr (Abc_Ntk_t *pNtk, Pdr_Par_t *pPars) |

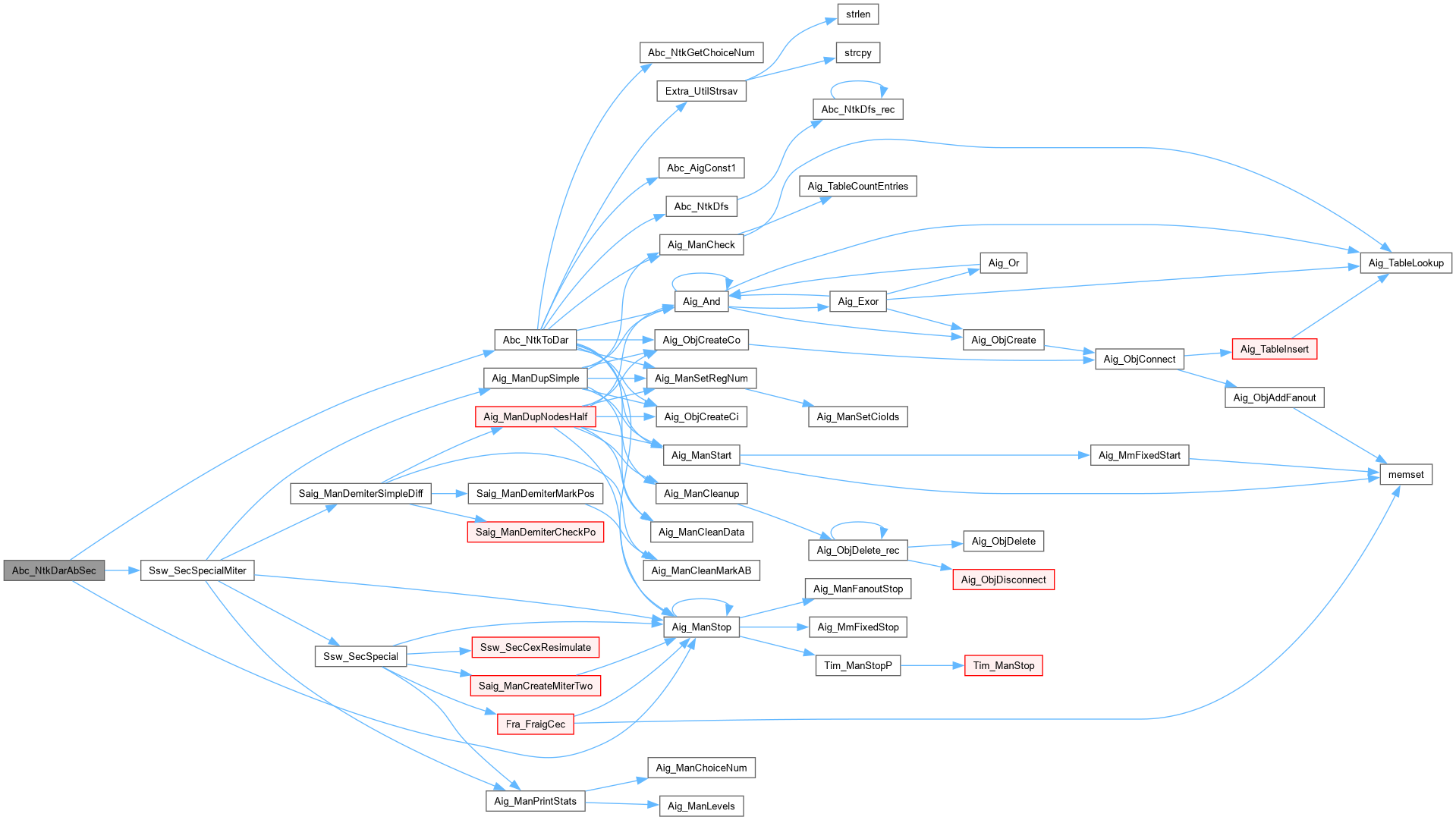

| int | Abc_NtkDarAbSec (Abc_Ntk_t *pNtk1, Abc_Ntk_t *pNtk2, int nFrames, int fVerbose) |

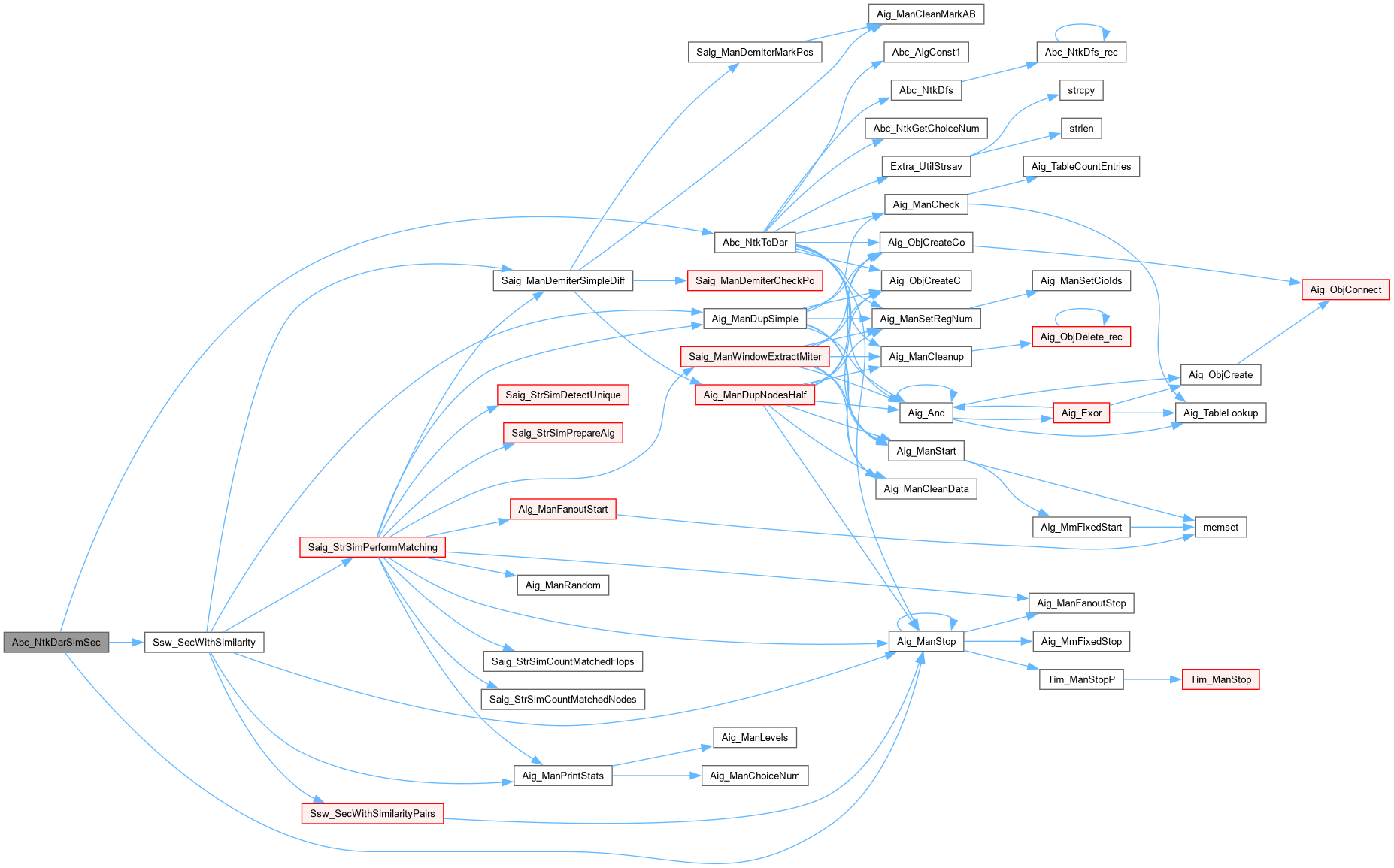

| int | Abc_NtkDarSimSec (Abc_Ntk_t *pNtk1, Abc_Ntk_t *pNtk2, Ssw_Pars_t *pPars) |

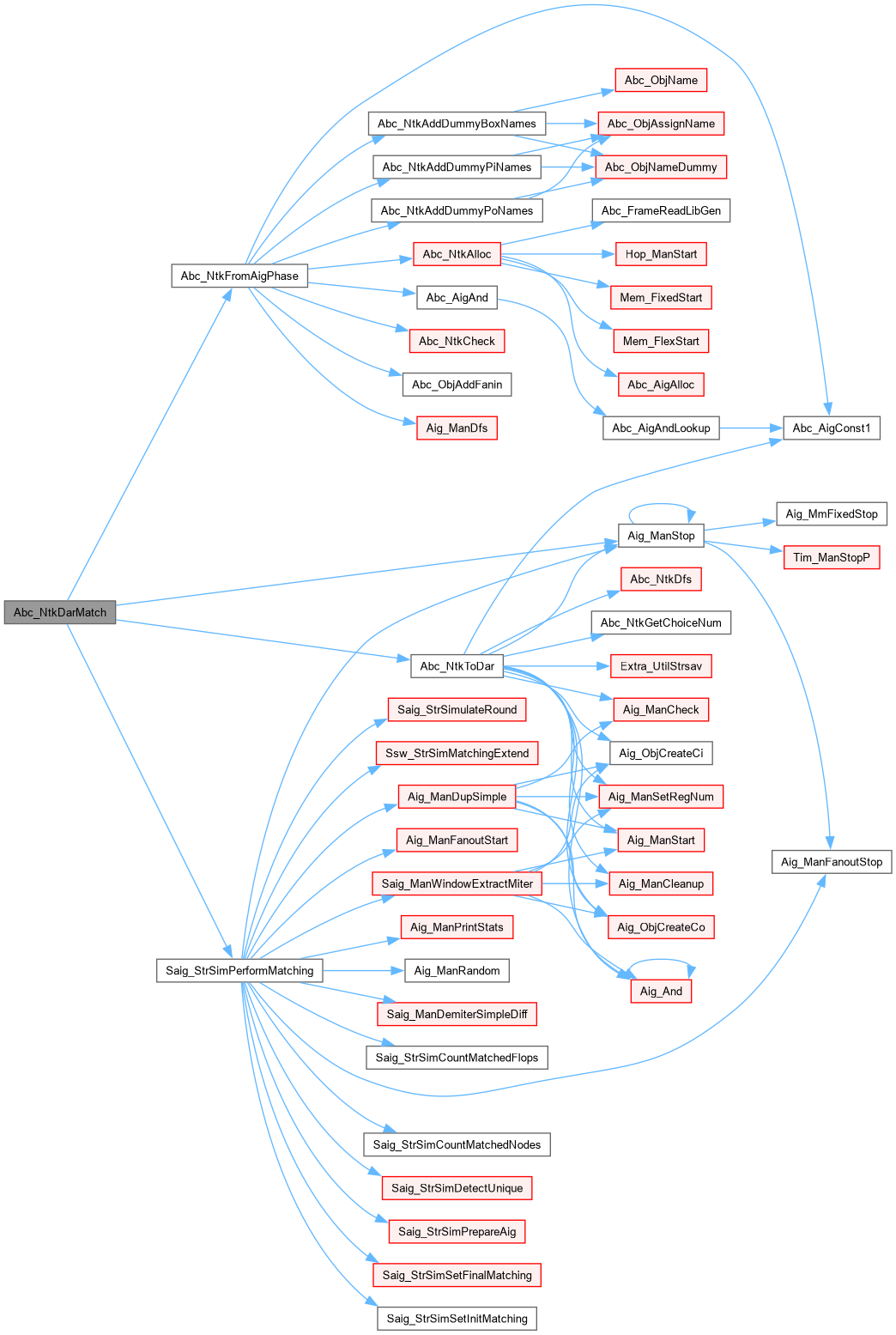

| Abc_Ntk_t * | Abc_NtkDarMatch (Abc_Ntk_t *pNtk1, Abc_Ntk_t *pNtk2, int nDist, int fVerbose) |

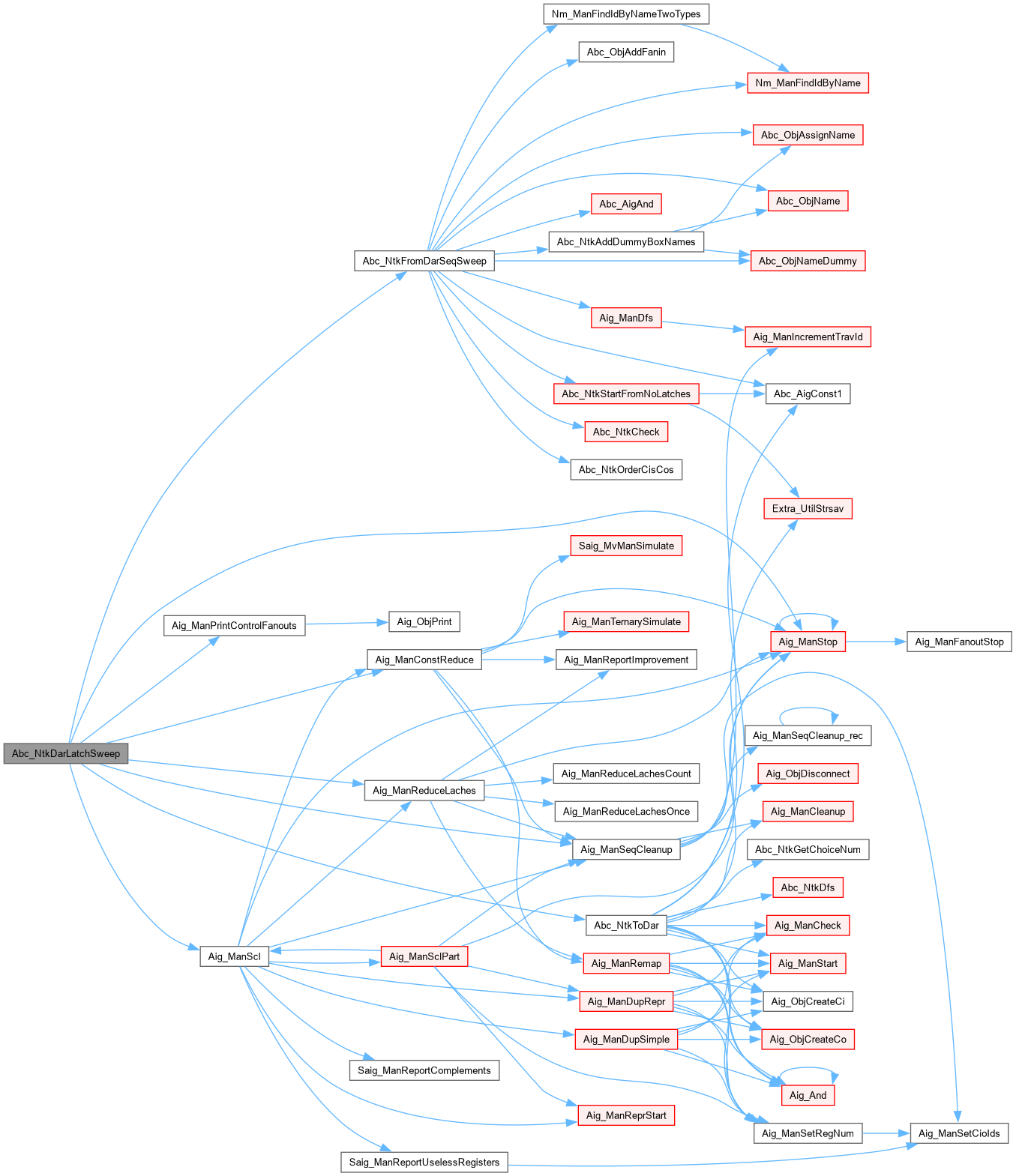

| Abc_Ntk_t * | Abc_NtkDarLatchSweep (Abc_Ntk_t *pNtk, int fLatchConst, int fLatchEqual, int fSaveNames, int fUseMvSweep, int nFramesSymb, int nFramesSatur, int fVerbose, int fVeryVerbose) |

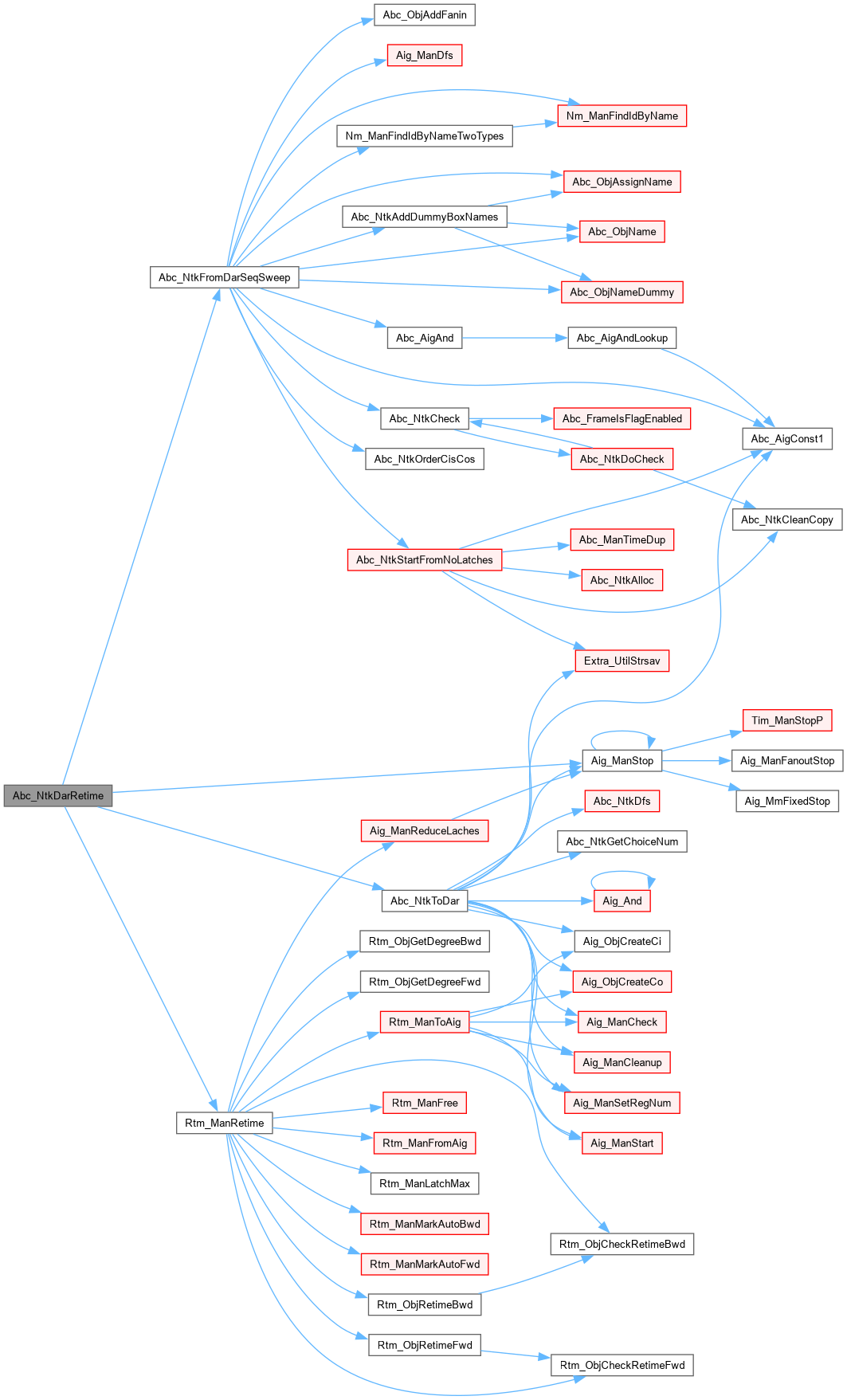

| Abc_Ntk_t * | Abc_NtkDarRetime (Abc_Ntk_t *pNtk, int nStepsMax, int fVerbose) |

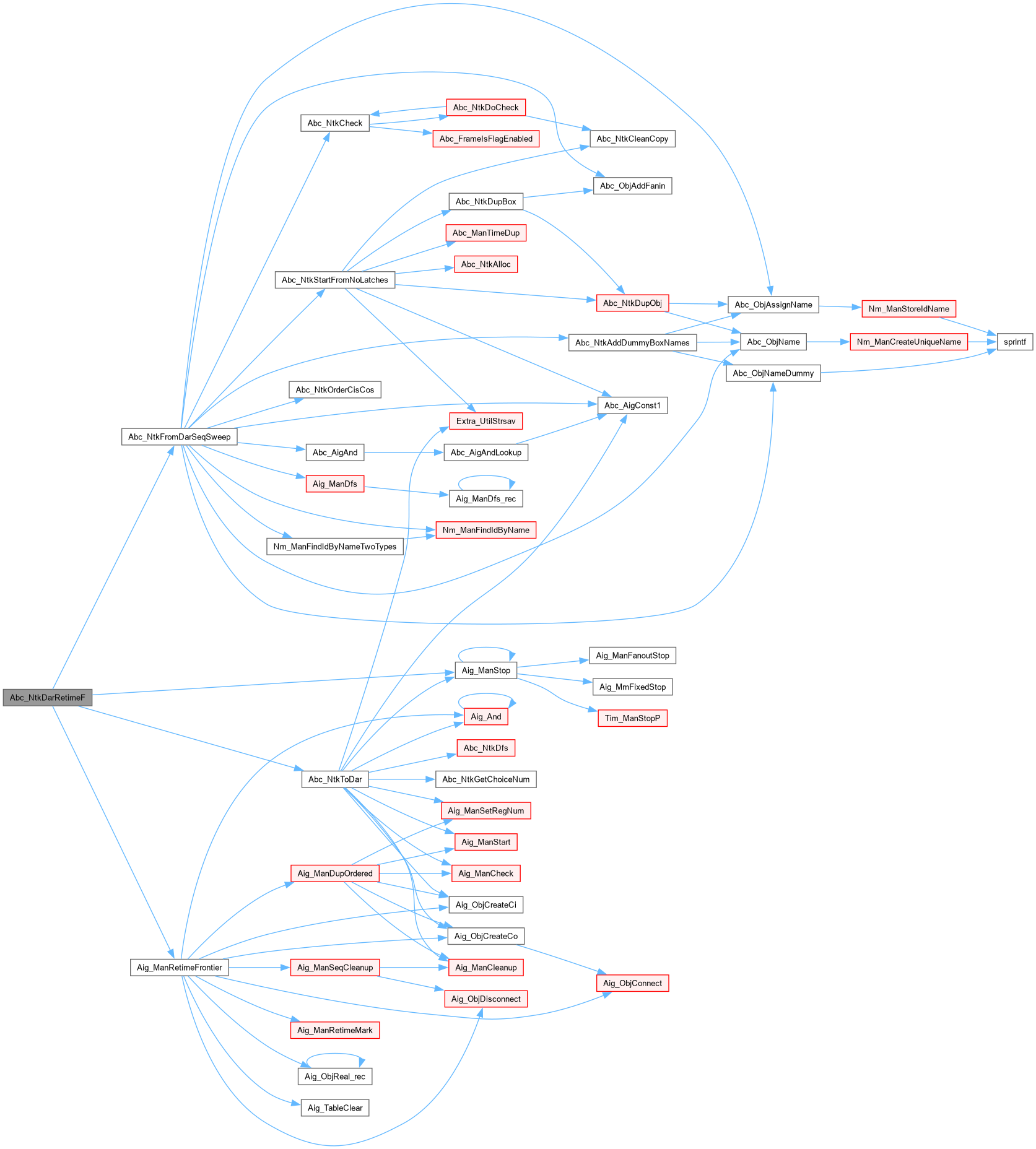

| Abc_Ntk_t * | Abc_NtkDarRetimeF (Abc_Ntk_t *pNtk, int nStepsMax, int fVerbose) |

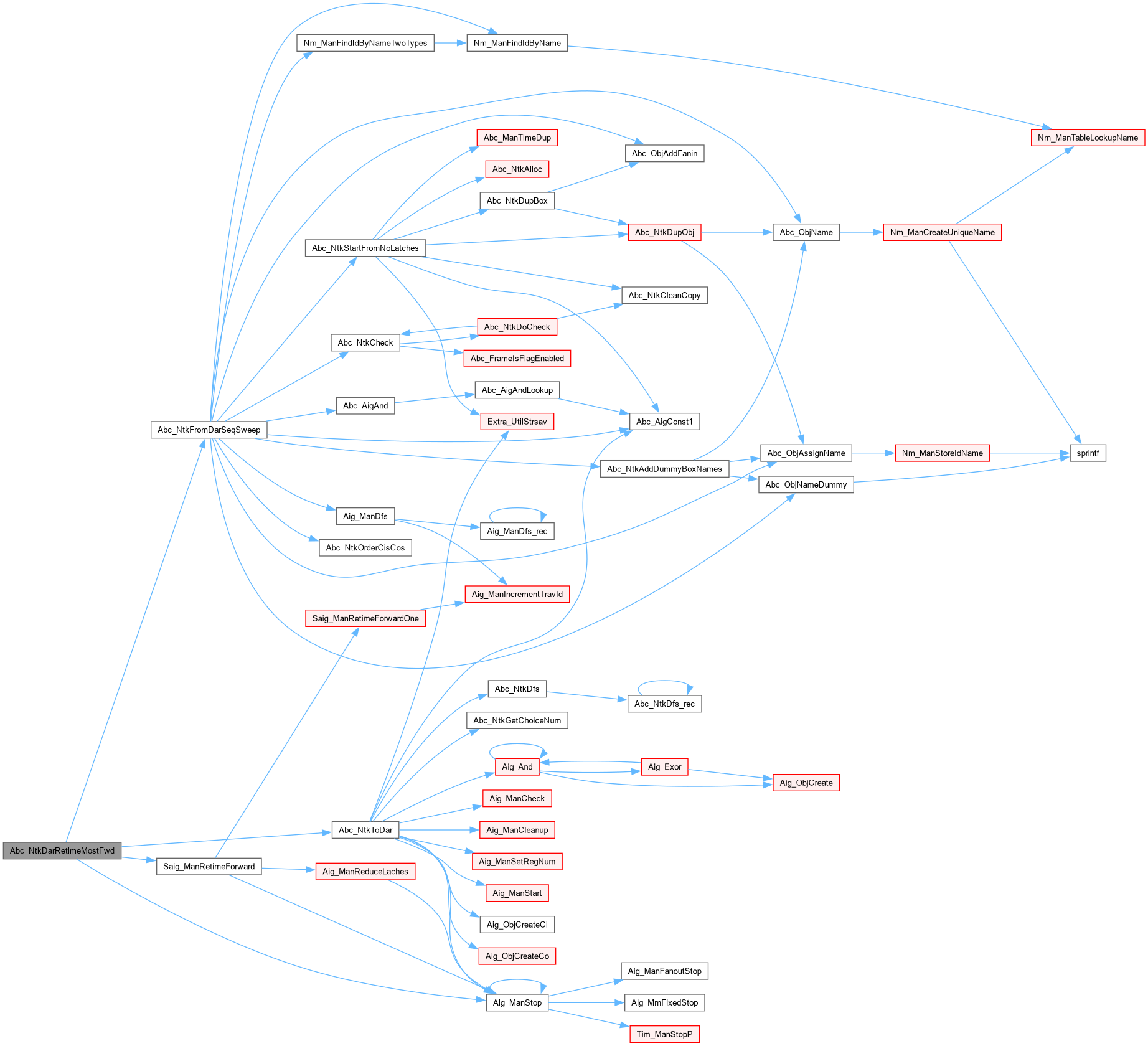

| Abc_Ntk_t * | Abc_NtkDarRetimeMostFwd (Abc_Ntk_t *pNtk, int nMaxIters, int fVerbose) |

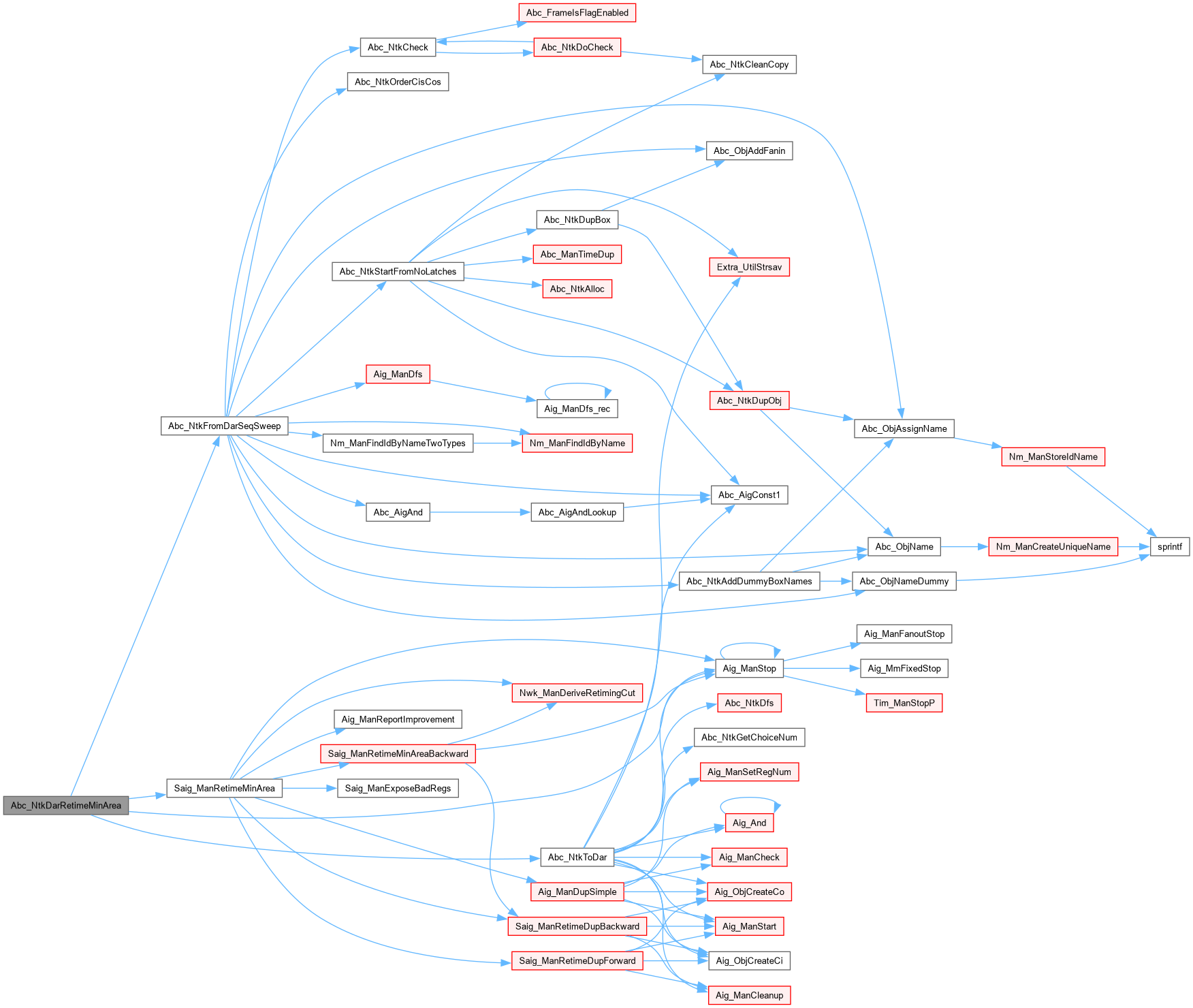

| Abc_Ntk_t * | Abc_NtkDarRetimeMinArea (Abc_Ntk_t *pNtk, int nMaxIters, int fForwardOnly, int fBackwardOnly, int fInitial, int fVerbose) |

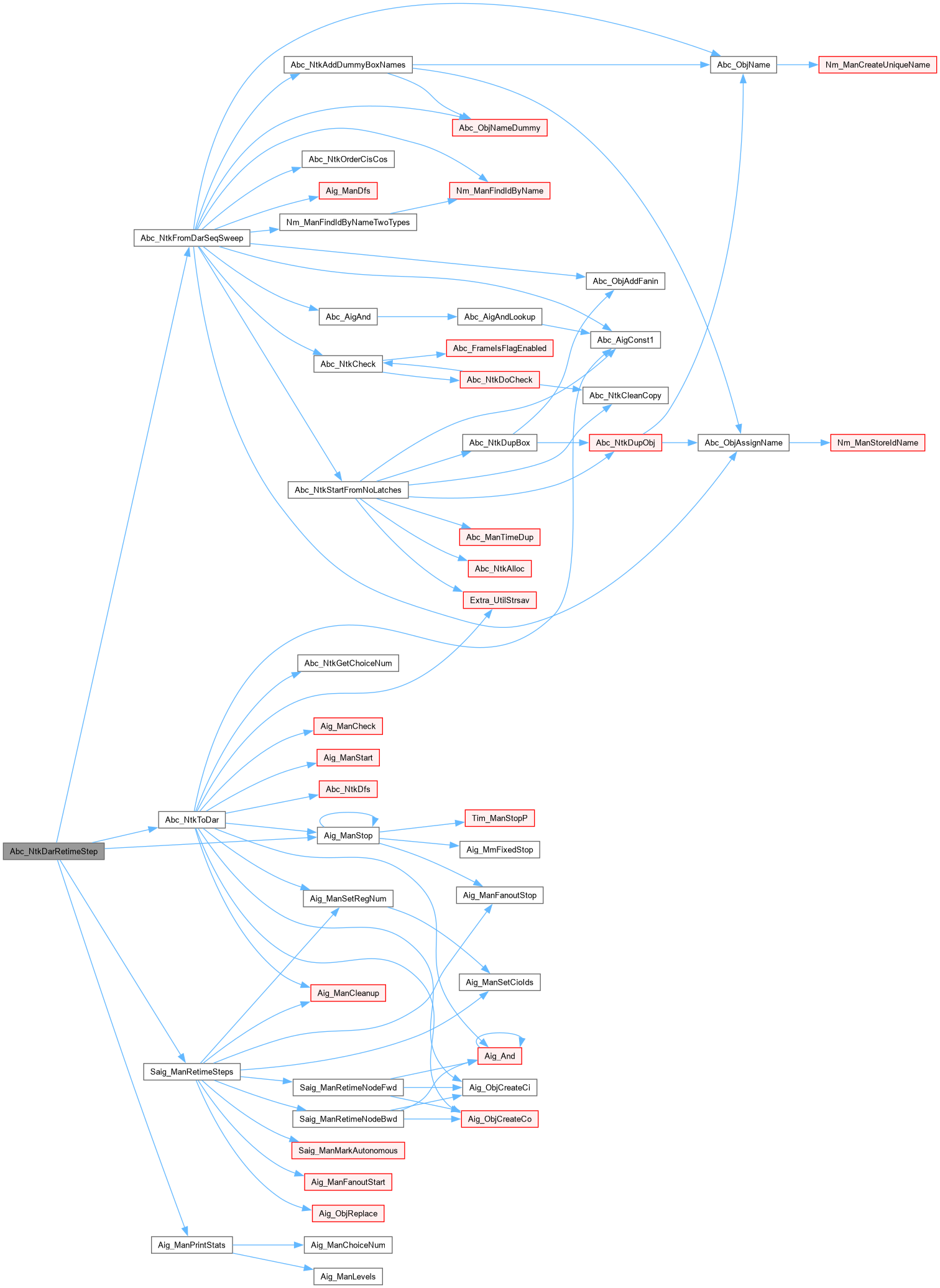

| Abc_Ntk_t * | Abc_NtkDarRetimeStep (Abc_Ntk_t *pNtk, int fVerbose) |

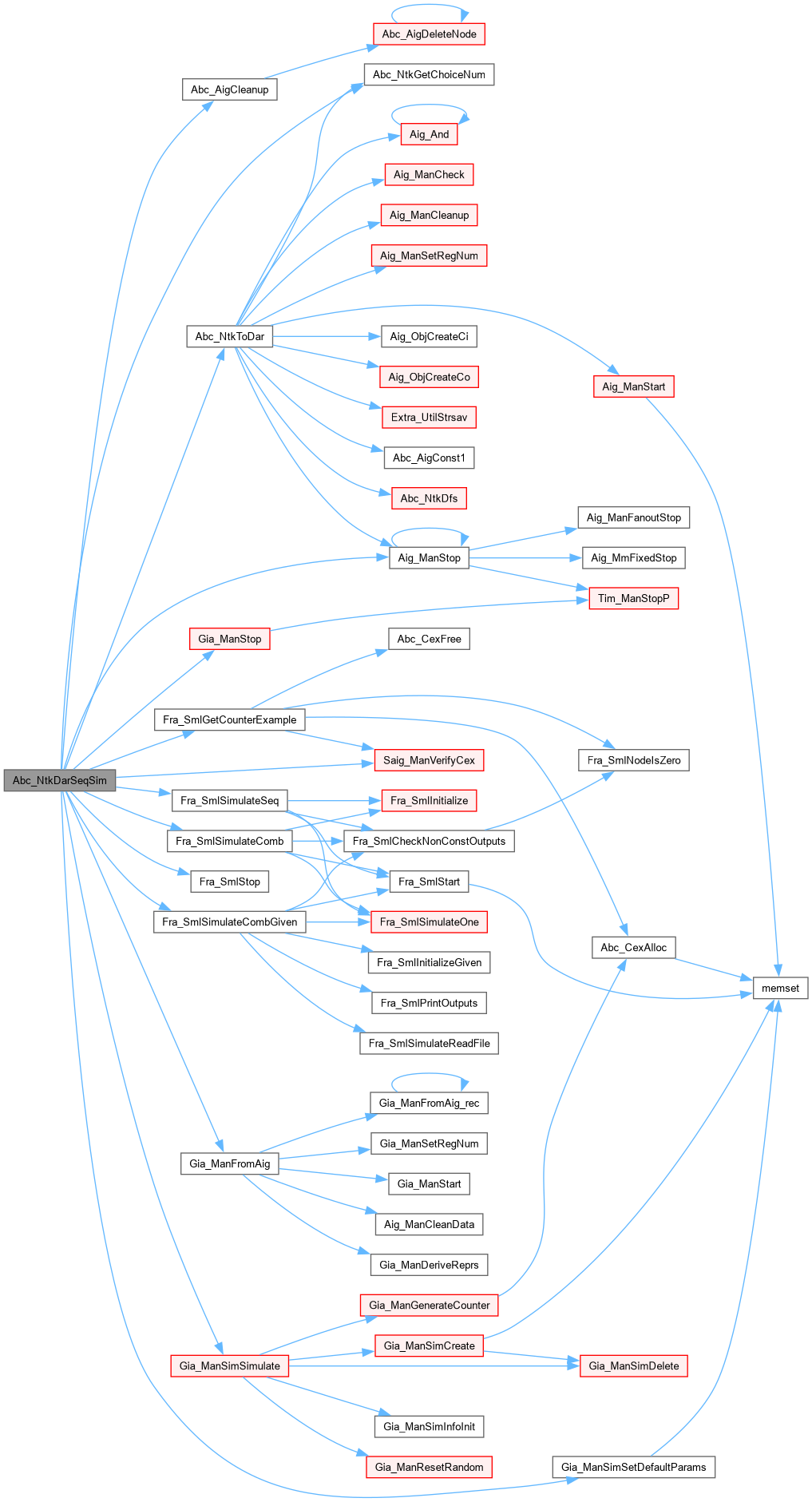

| int | Abc_NtkDarSeqSim (Abc_Ntk_t *pNtk, int nFrames, int nWords, int TimeOut, int fNew, int fMiter, int fVerbose, char *pFileSim) |

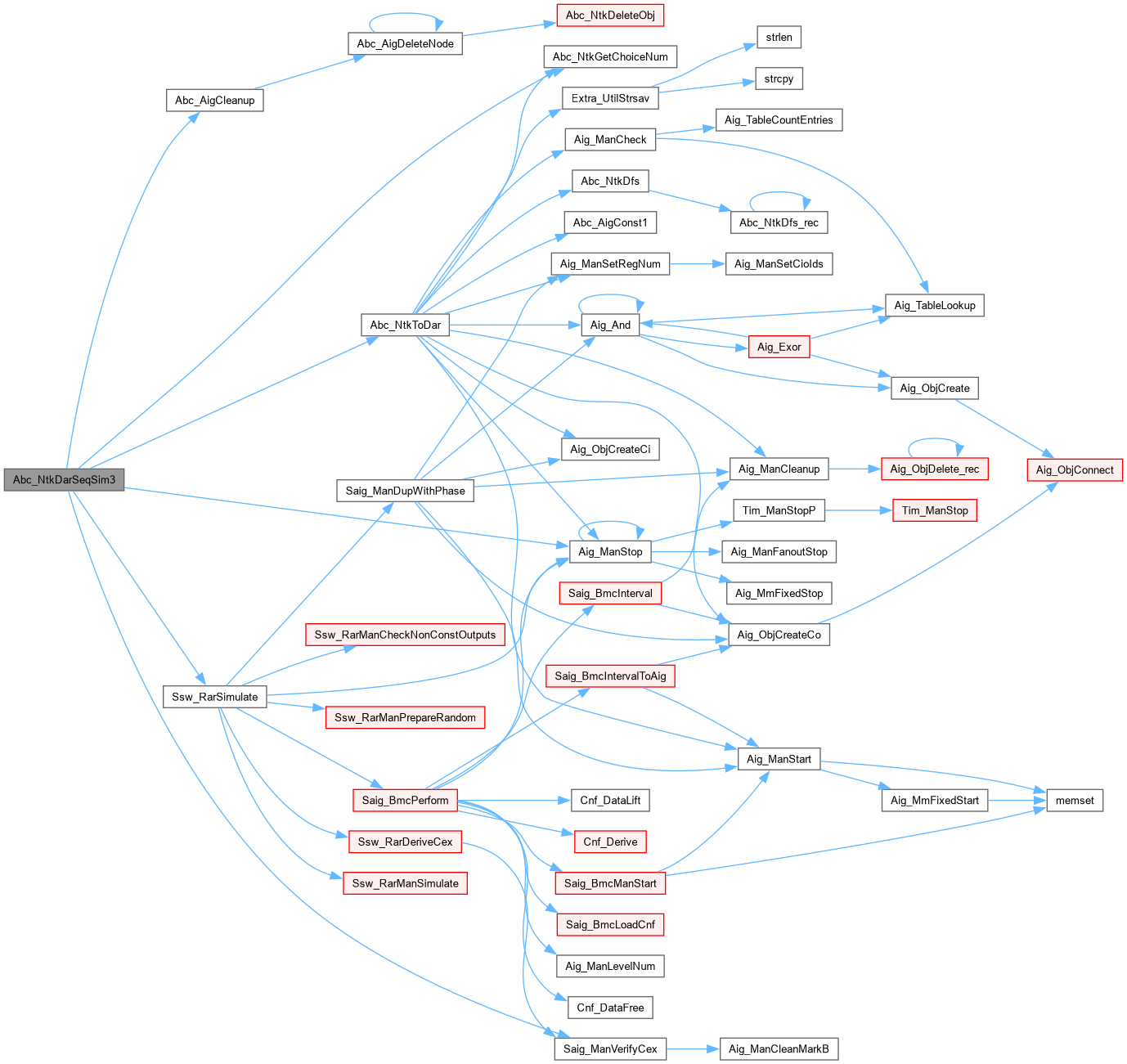

| int | Abc_NtkDarSeqSim3 (Abc_Ntk_t *pNtk, Ssw_RarPars_t *pPars) |

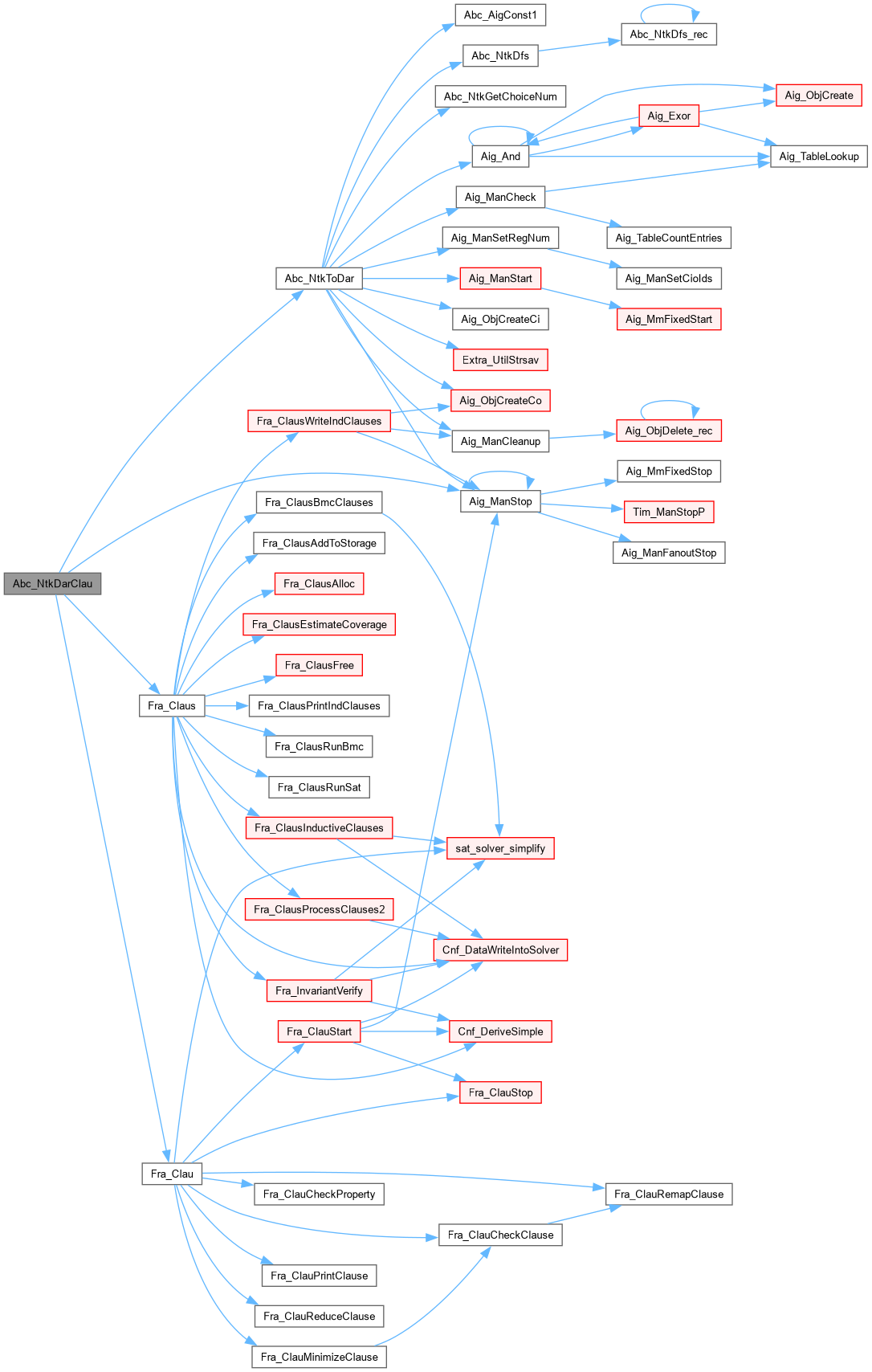

| int | Abc_NtkDarClau (Abc_Ntk_t *pNtk, int nFrames, int nPref, int nClauses, int nLutSize, int nLevels, int nCutsMax, int nBatches, int fStepUp, int fBmc, int fRefs, int fTarget, int fVerbose, int fVeryVerbose) |

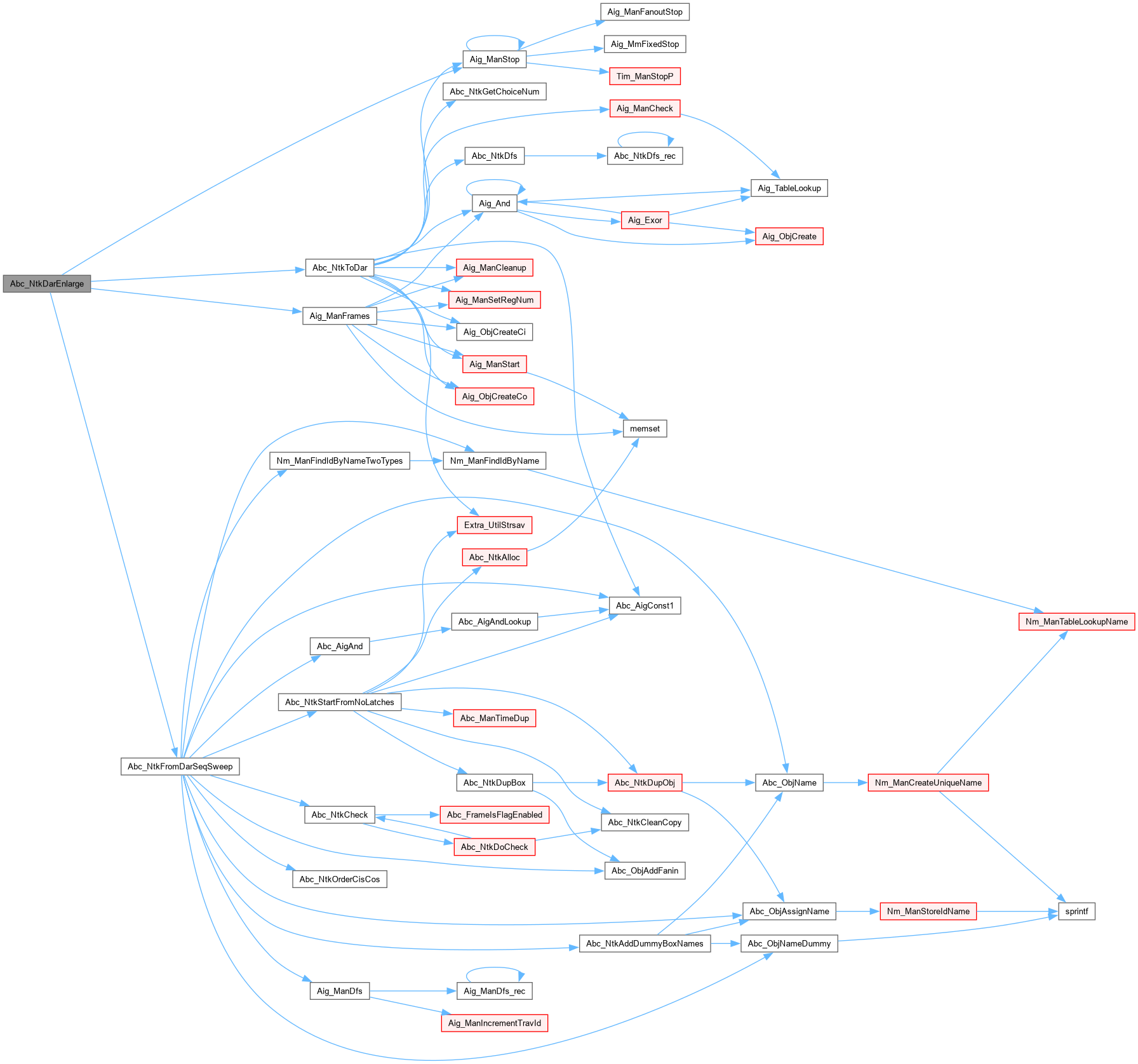

| Abc_Ntk_t * | Abc_NtkDarEnlarge (Abc_Ntk_t *pNtk, int nFrames, int fVerbose) |

| Abc_Ntk_t * | Abc_NtkDarTempor (Abc_Ntk_t *pNtk, int nFrames, int TimeOut, int nConfLimit, int fUseBmc, int fUseTransSigs, int fVerbose, int fVeryVerbose) |

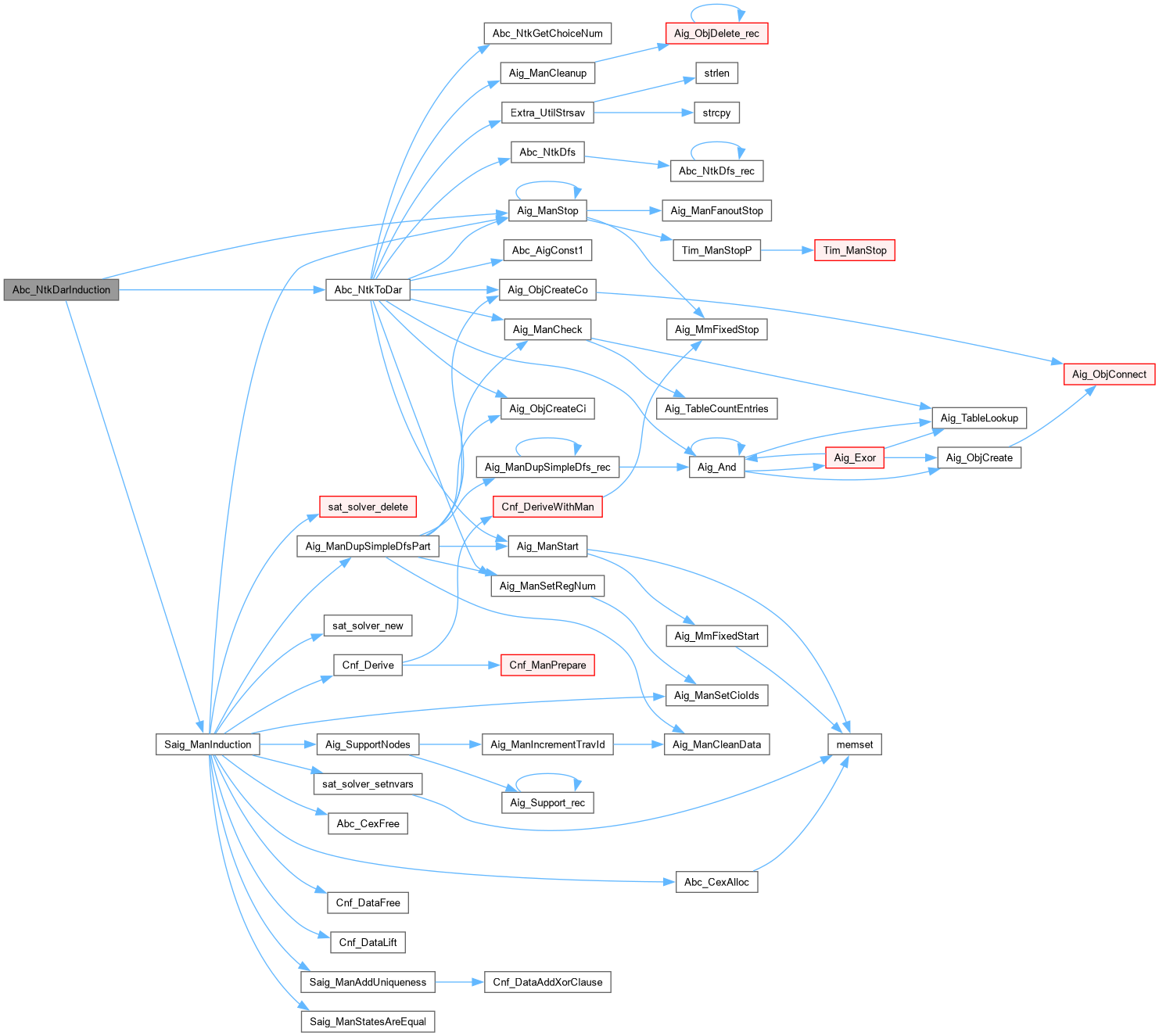

| int | Abc_NtkDarInduction (Abc_Ntk_t *pNtk, int nTimeOut, int nFramesMax, int nConfMax, int fUnique, int fUniqueAll, int fGetCex, int fVerbose, int fVeryVerbose) |

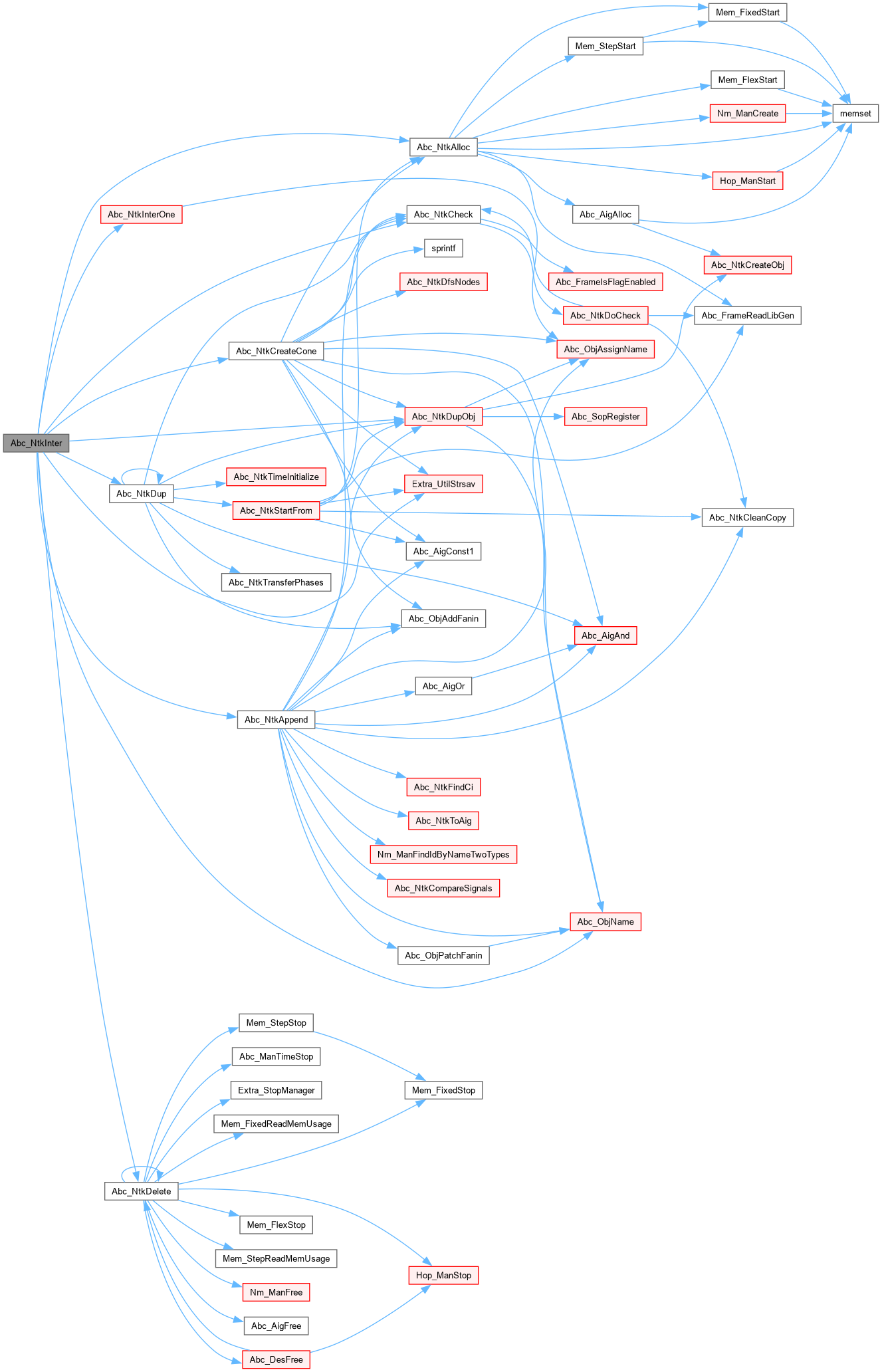

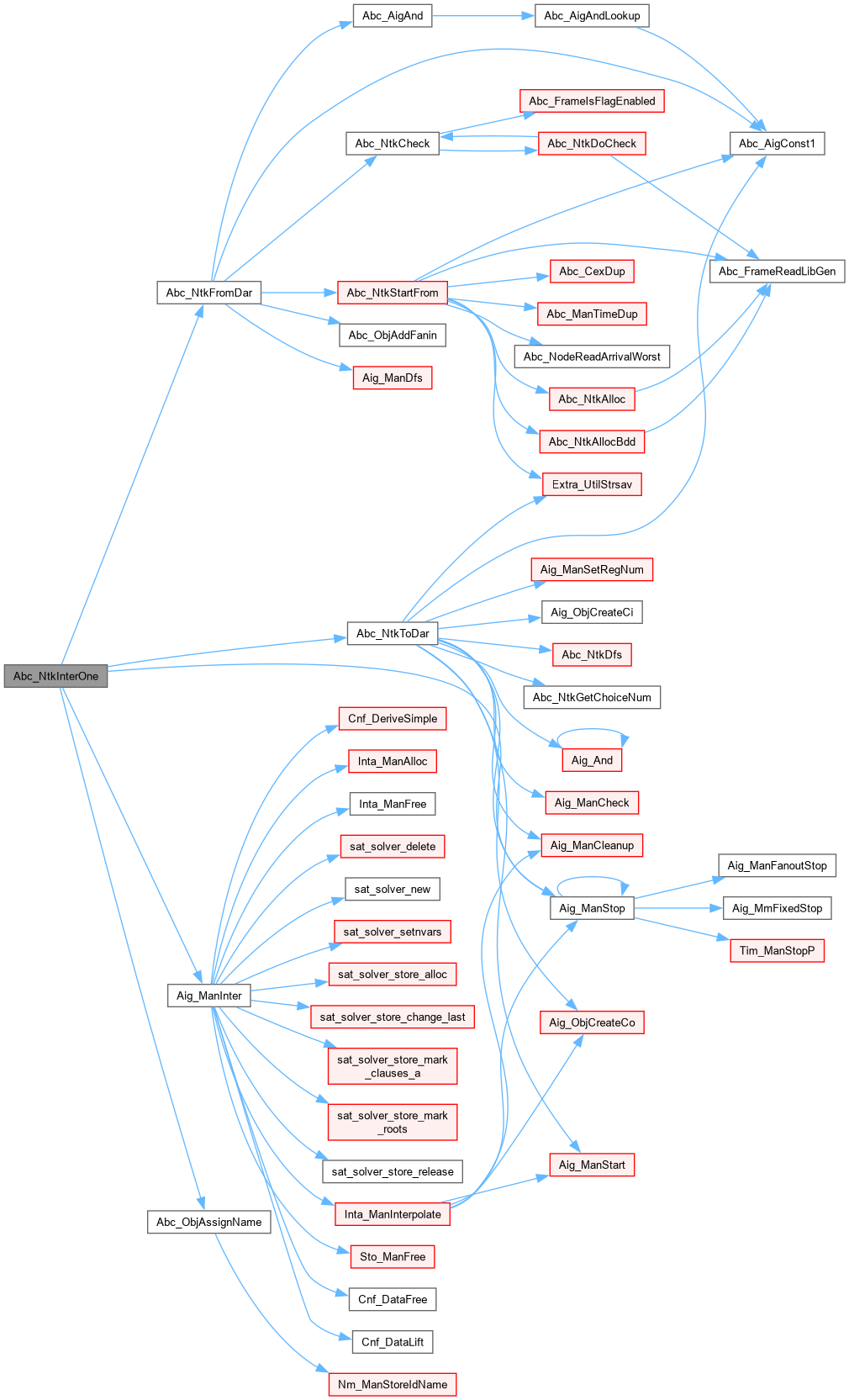

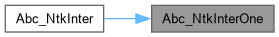

| Abc_Ntk_t * | Abc_NtkInterOne (Abc_Ntk_t *pNtkOn, Abc_Ntk_t *pNtkOff, int fRelation, int fVerbose) |

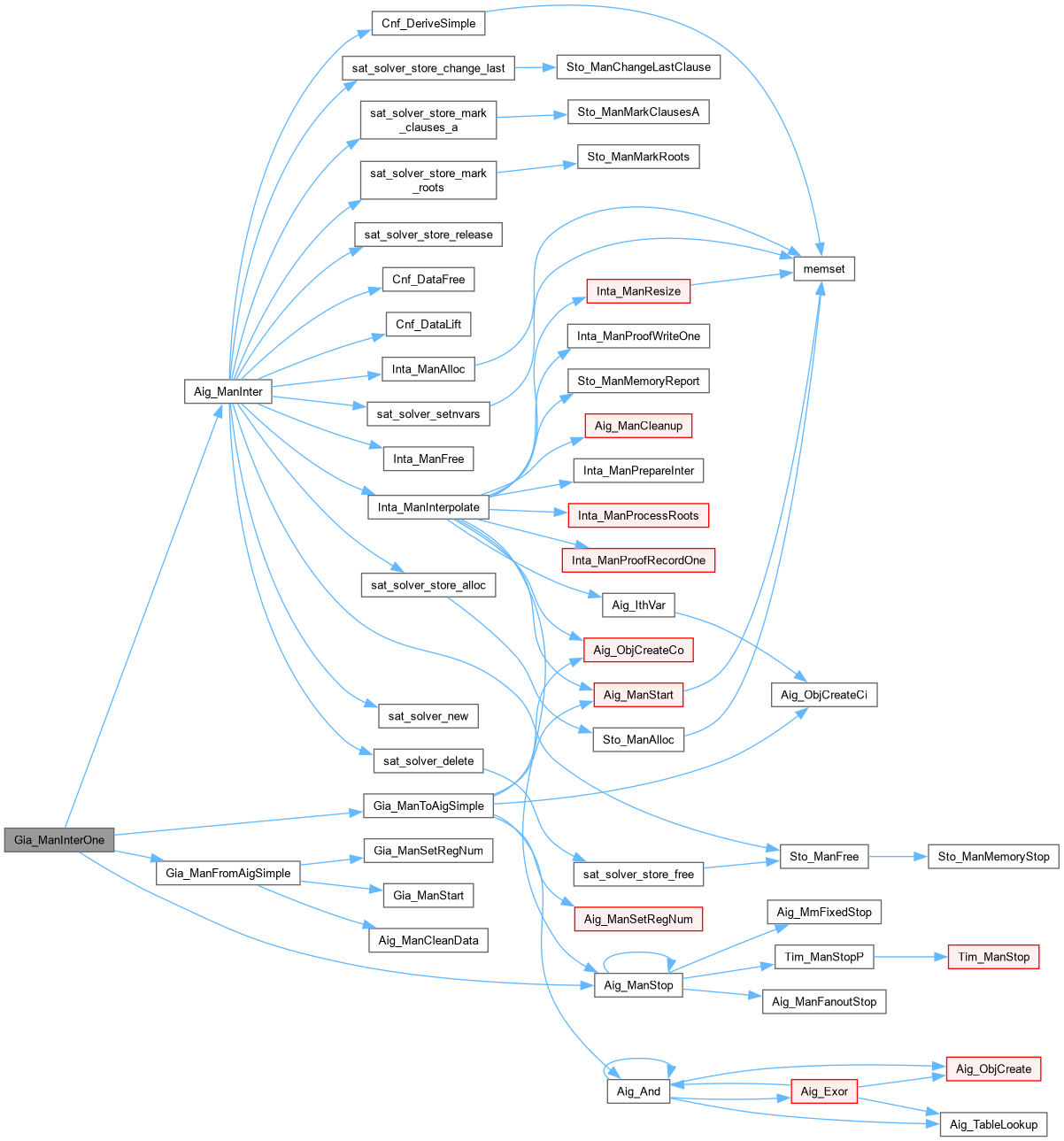

| Gia_Man_t * | Gia_ManInterOne (Gia_Man_t *pNtkOn, Gia_Man_t *pNtkOff, int fVerbose) |

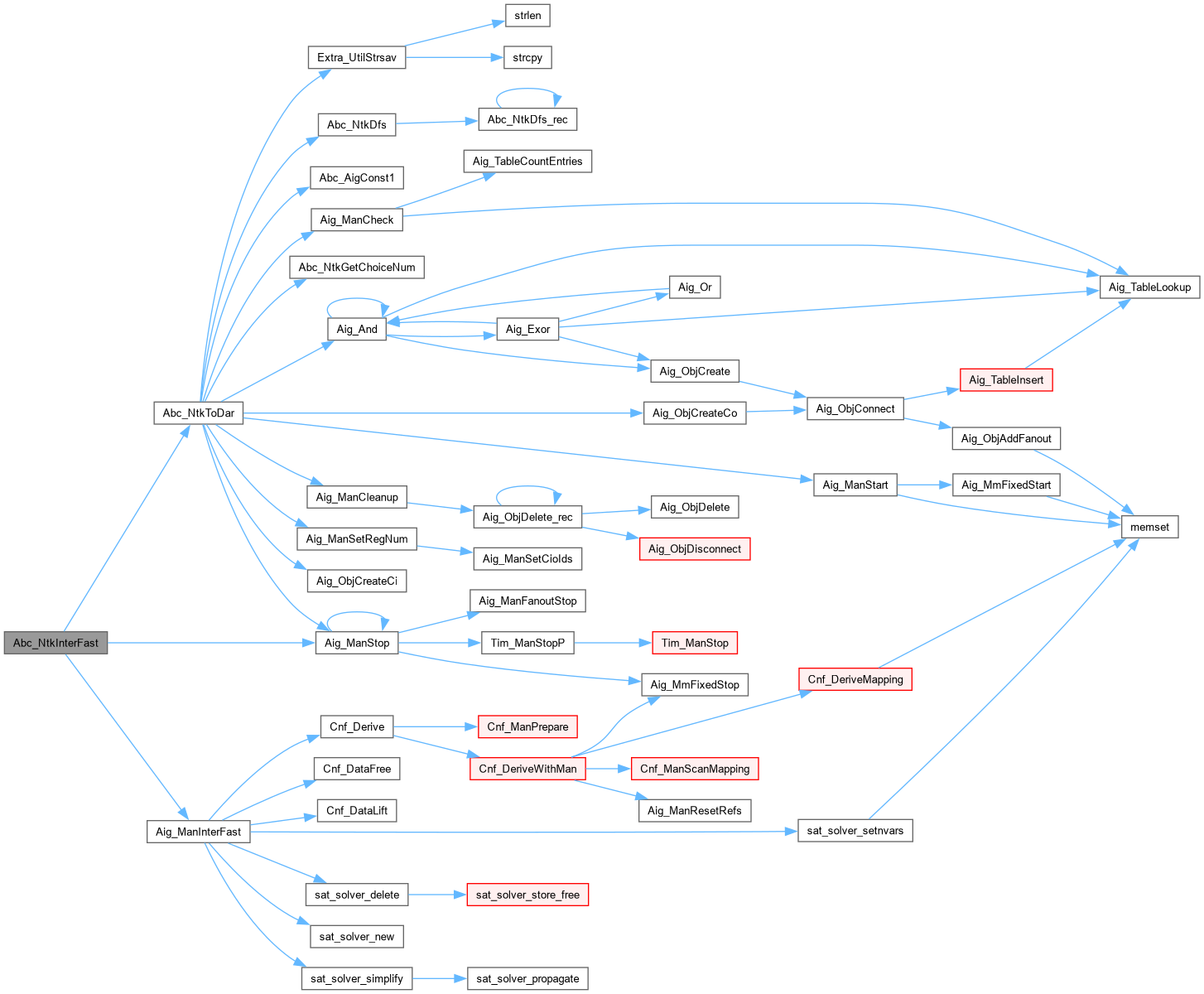

| void | Abc_NtkInterFast (Abc_Ntk_t *pNtkOn, Abc_Ntk_t *pNtkOff, int fVerbose) |

| Abc_Ntk_t * | Abc_NtkInter (Abc_Ntk_t *pNtkOn, Abc_Ntk_t *pNtkOff, int fRelation, int fVerbose) |

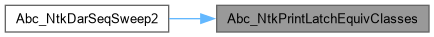

| void | Abc_NtkPrintSccs (Abc_Ntk_t *pNtk, int fVerbose) |

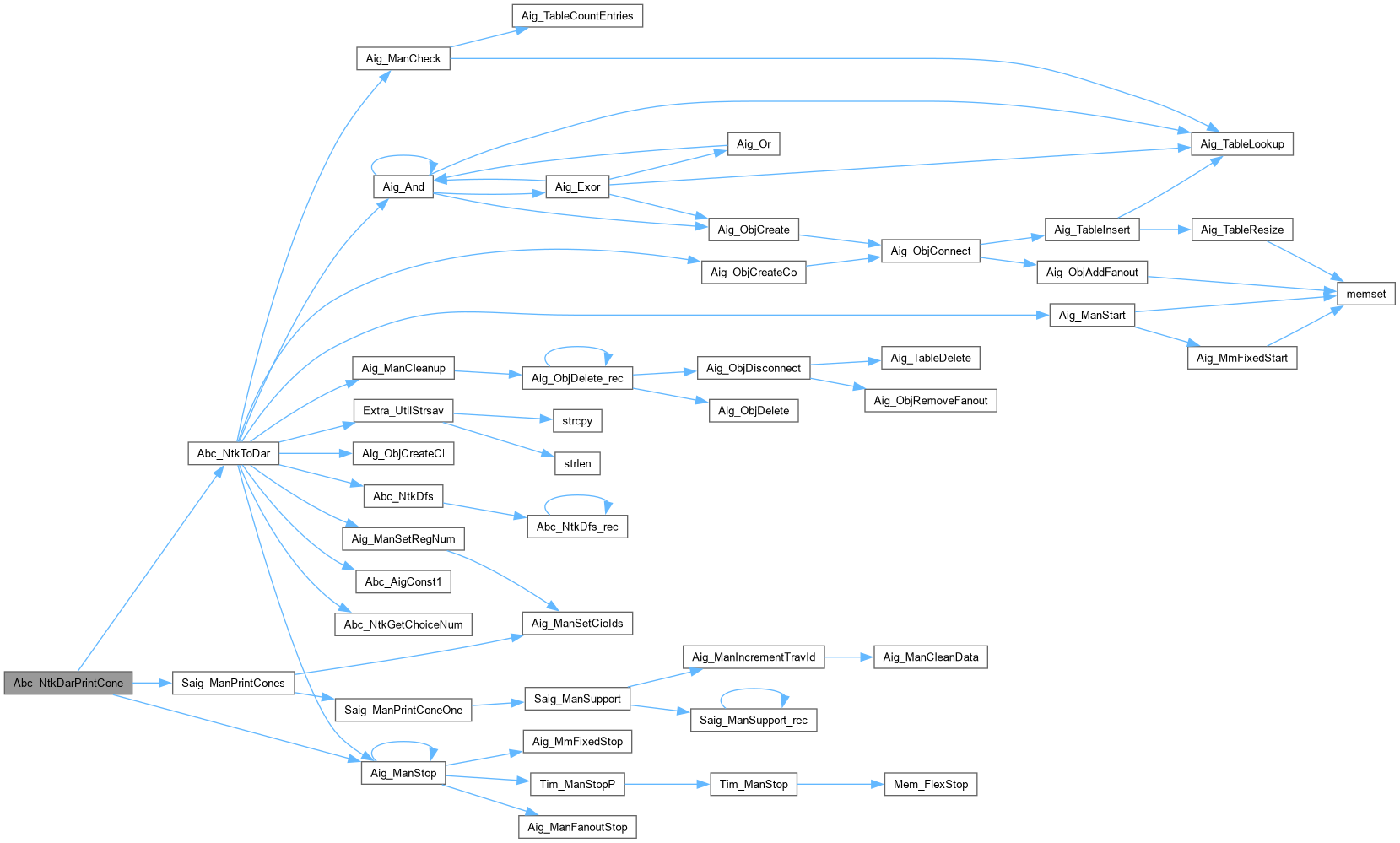

| int | Abc_NtkDarPrintCone (Abc_Ntk_t *pNtk) |

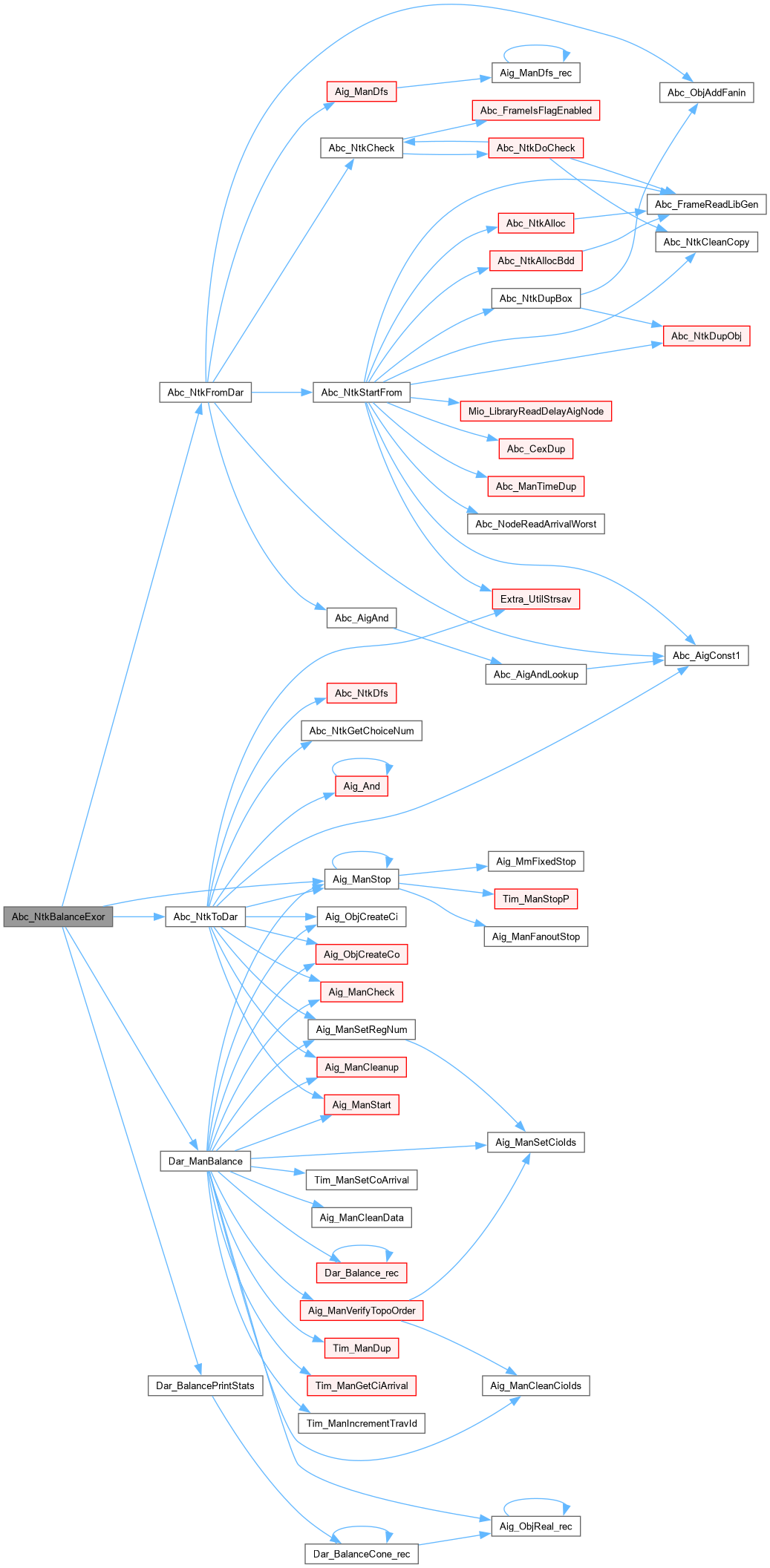

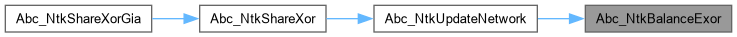

| Abc_Ntk_t * | Abc_NtkBalanceExor (Abc_Ntk_t *pNtk, int fUpdateLevel, int fVerbose) |

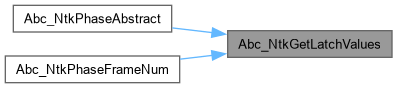

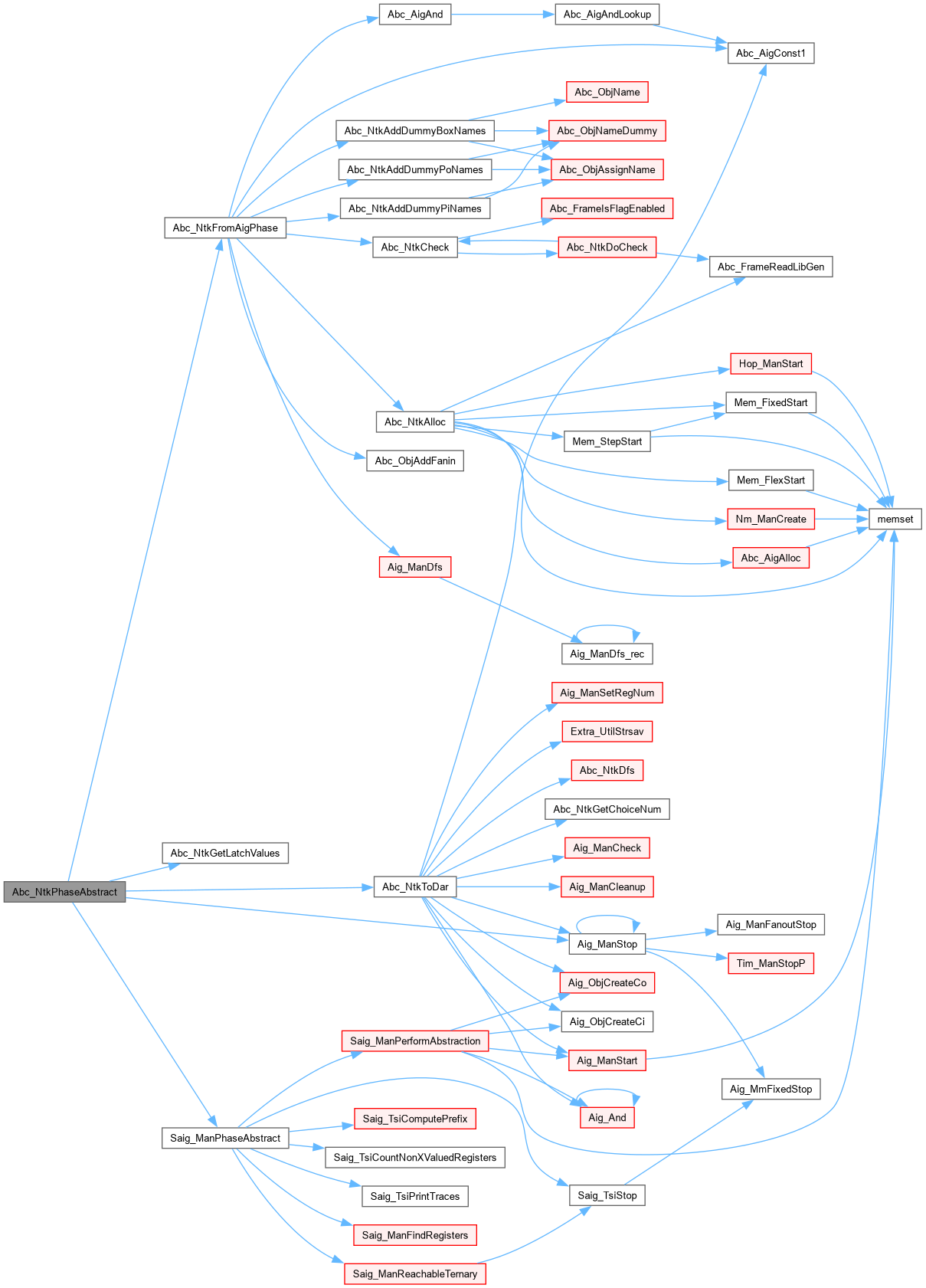

| Abc_Ntk_t * | Abc_NtkPhaseAbstract (Abc_Ntk_t *pNtk, int nFrames, int nPref, int fIgnore, int fPrint, int fVerbose) |

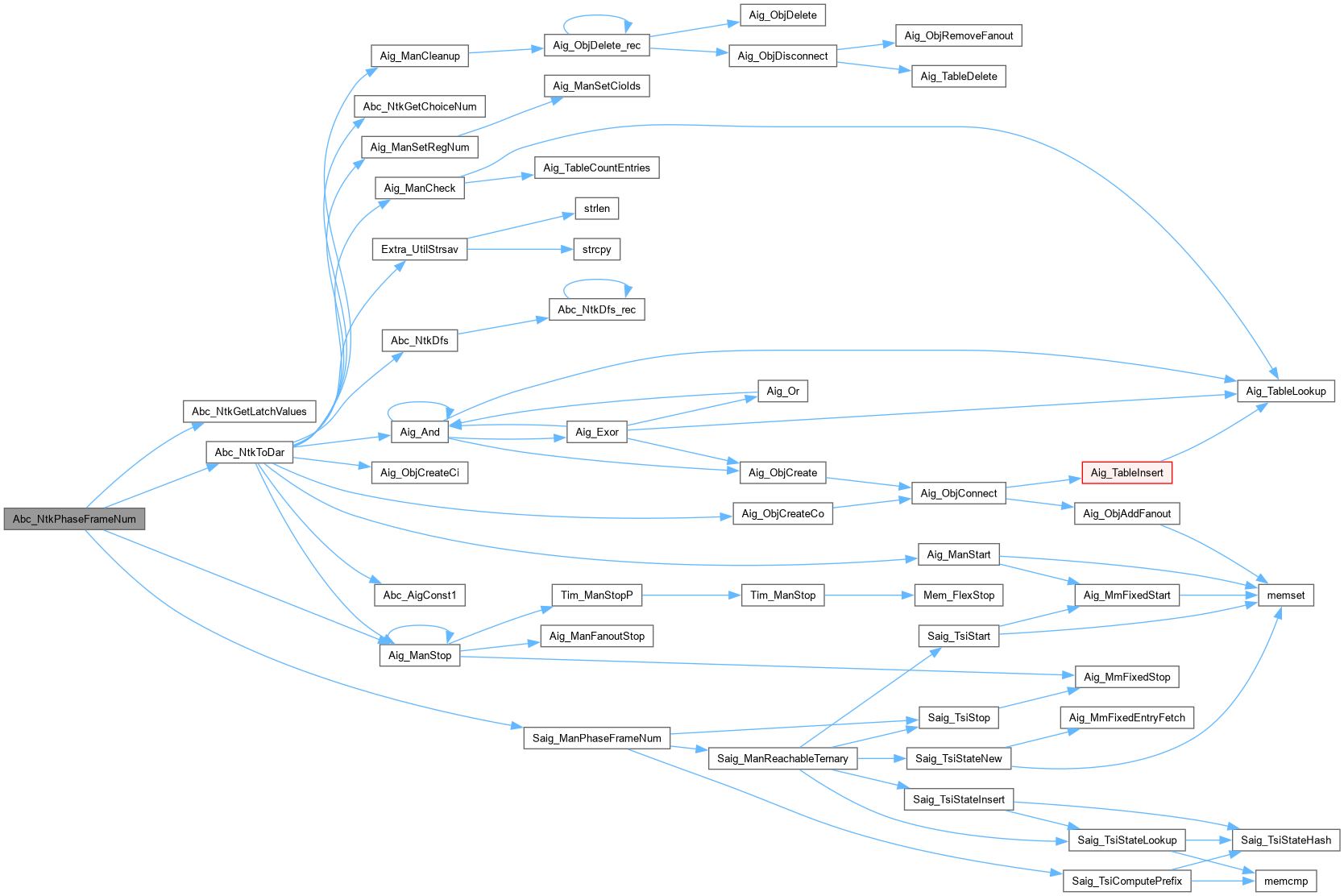

| int | Abc_NtkPhaseFrameNum (Abc_Ntk_t *pNtk) |

| Abc_Ntk_t * | Abc_NtkDarSynchOne (Abc_Ntk_t *pNtk, int nWords, int fVerbose) |

| Abc_Ntk_t * | Abc_NtkDarSynch (Abc_Ntk_t *pNtk1, Abc_Ntk_t *pNtk2, int nWords, int fVerbose) |

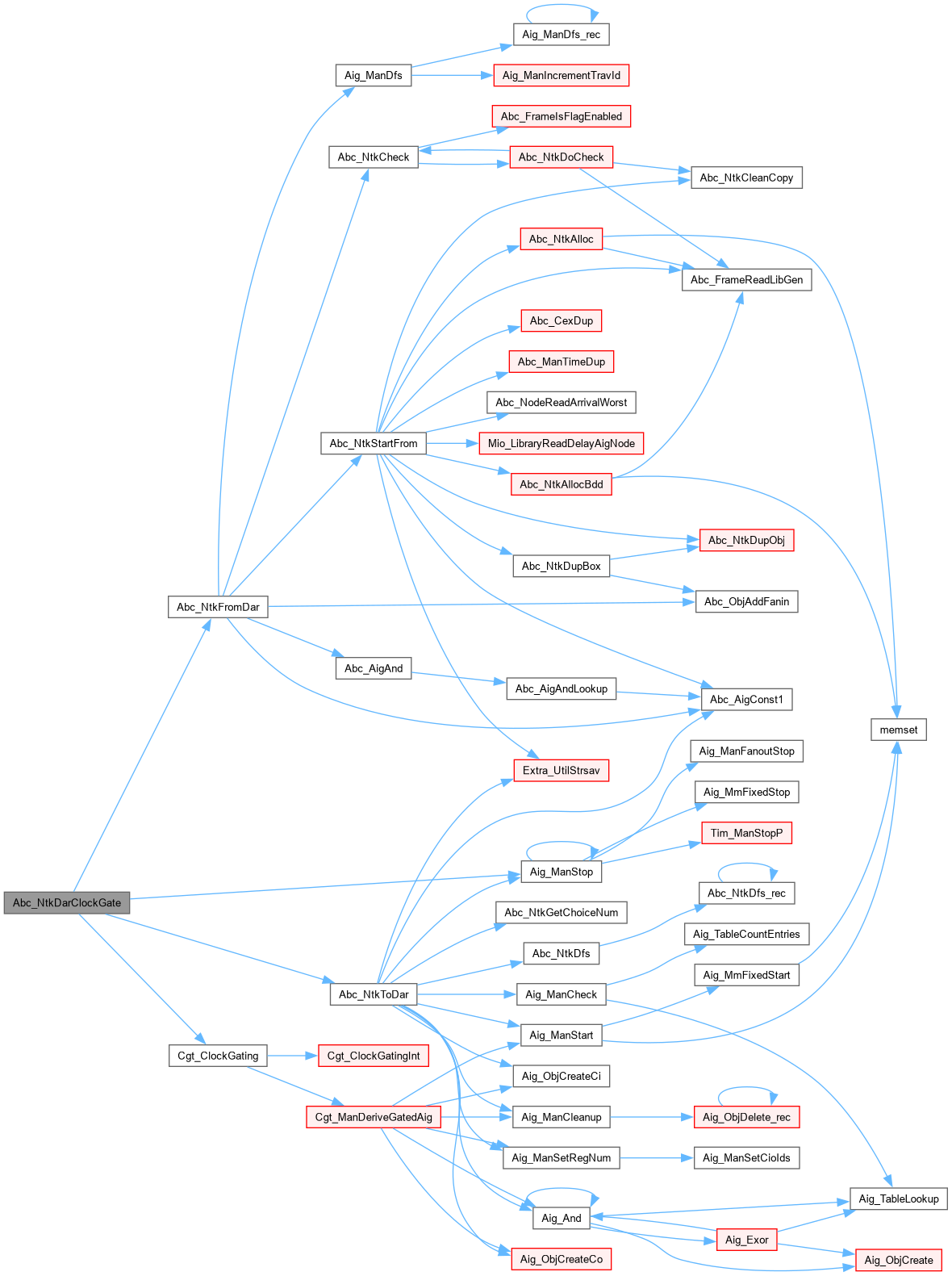

| Abc_Ntk_t * | Abc_NtkDarClockGate (Abc_Ntk_t *pNtk, Abc_Ntk_t *pCare, Cgt_Par_t *pPars) |

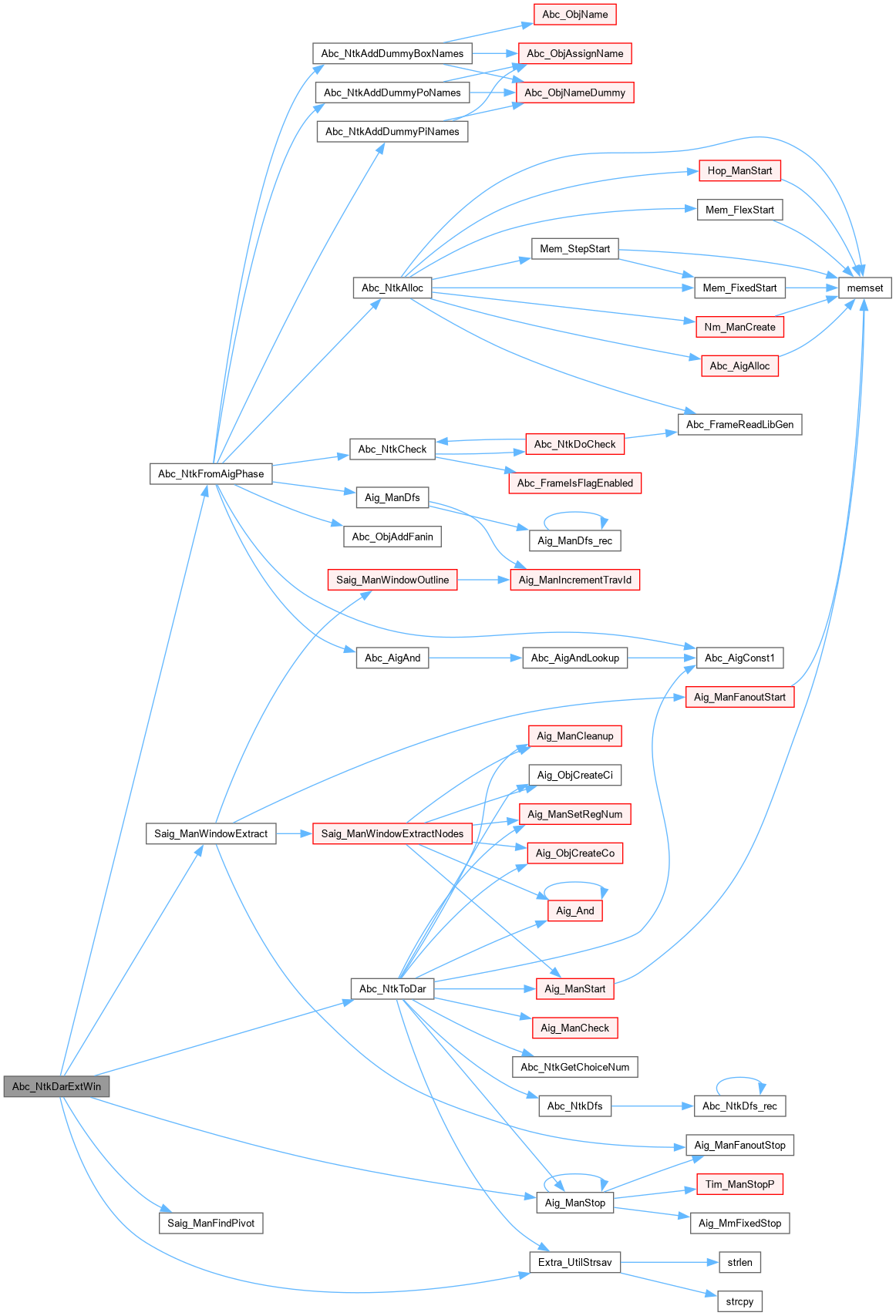

| Abc_Ntk_t * | Abc_NtkDarExtWin (Abc_Ntk_t *pNtk, int nObjId, int nDist, int fVerbose) |

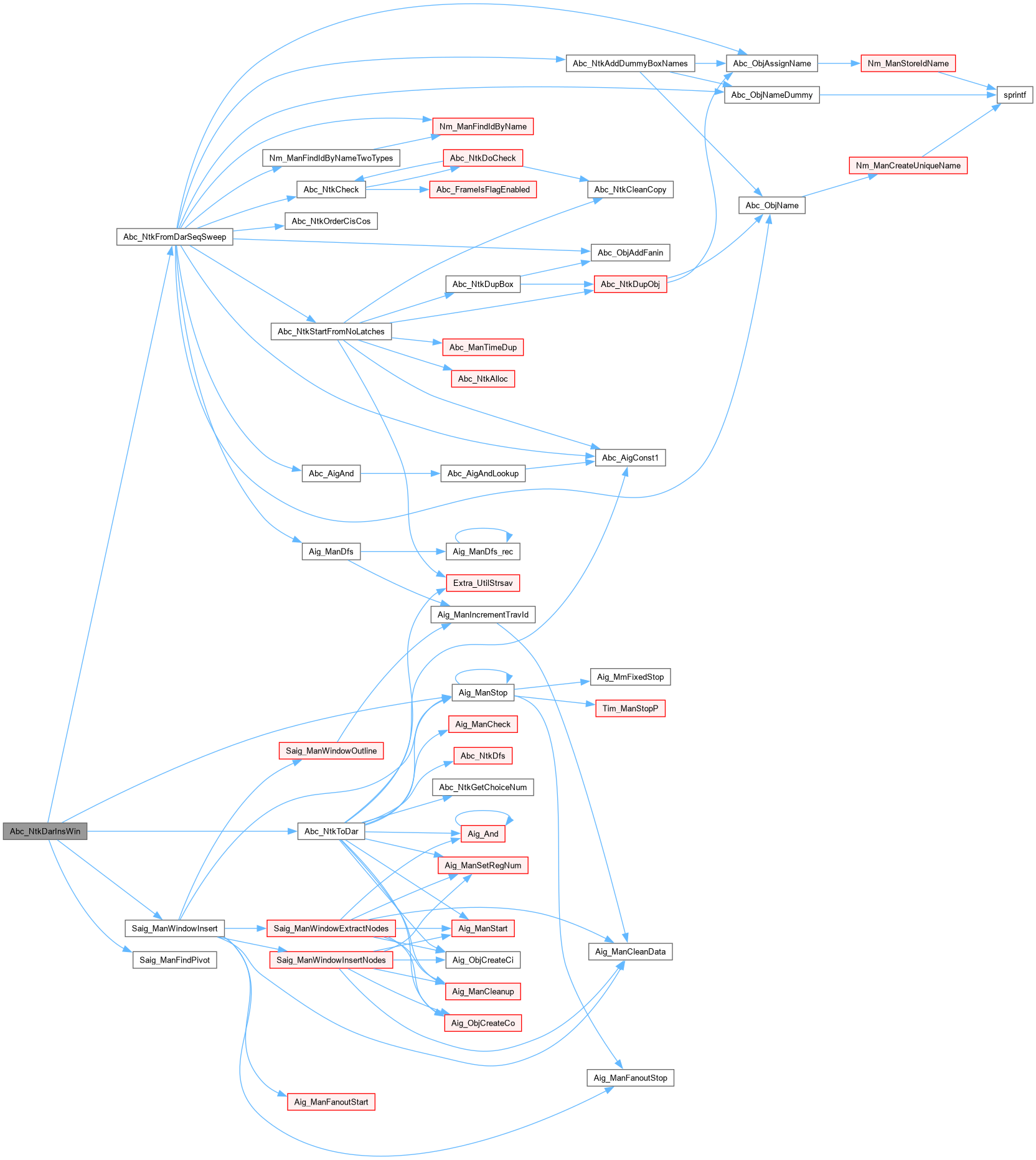

| Abc_Ntk_t * | Abc_NtkDarInsWin (Abc_Ntk_t *pNtk, Abc_Ntk_t *pCare, int nObjId, int nDist, int fVerbose) |

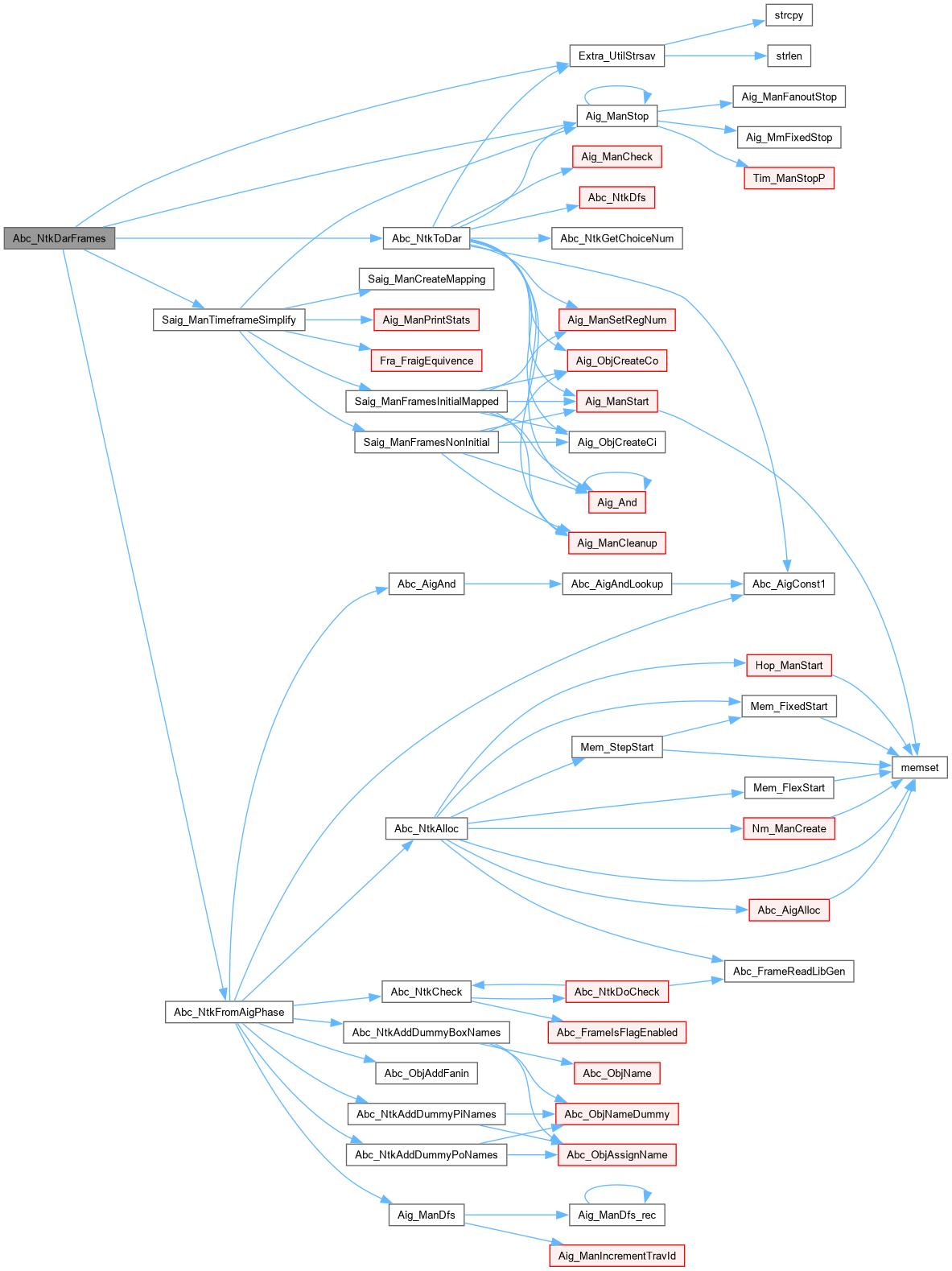

| Abc_Ntk_t * | Abc_NtkDarFrames (Abc_Ntk_t *pNtk, int nPrefix, int nFrames, int fInit, int fVerbose) |

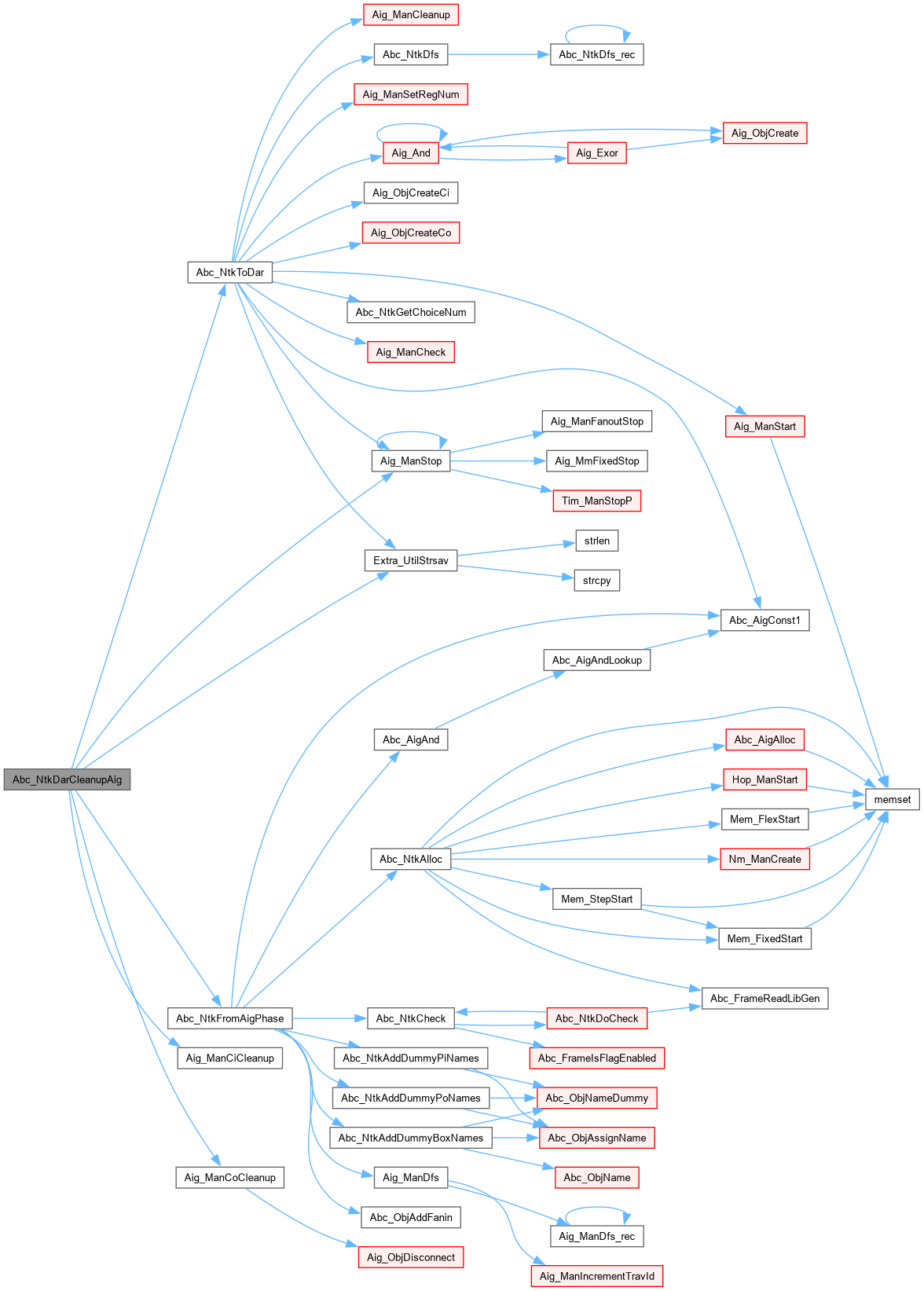

| Abc_Ntk_t * | Abc_NtkDarCleanupAig (Abc_Ntk_t *pNtk, int fCleanupPis, int fCleanupPos, int fVerbose) |

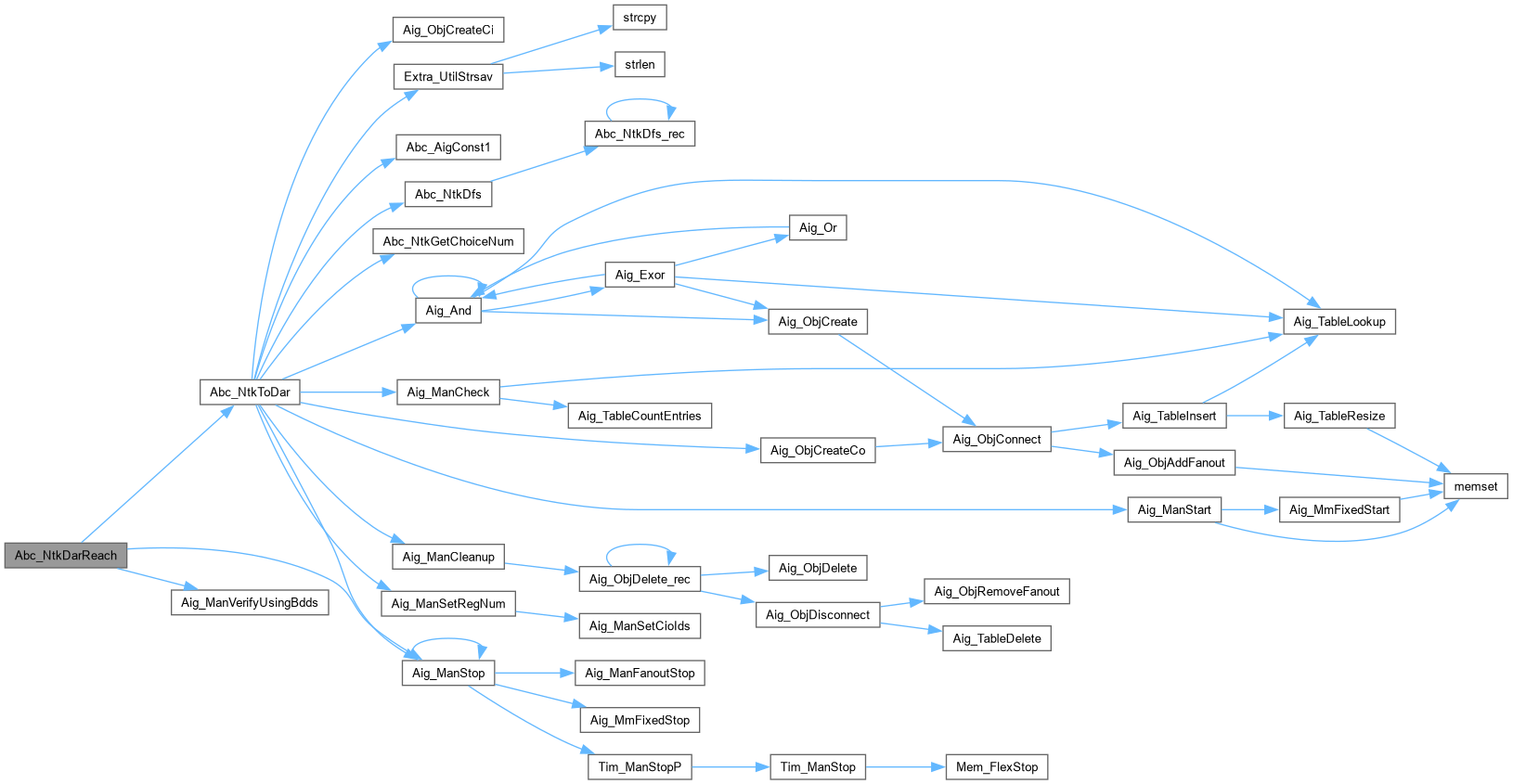

| int | Abc_NtkDarReach (Abc_Ntk_t *pNtk, Saig_ParBbr_t *pPars) |

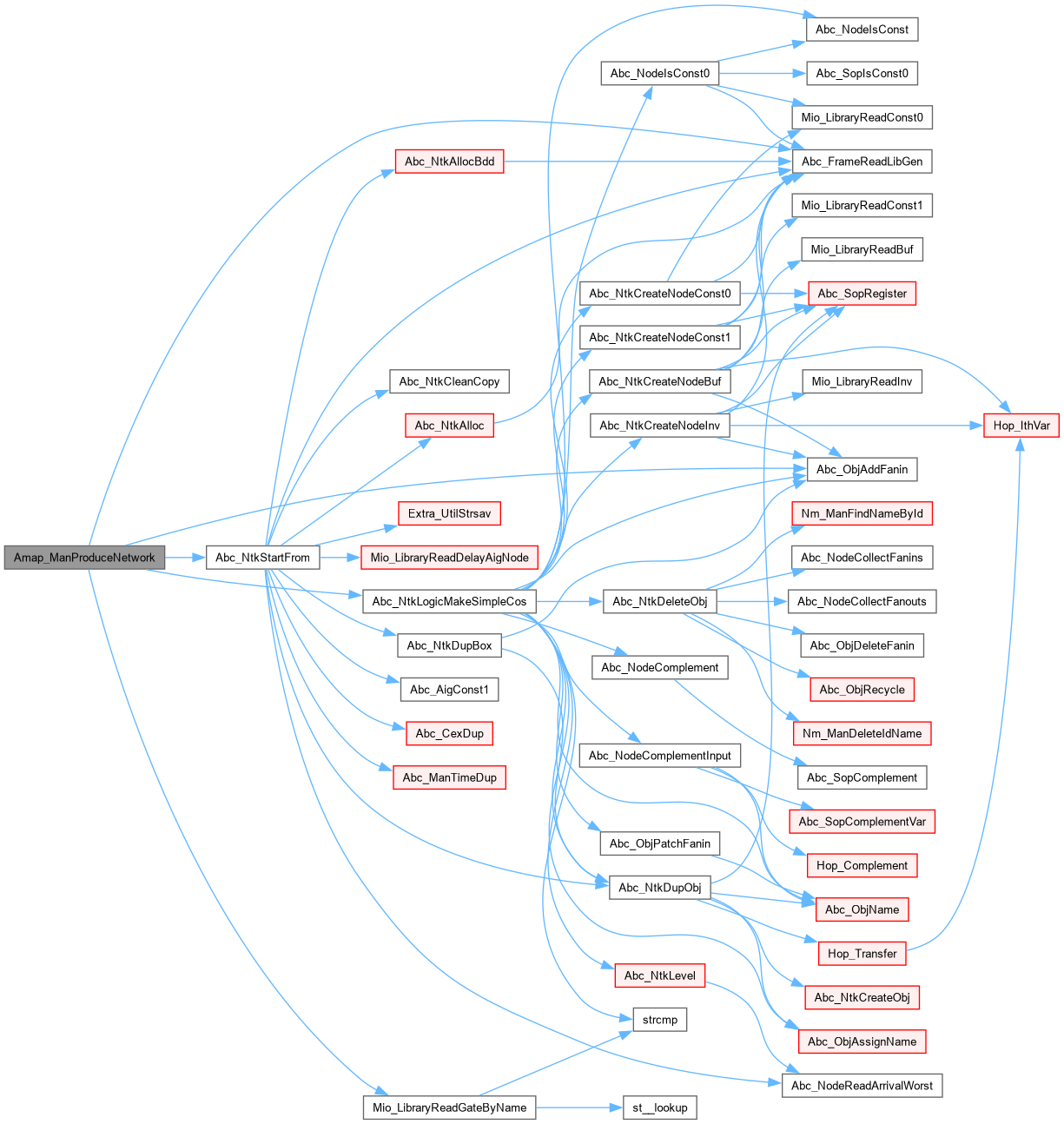

| ABC_NAMESPACE_IMPL_END ABC_NAMESPACE_IMPL_START Abc_Ntk_t * | Amap_ManProduceNetwork (Abc_Ntk_t *pNtk, Vec_Ptr_t *vMapping) |

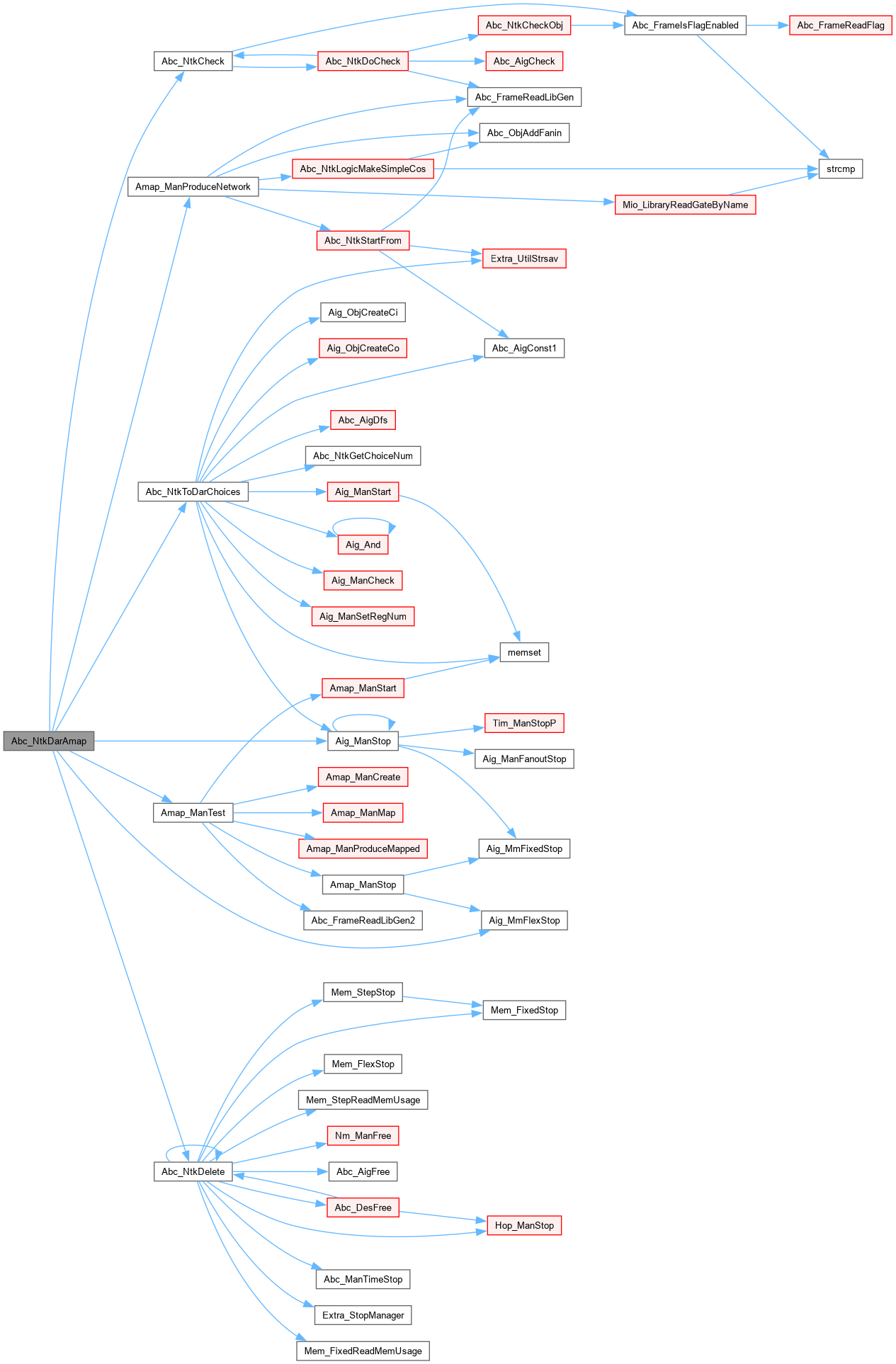

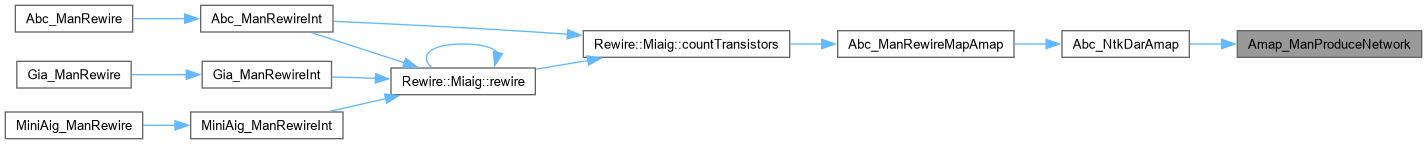

| Abc_Ntk_t * | Abc_NtkDarAmap (Abc_Ntk_t *pNtk, Amap_Par_t *pPars) |

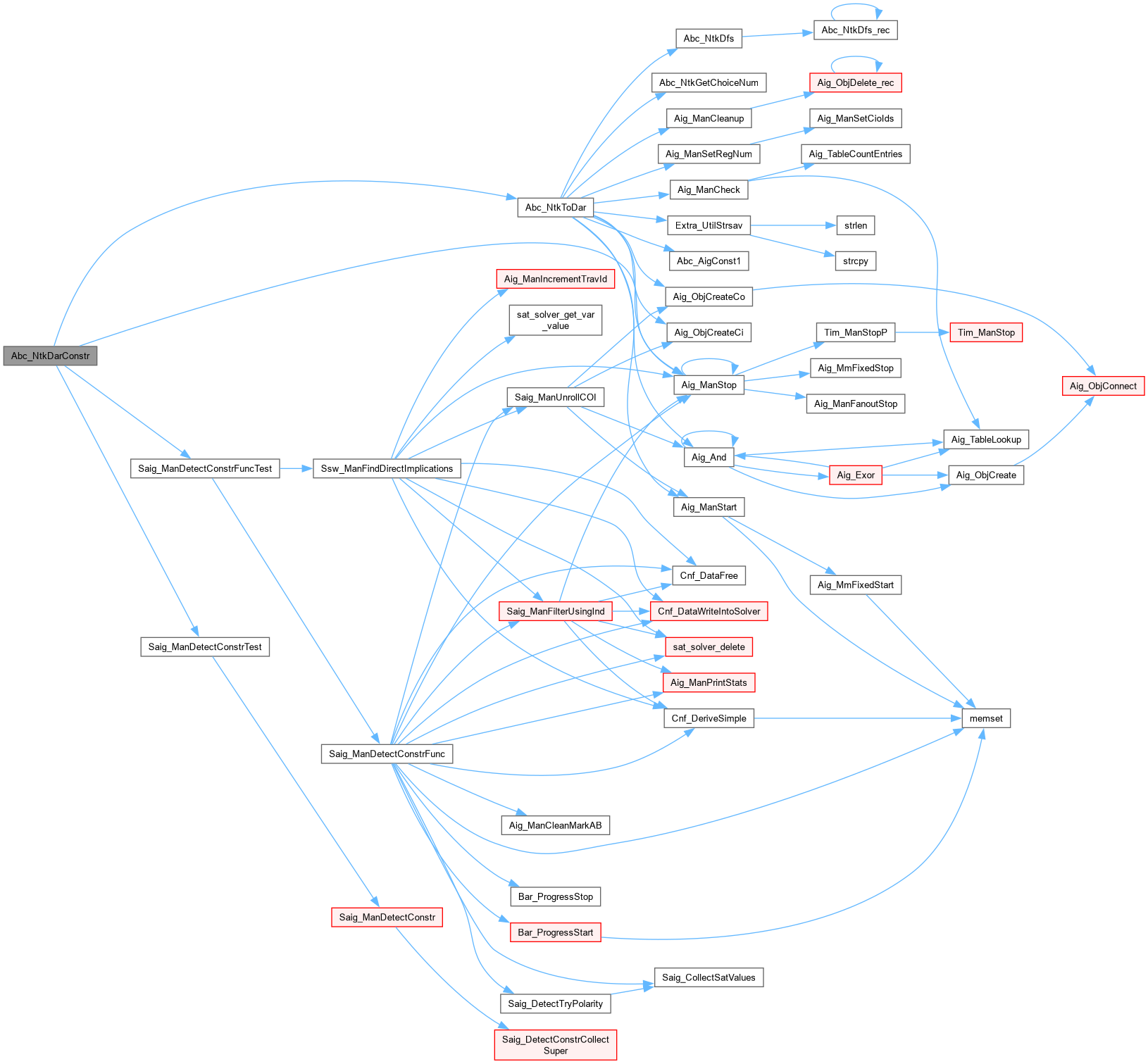

| void | Abc_NtkDarConstr (Abc_Ntk_t *pNtk, int nFrames, int nConfs, int nProps, int fStruct, int fOldAlgo, int fVerbose) |

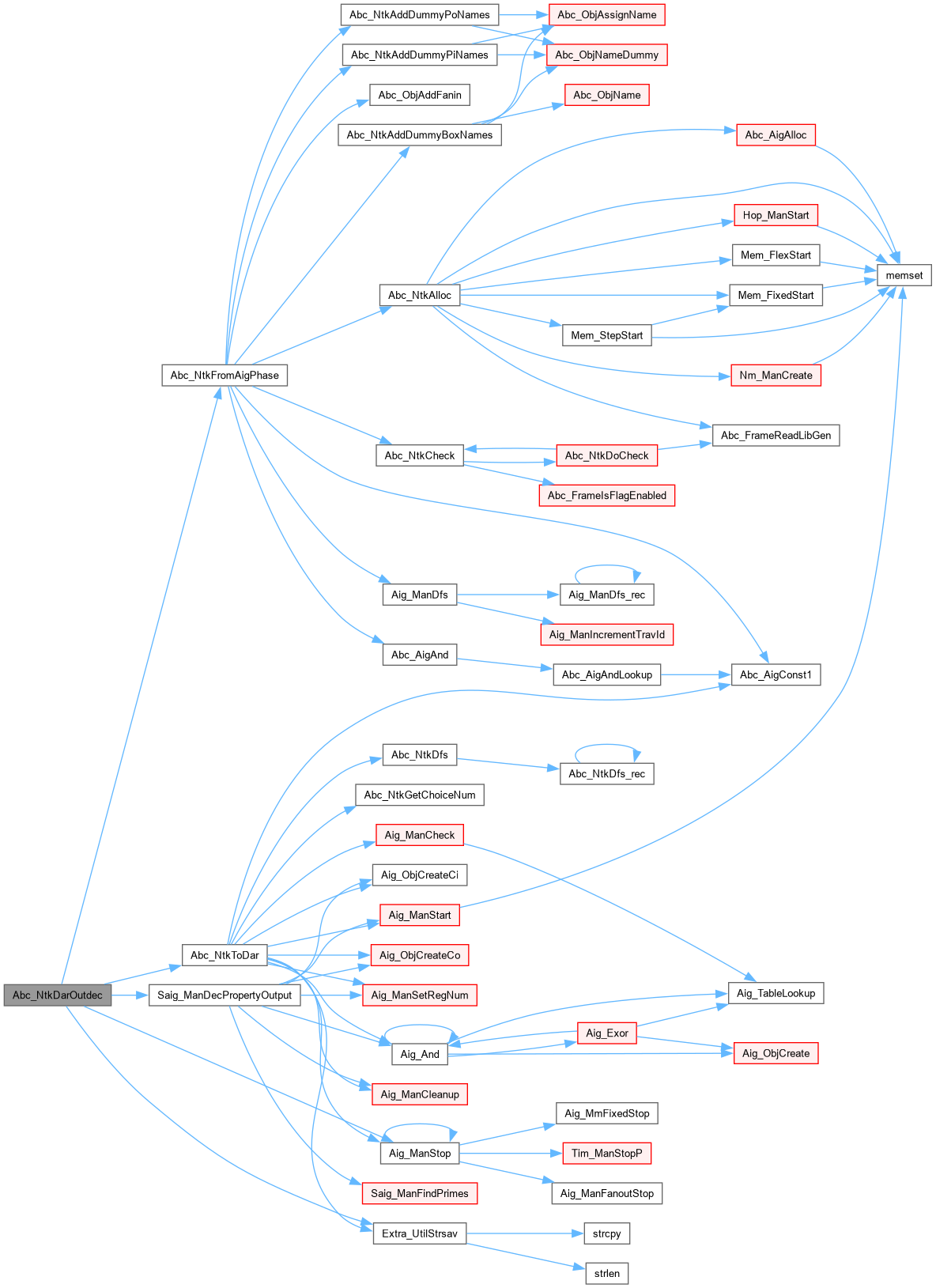

| Abc_Ntk_t * | Abc_NtkDarOutdec (Abc_Ntk_t *pNtk, int nLits, int fVerbose) |

| Abc_Ntk_t * | Abc_NtkDarUnfold (Abc_Ntk_t *pNtk, int nFrames, int nConfs, int nProps, int fStruct, int fOldAlgo, int fVerbose) |

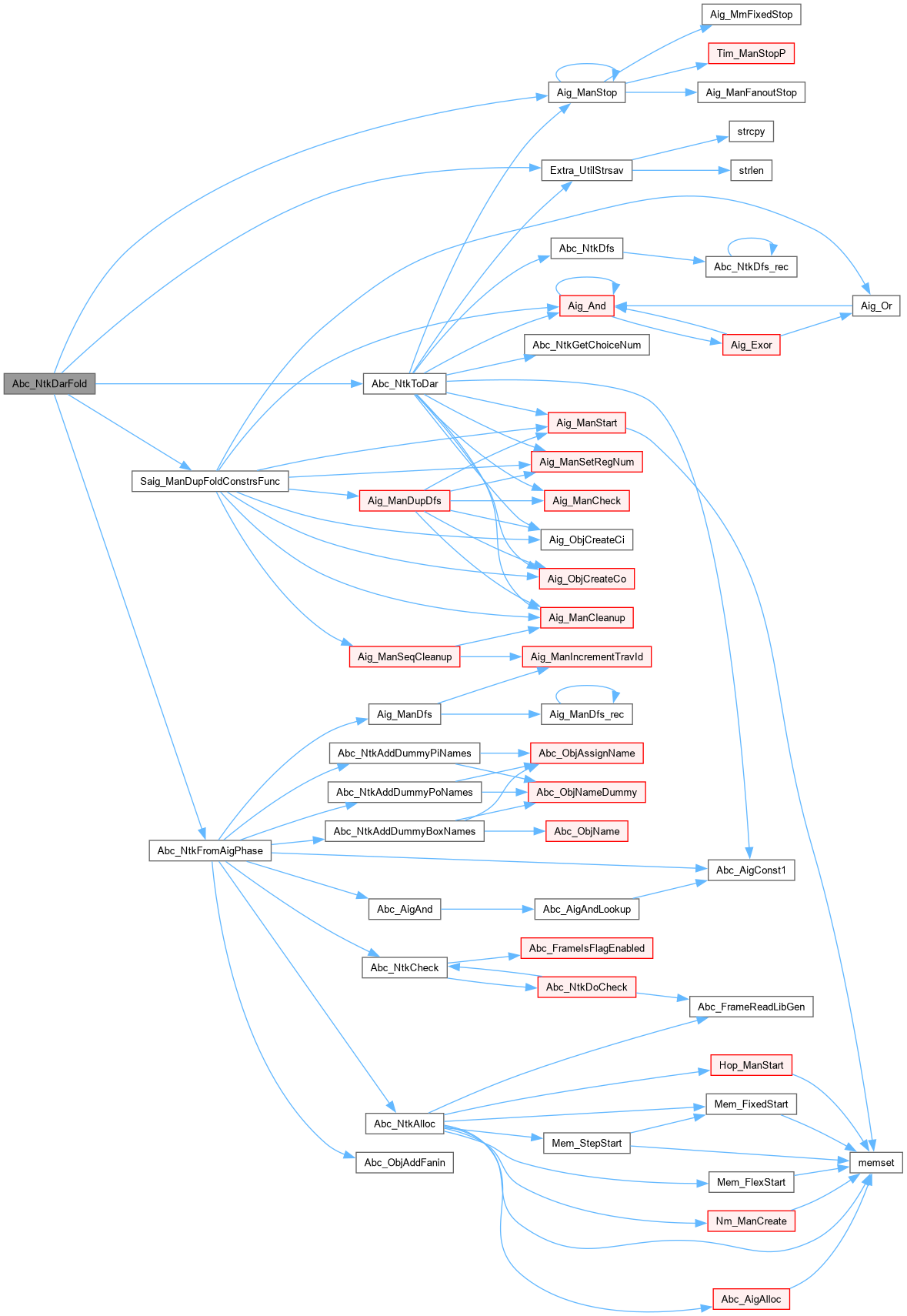

| Abc_Ntk_t * | Abc_NtkDarFold (Abc_Ntk_t *pNtk, int fCompl, int fVerbose, int fSeqCleanup) |

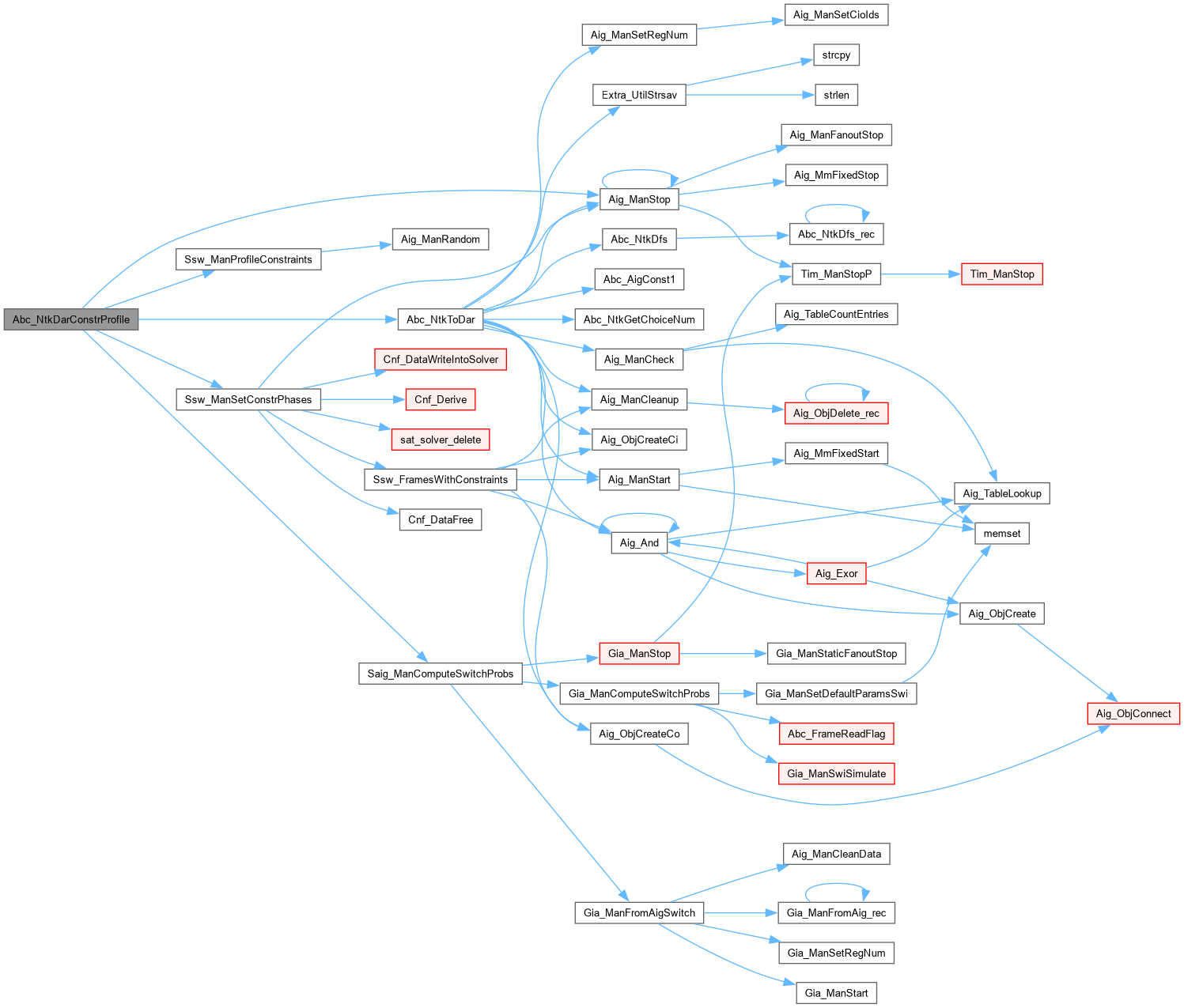

| void | Abc_NtkDarConstrProfile (Abc_Ntk_t *pNtk, int fVerbose) |

| void | Abc_NtkDarTest (Abc_Ntk_t *pNtk, int Num) |

| Abc_Ntk_t * | Abc_NtkDarTestNtk (Abc_Ntk_t *pNtk) |

Variables | |

| abctime | timeCnf |

| DECLARATIONS ///. | |

| abctime | timeSat |

| abctime | timeInt |

Definition at line 92 of file abcDar.c.

Function*************************************************************

Synopsis [Collects the supergate.]

Description []

SideEffects []

SeeAlso []

Definition at line 81 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [This procedure should be called after seq sweeping, which changes the number of registers.]

SideEffects []

SeeAlso []

Definition at line 1120 of file abcDar.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 4078 of file abcDar.c.

Function*************************************************************

Synopsis [Collects CI of the network.]

Description []

SideEffects []

SeeAlso []

Definition at line 1348 of file abcDar.c.

Function*************************************************************

Synopsis [Collects CO of the network.]

Description []

SideEffects []

SeeAlso []

Definition at line 1370 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1775 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1523 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1423 of file abcDar.c.

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 3157 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarAmap | ( | Abc_Ntk_t * | pNtk, |

| Amap_Par_t * | pPars ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 4558 of file abcDar.c.

| int Abc_NtkDarBmc | ( | Abc_Ntk_t * | pNtk, |

| int | nStart, | ||

| int | nFrames, | ||

| int | nSizeMax, | ||

| int | nNodeDelta, | ||

| int | nTimeOut, | ||

| int | nBTLimit, | ||

| int | nBTLimitAll, | ||

| int | fRewrite, | ||

| int | fNewAlgo, | ||

| int | fOrDecomp, | ||

| int | nCofFanLit, | ||

| int | fVerbose, | ||

| int * | piFrames, | ||

| int | fUseSatoko ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2367 of file abcDar.c.

| int Abc_NtkDarBmc3 | ( | Abc_Ntk_t * | pNtk, |

| Saig_ParBmc_t * | pPars, | ||

| int | fOrDecomp ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 2449 of file abcDar.c.

| int Abc_NtkDarBmcInter | ( | Abc_Ntk_t * | pNtk, |

| Inter_ManParams_t * | pPars, | ||

| Abc_Ntk_t ** | ppNtkRes ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2664 of file abcDar.c.

| int Abc_NtkDarBmcInter_int | ( | Aig_Man_t * | pMan, |

| Inter_ManParams_t * | pPars, | ||

| Aig_Man_t ** | ppNtkRes ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2555 of file abcDar.c.

| int Abc_NtkDarCec | ( | Abc_Ntk_t * | pNtk1, |

| Abc_Ntk_t * | pNtk2, | ||

| int | nConfLimit, | ||

| int | fPartition, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1965 of file abcDar.c.

| int Abc_NtkDarClau | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | nPref, | ||

| int | nClauses, | ||

| int | nLutSize, | ||

| int | nLevels, | ||

| int | nCutsMax, | ||

| int | nBatches, | ||

| int | fStepUp, | ||

| int | fBmc, | ||

| int | fRefs, | ||

| int | fTarget, | ||

| int | fVerbose, | ||

| int | fVeryVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3707 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarCleanupAig | ( | Abc_Ntk_t * | pNtk, |

| int | fCleanupPis, | ||

| int | fCleanupPos, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4427 of file abcDar.c.

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4237 of file abcDar.c.

| void Abc_NtkDarConstr | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | nConfs, | ||

| int | nProps, | ||

| int | fStruct, | ||

| int | fOldAlgo, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4603 of file abcDar.c.

| void Abc_NtkDarConstrProfile | ( | Abc_Ntk_t * | pNtk, |

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4719 of file abcDar.c.

| int Abc_NtkDarDemiter | ( | Abc_Ntk_t * | pNtk | ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2705 of file abcDar.c.

| int Abc_NtkDarDemiterDual | ( | Abc_Ntk_t * | pNtk, |

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2809 of file abcDar.c.

| int Abc_NtkDarDemiterNew | ( | Abc_Ntk_t * | pNtk | ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2756 of file abcDar.c.

Function*************************************************************

Synopsis [Performs targe enlargement.]

Description []

SideEffects []

SeeAlso []

Definition at line 3742 of file abcDar.c.

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4275 of file abcDar.c.

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4691 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarFraig | ( | Abc_Ntk_t * | pNtk, |

| int | nConfLimit, | ||

| int | fDoSparse, | ||

| int | fProve, | ||

| int | fTransfer, | ||

| int | fSpeculate, | ||

| int | fChoicing, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1462 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarFraigPart | ( | Abc_Ntk_t * | pNtk, |

| int | nPartSize, | ||

| int | nConfLimit, | ||

| int | nLevelMax, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1498 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarFrames | ( | Abc_Ntk_t * | pNtk, |

| int | nPrefix, | ||

| int | nFrames, | ||

| int | fInit, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4398 of file abcDar.c.

| int Abc_NtkDarInduction | ( | Abc_Ntk_t * | pNtk, |

| int | nTimeOut, | ||

| int | nFramesMax, | ||

| int | nConfMax, | ||

| int | fUnique, | ||

| int | fUniqueAll, | ||

| int | fGetCex, | ||

| int | fVerbose, | ||

| int | fVeryVerbose ) |

Function*************************************************************

Synopsis [Performs induction for property only.]

Description []

SideEffects []

SeeAlso []

Definition at line 3795 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarInsWin | ( | Abc_Ntk_t * | pNtk, |

| Abc_Ntk_t * | pCare, | ||

| int | nObjId, | ||

| int | nDist, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4332 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarLatchSweep | ( | Abc_Ntk_t * | pNtk, |

| int | fLatchConst, | ||

| int | fLatchEqual, | ||

| int | fSaveNames, | ||

| int | fUseMvSweep, | ||

| int | nFramesSymb, | ||

| int | nFramesSatur, | ||

| int | fVerbose, | ||

| int | fVeryVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3317 of file abcDar.c.

Function*************************************************************

Synopsis [Computes latch correspondence.]

Description []

SideEffects []

SeeAlso []

Definition at line 2274 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarLcorrNew | ( | Abc_Ntk_t * | pNtk, |

| int | nVarsMax, | ||

| int | nConfMax, | ||

| int | nLimitMax, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Computes latch correspondence.]

Description []

SideEffects []

SeeAlso []

Definition at line 2311 of file abcDar.c.

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 3265 of file abcDar.c.

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4628 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3079 of file abcDar.c.

| int Abc_NtkDarPrintCone | ( | Abc_Ntk_t * | pNtk | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 4054 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2879 of file abcDar.c.

| int Abc_NtkDarReach | ( | Abc_Ntk_t * | pNtk, |

| Saig_ParBbr_t * | pPars ) |

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4464 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3359 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3393 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarRetimeMinArea | ( | Abc_Ntk_t * | pNtk, |

| int | nMaxIters, | ||

| int | fForwardOnly, | ||

| int | fBackwardOnly, | ||

| int | fInitial, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3463 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3427 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3494 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2991 of file abcDar.c.

| int Abc_NtkDarSeqSim | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | nWords, | ||

| int | TimeOut, | ||

| int | fNew, | ||

| int | fMiter, | ||

| int | fVerbose, | ||

| char * | pFileSim ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso [] Function*************************************************************

Synopsis [Performs random simulation.]

Description []

SideEffects []

SeeAlso []

Definition at line 3558 of file abcDar.c.

| int Abc_NtkDarSeqSim3 | ( | Abc_Ntk_t * | pNtk, |

| Ssw_RarPars_t * | pPars ) |

Function*************************************************************

Synopsis [Performs random simulation.]

Description []

SideEffects []

SeeAlso []

Definition at line 3656 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2082 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarSeqSweep2 | ( | Abc_Ntk_t * | pNtk, |

| Ssw_Pars_t * | pPars ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 2231 of file abcDar.c.

| int Abc_NtkDarSimSec | ( | Abc_Ntk_t * | pNtk1, |

| Abc_Ntk_t * | pNtk2, | ||

| Ssw_Pars_t * | pPars ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 3222 of file abcDar.c.

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4200 of file abcDar.c.

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4172 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarTempor | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | TimeOut, | ||

| int | nConfLimit, | ||

| int | fUseBmc, | ||

| int | fUseTransSigs, | ||

| int | fVerbose, | ||

| int | fVeryVerbose ) |

Function*************************************************************

Synopsis [Performs targe enlargement.]

Description []

SideEffects []

SeeAlso []

Definition at line 3767 of file abcDar.c.

| void Abc_NtkDarTest | ( | Abc_Ntk_t * | pNtk, |

| int | Num ) |

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4769 of file abcDar.c.

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4856 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarToCnf | ( | Abc_Ntk_t * | pNtk, |

| char * | pFileName, | ||

| int | fFastAlgo, | ||

| int | fChangePol, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1847 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDarUnfold | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | nConfs, | ||

| int | nProps, | ||

| int | fStruct, | ||

| int | fOldAlgo, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs BDD-based reachability analysis.]

Description []

SideEffects []

SeeAlso []

Definition at line 4658 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDC2 | ( | Abc_Ntk_t * | pNtk, |

| int | fBalance, | ||

| int | fUpdateLevel, | ||

| int | fFanout, | ||

| int | fPower, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1630 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDch | ( | Abc_Ntk_t * | pNtk, |

| Dch_Pars_t * | pPars ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1689 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDChoice | ( | Abc_Ntk_t * | pNtk, |

| int | fBalance, | ||

| int | fUpdateLevel, | ||

| int | fConstruct, | ||

| int | nConfMax, | ||

| int | nLevelMax, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1663 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDRefactor | ( | Abc_Ntk_t * | pNtk, |

| Dar_RefPar_t * | pPars ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1593 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkDRewrite | ( | Abc_Ntk_t * | pNtk, |

| Dar_RwrPar_t * | pPars ) |

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1549 of file abcDar.c.

Function*************************************************************

Synopsis [Gives the current ABC network to AIG manager for processing.]

Description []

SideEffects []

SeeAlso []

Definition at line 1742 of file abcDar.c.

| int Abc_NtkDSat | ( | Abc_Ntk_t * | pNtk, |

| ABC_INT64_T | nConfLimit, | ||

| ABC_INT64_T | nInsLimit, | ||

| int | nLearnedStart, | ||

| int | nLearnedDelta, | ||

| int | nLearnedPerce, | ||

| int | fAlignPol, | ||

| int | fAndOuts, | ||

| int | fNewSolver, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Solves combinational miter using a SAT solver.]

Description []

SideEffects []

SeeAlso []

Definition at line 1915 of file abcDar.c.

Function*************************************************************

Synopsis [Collects information about what flops have unknown values.]

Description []

SideEffects []

SeeAlso []

Definition at line 211 of file abcDar.c.

DECLARATIONS ///.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [This procedure should be called after seq sweeping, which changes the number of registers.]

SideEffects []

SeeAlso []

Definition at line 595 of file abcDar.c.

Definition at line 967 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description []

SideEffects []

SeeAlso []

Definition at line 419 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description []

SideEffects []

SeeAlso []

Definition at line 1208 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description []

SideEffects []

SeeAlso []

Definition at line 1274 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [This procedure should be called after seq sweeping, which changes the number of registers.]

SideEffects []

SeeAlso []

Definition at line 473 of file abcDar.c.

| int Abc_NtkFromGiaCollapse | ( | Gia_Man_t * | pGia | ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 676 of file abcDar.c.

Definition at line 768 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the mapped GIA manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 746 of file abcDar.c.

Function*************************************************************

Synopsis [Collect latch values.]

Description []

SideEffects []

SeeAlso []

Definition at line 1392 of file abcDar.c.

Function*************************************************************

Synopsis [Interplates two networks.]

Description []

SideEffects []

SeeAlso []

Definition at line 3956 of file abcDar.c.

Function*************************************************************

Synopsis [Fast interpolation.]

Description []

SideEffects []

SeeAlso []

Definition at line 3925 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkInterOne | ( | Abc_Ntk_t * | pNtkOn, |

| Abc_Ntk_t * | pNtkOff, | ||

| int | fRelation, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Interplates two networks.]

Description []

SideEffects []

SeeAlso []

Definition at line 3841 of file abcDar.c.

| int Abc_NtkPartitionedSat | ( | Abc_Ntk_t * | pNtk, |

| int | nAlgo, | ||

| int | nPartSize, | ||

| int | nConfPart, | ||

| int | nConfTotal, | ||

| int | fAlignPol, | ||

| int | fSynthesize, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Solves combinational miter using a SAT solver.]

Description []

SideEffects []

SeeAlso []

Definition at line 1940 of file abcDar.c.

| Abc_Ntk_t * Abc_NtkPhaseAbstract | ( | Abc_Ntk_t * | pNtk, |

| int | nFrames, | ||

| int | nPref, | ||

| int | fIgnore, | ||

| int | fPrint, | ||

| int | fVerbose ) |

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4112 of file abcDar.c.

| int Abc_NtkPhaseFrameNum | ( | Abc_Ntk_t * | pNtk | ) |

Function*************************************************************

Synopsis [Performs phase abstraction.]

Description []

SideEffects []

SeeAlso []

Definition at line 4145 of file abcDar.c.

Function*************************************************************

Synopsis [Print Latch Equivalence Classes.]

Description []

SideEffects []

SeeAlso []

Definition at line 2141 of file abcDar.c.

| void Abc_NtkPrintSccs | ( | Abc_Ntk_t * | pNtk, |

| int | fVerbose ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 4031 of file abcDar.c.

DECLARATIONS ///.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [Assumes that registers are ordered after PIs/POs.]

SideEffects []

SeeAlso []

Definition at line 237 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [The returned map maps new PO IDs into old ones.]

SideEffects []

SeeAlso []

Definition at line 115 of file abcDar.c.

Function*************************************************************

Synopsis [Converts the network from the AIG manager into ABC.]

Description [Assumes that registers are ordered after PIs/POs.]

SideEffects []

SeeAlso []

Definition at line 359 of file abcDar.c.

| ABC_NAMESPACE_IMPL_START int Abc_ObjCompareById | ( | Abc_Obj_t ** | pp1, |

| Abc_Obj_t ** | pp2 ) |

DECLARATIONS ///.

CFile****************************************************************

FileName [abcDar.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [DAG-aware rewriting.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 65 of file abcDar.c.

| Hop_Obj_t * Abc_ObjHopFromGia | ( | Hop_Man_t * | pHopMan, |

| Gia_Man_t * | p, | ||

| int | GiaId, | ||

| Vec_Ptr_t * | vCopies ) |

Definition at line 721 of file abcDar.c.

| Hop_Obj_t * Abc_ObjHopFromGia_rec | ( | Hop_Man_t * | pHopMan, |

| Gia_Man_t * | p, | ||

| int | Id, | ||

| Vec_Ptr_t * | vCopies ) |

Function*************************************************************

Synopsis [Creates local function of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 704 of file abcDar.c.

| ABC_NAMESPACE_IMPL_END ABC_NAMESPACE_IMPL_START Abc_Ntk_t * Amap_ManProduceNetwork | ( | Abc_Ntk_t * | pNtk, |

| Vec_Ptr_t * | vMapping ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 4498 of file abcDar.c.

Definition at line 3884 of file abcDar.c.

| abctime timeCnf |

DECLARATIONS ///.

CFile****************************************************************

FileName [aigInter.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [Interpolate two AIGs.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

]