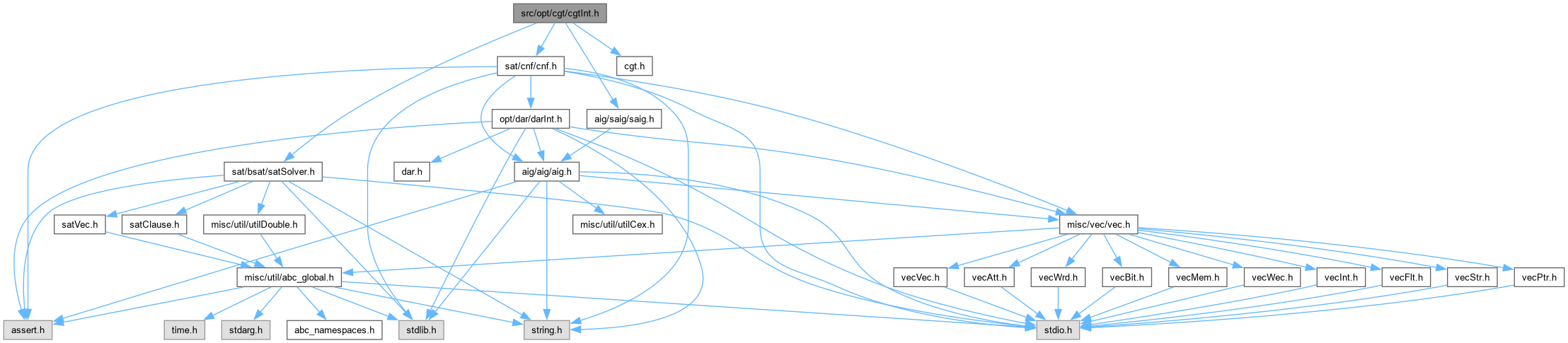

#include "aig/saig/saig.h"#include "sat/bsat/satSolver.h"#include "sat/cnf/cnf.h"#include "cgt.h"

Go to the source code of this file.

Classes | |

| struct | Cgt_Man_t_ |

Typedefs | |

| typedef typedefABC_NAMESPACE_HEADER_START struct Cgt_Man_t_ | Cgt_Man_t |

| INCLUDES ///. | |

Functions | |

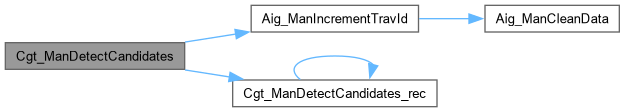

| void | Cgt_ManDetectCandidates (Aig_Man_t *pAig, Vec_Int_t *vUseful, Aig_Obj_t *pObj, int nLevelMax, Vec_Ptr_t *vCands) |

| MACRO DEFINITIONS ///. | |

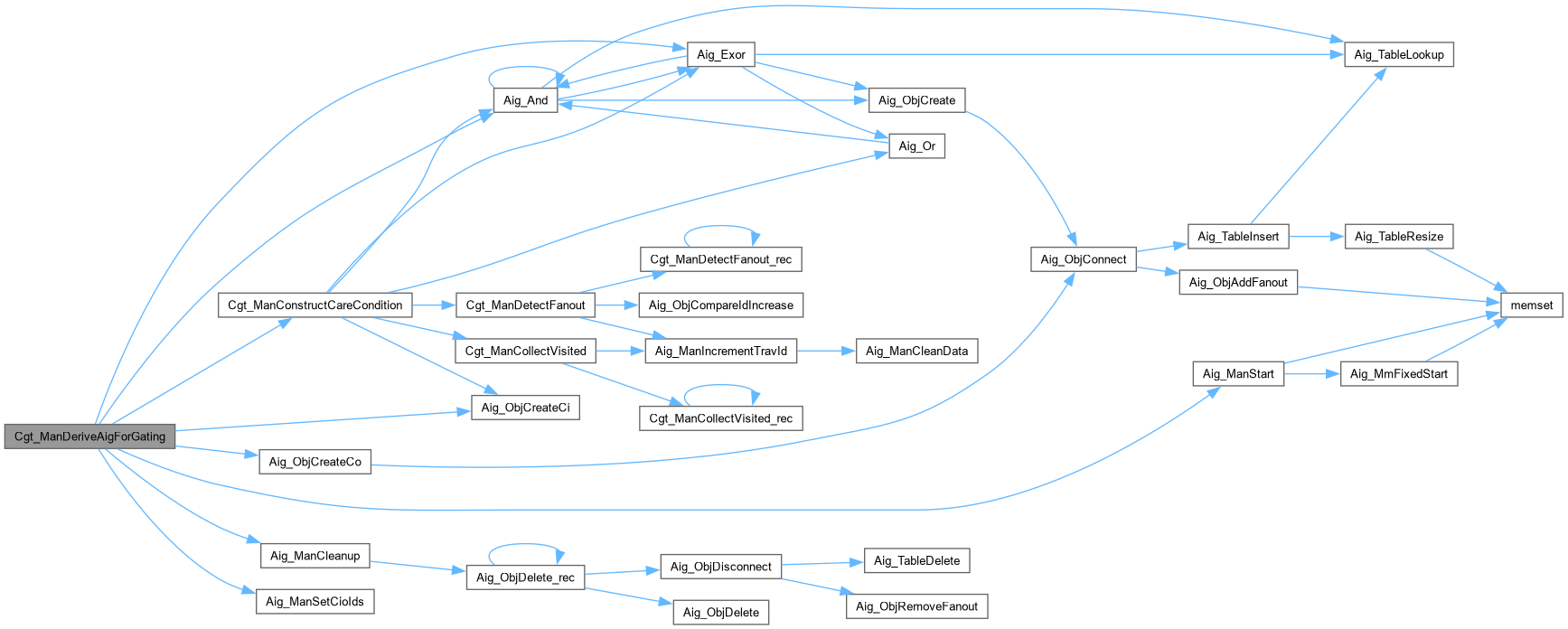

| Aig_Man_t * | Cgt_ManDeriveAigForGating (Cgt_Man_t *p) |

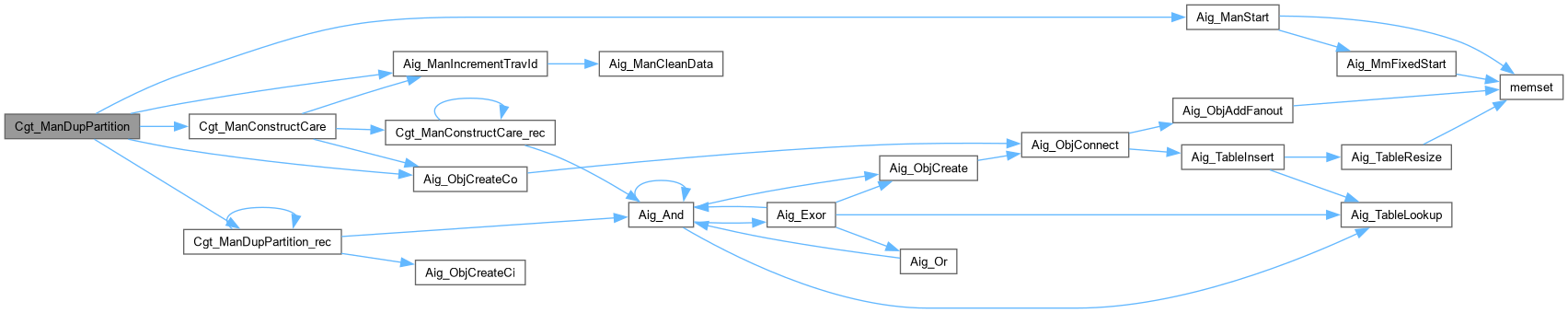

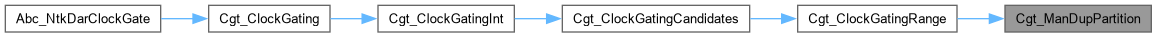

| Aig_Man_t * | Cgt_ManDupPartition (Aig_Man_t *pAig, int nVarsMin, int nFlopsMin, int iStart, Aig_Man_t *pCare, Vec_Vec_t *vSuppsInv, int *pnOutputs) |

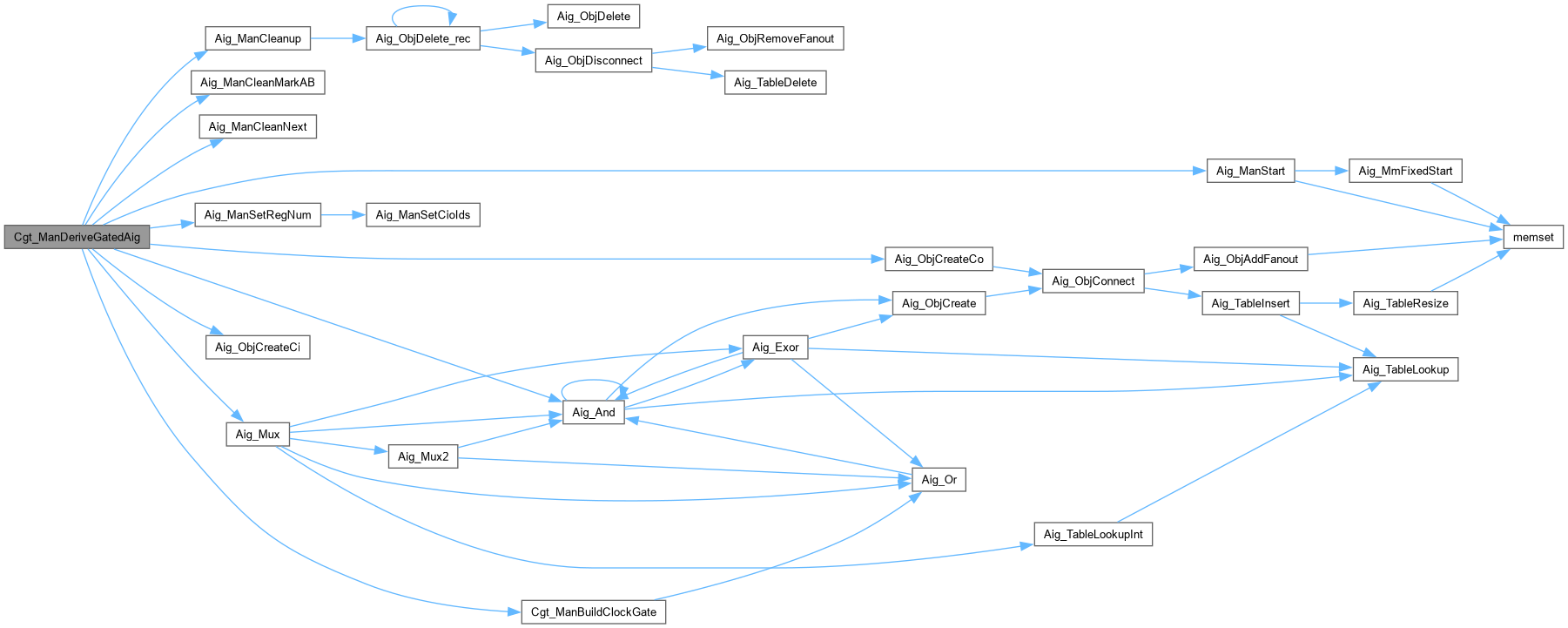

| Aig_Man_t * | Cgt_ManDeriveGatedAig (Aig_Man_t *pAig, Vec_Vec_t *vGates, int fReduce, int *pnUsedNodes) |

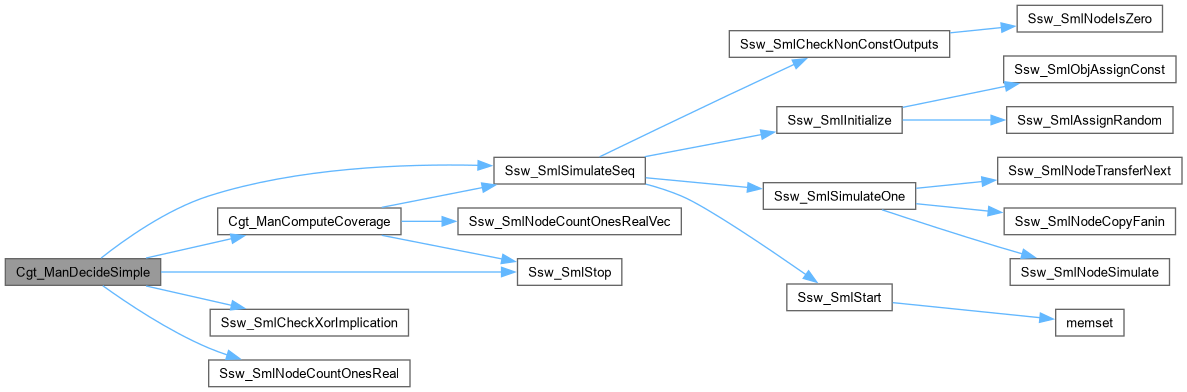

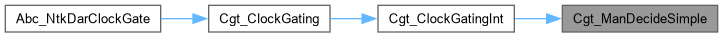

| Vec_Vec_t * | Cgt_ManDecideSimple (Aig_Man_t *pAig, Vec_Vec_t *vGatesAll, int nOdcMax, int fVerbose) |

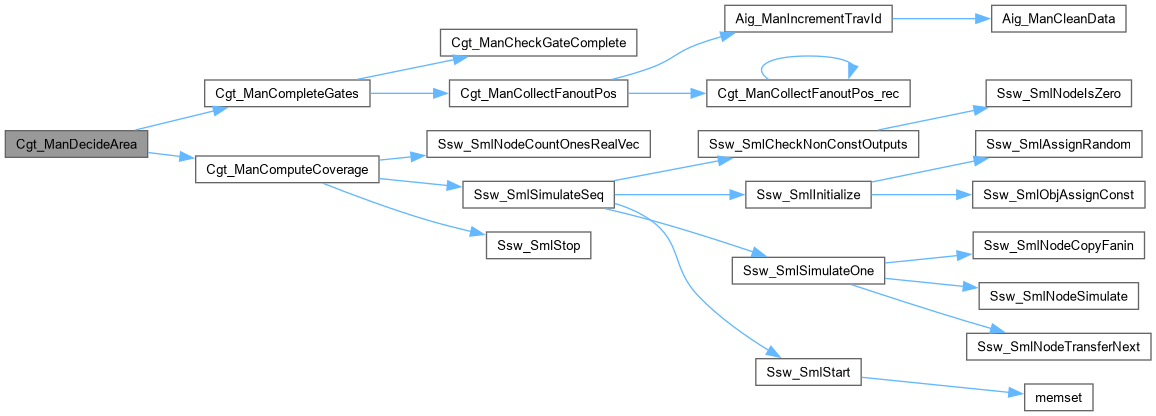

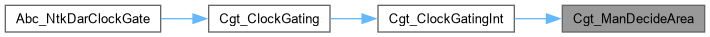

| Vec_Vec_t * | Cgt_ManDecideArea (Aig_Man_t *pAig, Vec_Vec_t *vGatesAll, int nOdcMax, int fVerbose) |

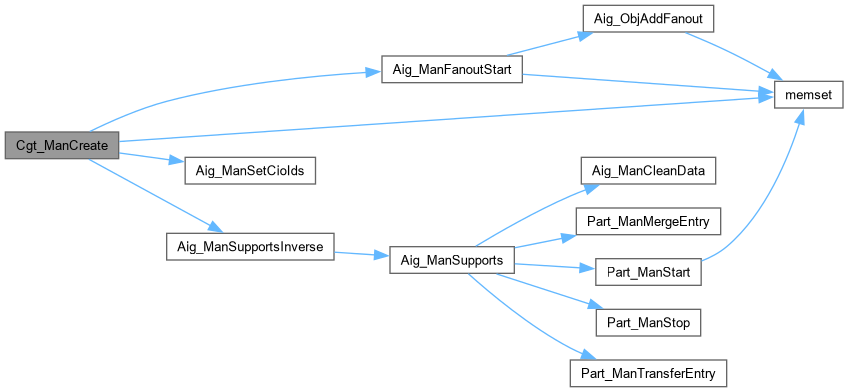

| Cgt_Man_t * | Cgt_ManCreate (Aig_Man_t *pAig, Aig_Man_t *pCare, Cgt_Par_t *pPars) |

| DECLARATIONS ///. | |

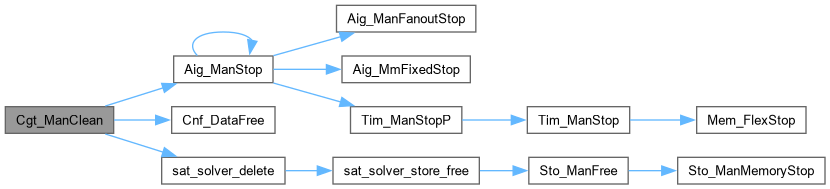

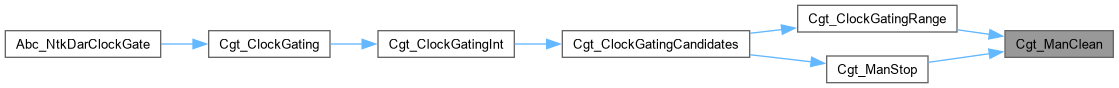

| void | Cgt_ManClean (Cgt_Man_t *p) |

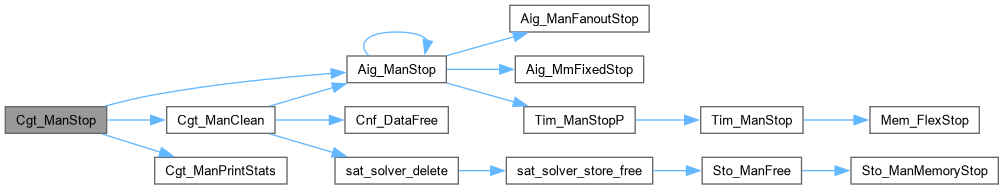

| void | Cgt_ManStop (Cgt_Man_t *p) |

| int | Cgt_CheckImplication (Cgt_Man_t *p, Aig_Obj_t *pGate, Aig_Obj_t *pFlop) |

| DECLARATIONS ///. | |

| typedef typedefABC_NAMESPACE_HEADER_START struct Cgt_Man_t_ Cgt_Man_t |

INCLUDES ///.

CFile****************************************************************

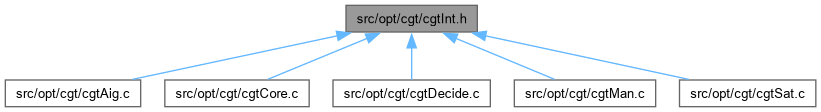

FileName [cgtInt.h]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Clock gating package.]

Synopsis [Internal declarations.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] PARAMETERS /// BASIC TYPES ///

DECLARATIONS ///.

CFile****************************************************************

FileName [cgtSat.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Clock gating package.]

Synopsis [Checking implications using SAT.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Runs equivalence test for the two nodes.]

Description [Both nodes should be regular and different from each other.]

SideEffects []

SeeAlso []

Definition at line 46 of file cgtSat.c.

|

extern |

Function*************************************************************

Synopsis [Creates the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 86 of file cgtMan.c.

DECLARATIONS ///.

CFile****************************************************************

FileName [cgtMan.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Clock gating package.]

Synopsis [Manipulation of clock gating manager.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

] FUNCTION DEFINITIONS /// Function*************************************************************

Synopsis [Creates the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 45 of file cgtMan.c.

|

extern |

Function*************************************************************

Synopsis [Computes the set of complete clock gates.]

Description []

SideEffects []

SeeAlso []

Definition at line 255 of file cgtDecide.c.

|

extern |

Function*************************************************************

Synopsis [Chooses what clock-gate to use for this register.]

Description [Currently uses the naive approach: For each register, choose the clock gate, which covers most of the transitions.]

SideEffects []

SeeAlso []

Definition at line 184 of file cgtDecide.c.

Function*************************************************************

Synopsis [Derives AIG for clock-gating.]

Description []

SideEffects []

SeeAlso []

Definition at line 266 of file cgtAig.c.

|

extern |

Function*************************************************************

Synopsis [Derives AIG after clock-gating.]

Description [The array contains, for each flop, its gate if present.]

SideEffects []

SeeAlso []

Definition at line 524 of file cgtAig.c.

|

extern |

MACRO DEFINITIONS ///.

FUNCTION DECLARATIONS ///

Function*************************************************************

Synopsis [Computes transitive fanout cone of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 70 of file cgtAig.c.

|

extern |

Function*************************************************************

Synopsis [Duplicates register outputs starting from the given one.]

Description []

SideEffects []

SeeAlso []

Definition at line 441 of file cgtAig.c.

|

extern |

Function*************************************************************

Synopsis [Frees the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 154 of file cgtMan.c.